基于硬件的安全性提供了針對網絡攻擊的強大保護,當實現加密功能的芯片使用時,物理不可克隆功能(PUF)技術可以進一步增強該級別的保護。本應用筆記討論了一種新的PUF半導體解決方案,稱為ChipDNA技術,該解決方案利用了MOSFET晶體管的隨機模擬特性,MOSFET晶體管是CMOS IC的基本構建模塊。在芯片層面,基于ChipDNA的PUF解決方案由一系列模擬電路元件構成,具有I-V特性固有的隨機性,并根據實現芯片加密要求所需的位數進行調整。需要時,ChipDNA PUF 用于導出每個芯片的隨機、唯一且可重復的二進制值,該值只能通過芯片加密塊訪問。一旦不再需要它,PUF 派生的密鑰值就會立即擦除,并且不會以數字形式存在。這種 ChipDNA PUF 解決方案已證明具有高可靠性和適當的加密質量——這兩個標準都使 PUF 輸出能夠用作加密密鑰值。本應用筆記的類似版本最初發表在《嵌入式世界2018年會議論文集》中。

介紹

密碼學提供了靈活有效的工具來應對嵌入式電子系統面臨的無數潛在安全威脅。有多種硬件和軟件方法可用于實現加密解決方案。通常理解,基于硬件的解決方案(即專用安全IC)是信任根的最有效表述,也是提供防止多種常見攻擊的對策和保護的方法。

與嵌入式系統相關的寶貴資產面臨著無情的威脅。例如,此類系統會遇到入侵,例如盜竊知識產權、引入惡意軟件來破壞或破壞設備、未經授權訪問敏感通信以及篡改從物聯網端點生成的數據。可用的安全IC和加密解決方案可以解決這些威脅。但是,安全IC本身可能成為試圖規避或破壞安全性的對手的攻擊目標。

對安全 IC 的攻擊

假設基于安全 IC 的保護解決方案,則攻擊場景分為兩類:非侵入性[1]和侵入性。

非侵入性攻擊包括操作測量,有時與其他外部應用的刺激相結合,以獲取加密密鑰或其他敏感數據。此類工作的例子包括差分或簡單的功率/電磁分析(DPA/SPA/DEMA/SEMA)或通過電壓毛刺、極端熱條件或激光和定時攻擊誘發故障狀態。雖然非侵入性攻擊威脅在技術上很難解決,但已經建立了電路和算法對策,這些電路和算法對策已被證明可以有效地保護安全IC和敏感的存儲數據免受損害。

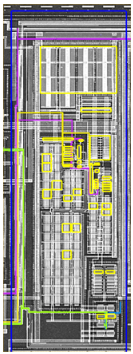

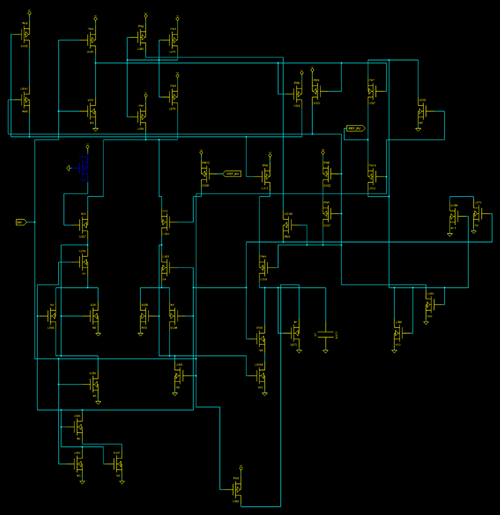

對安全IC的侵入性攻擊包括直接芯片級電路探測、修改、反處理和逆向工程,其目的同樣是通過獲取密鑰、禁用功能或將設計完全逆向工程到網表進行復制來破壞解決方案。技能集和所需工具比非侵入性場景更復雜,但它們確實存在,并且通常用于攻擊保護高價值資產的安全 IC。例如,圖1和圖2是工具的輸出示例,這些工具可用于侵入性攻擊,首先對IC的一部分進行成像,然后從成像中提取網表和原理圖。攻擊者將對整個IC重復此過程,最終目標是獲得一些見解以發起子電路攻擊或生成數據庫以復制IC

圖1.用于原理圖/網表提取的成像安全IC區域。

圖2.用于對區域進行成像的工具的邏輯示意圖輸出。

與非侵入性情況一樣,也有電路解決方案可用于對抗侵入性攻擊。一個例子包括頂級芯片屏蔽,這些屏蔽被主動監控以發生篡改事件,并結合采取防御性反擊的檢測電路。然而,采用侵入性技術的攻擊者的技能和裝備迅速發展,歷來是一個決定性擊敗的挑戰。

PUF 技術如何應對侵入性攻擊

物理不可克隆功能(PUF)技術已經出現,可提供針對入侵威脅的強大保護[2].PUF源自IC復雜多變的物理/電學特性。由于PUF依賴于隨機物理因素(不可預測和不可控制),這些因素是原生存在的和/或在制造過程中偶然引入的,因此幾乎不可能復制或克隆。PUF 技術原生為其關聯的安全 IC 生成數字指紋,該指紋可用作唯一的密鑰/機密,以支持加密算法和服務,包括加密/解密、身份驗證和數字簽名。

Maxim Integrated的PUF實現,稱為ChipDNA技術,基于基本半導體MOSFET器件模擬特性的自然隨機變化和失配。這種隨機性源于氧化物變化、閾值電壓的器件間不匹配和互連阻抗等因素。同樣,晶圓制造過程通過不完善或不均勻的沉積和蝕刻步驟引入隨機性。矛盾的是,半導體器件參數變化通常是IC設計人員在開發過程中面臨的挑戰,也是Maxim的PUF設計的基本基礎。

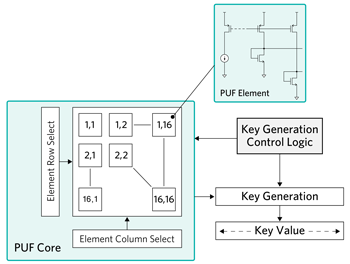

圖3是Maxim的ChipDNA PUF架構的簡化框圖,示例密鑰大小為128位。PUF 核心塊中顯示的是一個由 16 個 PUF 元件組成的 16x256 陣列,每個元件都是模擬結構。通過工廠調理,這256個元素組合成128對。在比較結構與結構時,由于前面描述的參數而存在隨機I / V特性,并且通過對中每個元件的精密電路級比較來生成二進制1/0值。例如,元素 {2,1} 和 {14,16} 可以構成一對,并且比較每個元素的 I/V 特性以得出一個位值。對 128 對中的每一對重復此操作,以生成示例密鑰大小的 128 位 PUF 密鑰輸出。對于較大的密鑰大小要求,只需縮放ChipDNA PUF元件的數量即可。

圖3.Maxim Integrated的ChipDNA PUF架構框圖。

對于侵入性攻擊,對 ChipDNA PUF 元件的任何探測或嘗試模擬測量都會導致敏感的模擬電氣特性因電容/電感/電阻負載等因素而發生變化。這就是為什么不可能通過侵入性測量提取任何關鍵數據的原因。此外,由于不完善的制造技術的統計性質,沒有已知的方法可以從檢查方法中識別任何關鍵信息。同樣,即使了解ChipDNA PUF元件配對也不會揭示任何有關最終可以從PUF元件結構的模擬特性得出的關鍵值的信息。最后,PUF 密鑰值僅在執行加密操作時以數字方式存在;此后,它會被立即擦除。這些ChipDNA PUF屬性共同產生了一種對侵入性攻擊高度免疫的解決方案。

PUF 可靠性和加密質量

從加密的角度來看,可靠性和隨機性是 PUF 解決方案必須表現出的關鍵特征。要用作加密密鑰或其根,PUF 輸出必須具有 100% 的可靠性,這意味著 PUF 派生的密鑰位值必須在一段時間內和所有操作條件下可重復。對于半導體器件,該評估使用JEDEC定義,經過行業驗證的可靠性研究方法進行。這包括選擇具有統計意義的設備樣本集并將其置于環境和操作壓力條件下,從而能夠評估使用壽命的可靠性性能。這些應力包括高溫工作壽命 (HTOL)、溫度循環、封裝和焊料回流影響、電壓和溫度漂移以及高度加速的溫度/濕度應力測試 (HAST)。使用這些經過驗證的方法進行可靠性鑒定研究,可以對設計在系統中使用期間的性能進行統計評估。例如,假設系統最終產品的設計壽命為10年,工作在-40°C至+85°C的環境中,電源可能會波動±10%。

與PUF解決方案同樣重要的是對高性能加密質量的要求,其關鍵屬性是隨機性。低質量隨機性可以通過可預測性弱點創建加密攻擊漏洞。統計測試套件(包括 NIST SP 800-22)提供了一種經過行業驗證的方法來測量 PUF 輸出的隨機性。針對測試套件的評估提供了多個指標,這些指標確定 PUF 輸出是否與隨機序列一致。為了具有統計意義,這些工具需要大型數據集進行分析(例如,20 kbit序列)。因此,大量 PUF 實例的輸出是必需的,并用于評估。

芯片DNA的可靠性研究

對Maxim的ChipDNA PUF進行終身可靠性分析的結果證明了其功能。從根本上說,可靠性研究產生了了解PUF元素的數據,例如老化,溫度/電壓漂移,IC封裝和PCB組裝的轉變。相對于兩個PUF成對元件的時間零特性,可靠性研究后的成對元件消耗了大約7%的總裕量,以保持輸出二進制值的穩定性。分析的最終輸出是 ChipDNA PUF 密鑰錯誤率 (KER) = 5ppb,其中 KER 定義為 PUF 產生的總密鑰大小中的 1 位(例如,256 位)可以翻轉產品的生命周期的概率。

ChipDNA PUF 的隨機性評估依賴于 NIST 標準 SP 800-22 單比特、撲克、運行測試和長期運行測試的性能。這些測試套件評估輸出數據是否與隨機序列一致。四個測試中每個測試的評估結果都驗證了在隨機性方面的出色表現。

為了評估Maxim ChipDNA PUF解決方案對侵入性攻擊和逆向工程的免疫力,由一家領先的美國公司[3]評估,該公司專門從事芯片級安全評估和IC逆向工程專業知識。在給定的評估時間范圍內,ChipDNA解決方案沒有受到損害,并且有一個定性的結論,即該解決方案“非常有效且能夠抵抗物理逆向工程攻擊”。

芯片DNA技術用例

ChipDNA PUF技術可以通過多種方式用于安全IC內的加密操作,例如:

在圖 4 中,為了保護安全 IC 上存儲的所有數據,ChipDNA PUF 派生密鑰用于根據需要使用 AES 等算法加密/解密數據。如果侵入性攻擊獲得了對任何非易失性存儲器 (NVM) 數據的訪問權限,則該數據將毫無用處,因為它已加密,攻擊者無法獲取基于 PUF 的解密密鑰。在本例中,數據的加密/解密僅根據需要在片上完成。PUF 密鑰加密數據不會從 IC 傳輸。

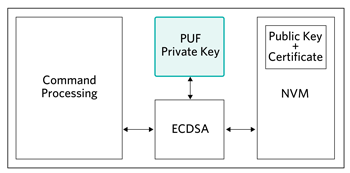

圖 5 顯示了使用 ChipDNA PUF 作為 ECDSA 簽名操作的唯一私鑰。在這種情況下,設備將從 PUF 私鑰計算自己的相應公鑰,并且在最終使用部署之前,證書頒發機構將在 NVM 中安裝證書。

圖5.使用 PUF 作為私鑰的 ECDSA 簽名。

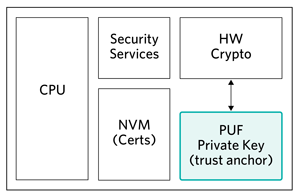

在圖6中,ChipDNA PUF私鑰是安全IC的根私鑰,與終端系統結合使用,與安全IC建立“信任根”,用于后續服務。

圖6.PUF 作為信任錨私鑰。

Maxim基于ChipDNA的商用安全IC

Maxim目前提供兩款基于ChipDNA PUF的安全IC:DS28E38采用非對稱ECDSA認證,DS28E50采用對稱SHA3認證。

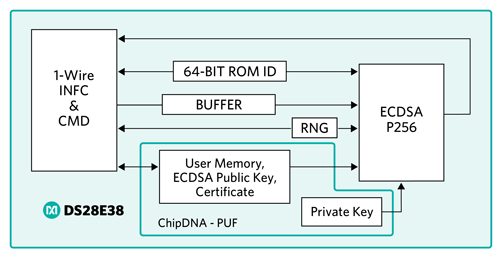

DS28E38是一款ECDSA認證器,利用公司的ChipDNA PUF輸出作為關鍵內容,對所有器件存儲的數據進行加密保護。或者,在用戶控制下,ChipDNA技術被用作ECDSA簽名操作的私鑰。該器件提供一組核心加密工具,這些工具源自集成模塊,包括非對稱 (ECC-P256) 硬件引擎、符合 FIPS/NIST 標準的真隨機數發生器 (TRNG)、2Kb 安全 EEPROM、僅遞減計數器和唯一的 64 位 ROM 標識號 (ROM ID)。ECC 公鑰/私鑰功能從 NIST 定義的 P-256 曲線運行,以提供符合 FIPS 186 的 ECDSA 簽名生成功能。DS28E38的框圖如圖7所示。

圖7.Maxim基于ChipDNA PUF的ECDSA認證器框圖。

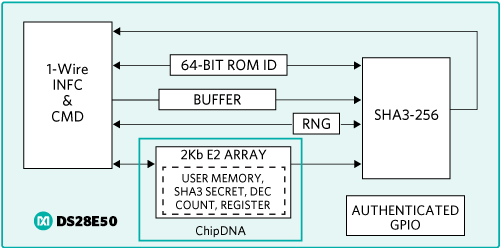

DS28E50是一款SHA3認證器,與DS28E38一樣,利用ChipDNA PUF輸出作為加密/解密密鑰來保護所有器件存儲的數據。該器件提供符合 FIPS-202 標準的雙向 SHA3-256 身份驗證、符合 FIPS/NIST 標準的 TRNG、2Kb 安全 EEPROM、僅遞減計數器、安全 GPIO 和獨特的 64 位 ROMID。DS28E50的框圖如圖8所示。

圖8.Maxim基于ChipDNA PUF的SHA3認證器框圖

總結

密碼學保護嵌入式系統內的電子資產。通過在嵌入式設計中使用具有加密功能的安全IC,設計人員無需成為密碼學專家即可獲得強大的設計保護。然而,安全IC本身可能成為日益復雜的網絡犯罪分子的攻擊目標。基于其固有的品質,ChipDNA PUF技術對逆向工程方法具有高度免疫力,為侵入性攻擊提供了決定性的對策。

審核編輯:郭婷

-

MOSFET

+關注

關注

150文章

8620瀏覽量

220547 -

半導體

+關注

關注

335文章

28919瀏覽量

238161 -

晶體管

+關注

關注

77文章

10020瀏覽量

141744

發布評論請先 登錄

物聯網嵌入式系統

嵌入式系統是什么 什么叫嵌入式系統

所有現代設備中都存在物理嵌入式系統是為什么?

嵌入式系統的定義和組成是什么

恩智浦以物理不可克隆技術(PUF)強化SmartMX2安全芯片

嵌入式系統設計|嵌入式計算

評論