每一代新產品的性能改進通常都伴隨著用戶必須遵守的實際要求,以便從運算放大器或轉換器獲得最佳性能。老一代運算放大器通常需要外部補償來定制響應;閃存A/D速度快,但耗電且輸入阻抗低。BiMOS轉換器簡化了應用問題;典型的高阻抗良性輸入結構易于驅動。高速CB運算放大器和基于開關電容的CMOS轉換器可最大限度地降低功耗和價格。運算放大器AD8011驅動AD876 A/D的應用顯示了新一代IC的優勢和實際問題。

高速開關電容A/D架構要求用戶在設計接口電路時了解一系列獨特的問題。最佳接口取決于應用是只需要低失真和雜散(動態特性)、低噪聲,還是同時需要低噪聲和低失真。

整個信號鏈(處理信號的一系列功能元件)必須優化總諧波失真(THD)和無雜散動態范圍(SFDR)等規格的系統(例如通信系統)通常涉及頻譜分析或處理。輸入信號在樣本之間以相對較小的增量變化;信號含量限制在奈奎斯特頻率<(即采樣率的1/2)。

專注于噪聲性能的系統可能會犧牲THD和SFDR來增加動態范圍(SNR)。雖然失真規格在這些低噪聲應用(如基于CCD的成像)中可能并不那么重要,但可能需要寬帶寬和快速瞬態響應來確保快速建立。

數據采集系統,如DSO-數字采樣示波器-是需要低雜散和失真以及寬動態范圍(SNR)的典型應用。除了電壓和電流噪聲外,相位噪聲(例如由孔徑抖動產生的相位噪聲)也值得關注。這些系統通常處理各種各樣的信號,執行頻譜信號處理和處理大規模瞬變(通常來自多路復用前端)。

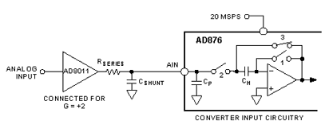

驅動開關電容ADC輸入:AD876的輸入保持電容必須在每個時鐘周期充電至新的輸入電壓。輸入驅動器必須提供的電量取決于上一次轉換時存儲在保持電容上的電壓與采樣時鐘從高電平(保持模式)轉換到低電平(軌道)時施加到A/D的電壓之差。此差異越小,所需的增量費用就越少。另一方面,對于轉換之間的滿量程變化,輸入驅動器必須提供較大的電荷增量。圖2所示電路由AD8011驅動AD876,說明了性能選項。無論運算放大器本身如何配置,增加一個串聯電阻(可能還有一個并聯電容)都可以提高運算放大器/轉換器對的性能。

為了研究為特定應用選擇最佳值電阻和電容時的一些考慮因素,AD8011的增益配置為+2(帶寬約為180 MHz),并如圖所示連接到AD876輸入。

圖2.驅動具有開關電容采樣保持的采樣ADC。

圖3a顯示了測試信號:頂部跡線是AD8011的模擬輸入,這是一個1 V p-p方波。底部跡線是AD876采樣時鐘。當時鐘為低電平時,SHA 跟蹤輸入;當它變高時,A/D 的 SHA 切換到保持。請注意,AD876每次轉換都必須獲得輸入電壓的滿量程變化;這種情況對AD8011提出了最嚴格的要求,因為它必須在每個轉換周期提供最大的電荷量。AD8011無法瞬時提供電荷差,因此在A/D采樣時鐘轉換期間,轉換器輸入端存在瞬變。

圖3.輸入波形。

圖3b顯示了輸入方波在擴展標度上處于正偏移時的瞬變(上圖),具有25 ns跟蹤模式時鐘脈沖。較小的上升沿保持瞬態并不重要;它發生在下一個樣本采集之前很久。當ADC獲取滿量程電荷變化時,下降沿瞬變約為-114 mV;恢復和建立至0.1%(10位或2 mV)必須在跟蹤模式脈沖的持續時間內進行,并且在上升沿之前 - 此處,使用20 Ω電阻時,恢復和建立時間為100 ns。對于20 MSPS采樣速率(50%占空比),恢復必須在25 ns以內。較慢的放大器可用于較低的采樣率。

圖4.轉換器和放大器電路的失真和噪聲。

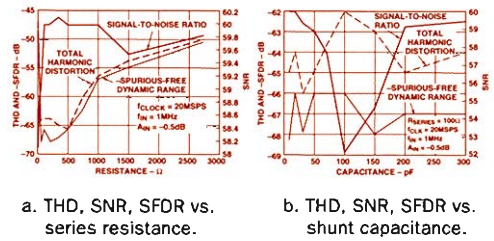

串聯電阻器有助于:大多數應用受益于AD8011輸出和AD876VIN引腳之間的串聯電阻,以將AD8011的輸出級與AD876的輸入電容隔離開來,并限制運算放大器必須提供的峰值電流。低至33 Ω(圖4a)大大降低了THD(從-47dB到-64 dB),并增加了SNR(從58dB增加到60 dB)和SFDR(從48dB增加到68 dB);可以使用高達 500 Ω,而不會因非線性容性負載而增加失真。小串聯電阻也改善了建立時間;如果沒有它,ADC的容性負載直接施加在放大器的輸出端,會導致放大器的響應出現一些峰值,并且建立速度變慢。但是,考慮到ADC的輸入電容、雜散和任何增加的電容,增加電阻會通過低通濾波降低帶寬。500 Ω 和 20 pF 的頻率約為 3 MHz,為 -16 dB。

分流電容限制噪聲:AD876的全功率帶寬至少為150 MHz,噪聲帶寬甚至更大。頻率>采樣速率1/2的寬帶輸入噪聲將被混疊回基帶,并將降低數字化信號的SNR。對于噪聲敏感型應用,帶串聯電阻的并聯電容(圖2)可在AD876輸入端濾除高頻外部噪聲。

圖4b顯示了使用100 Ω串聯電阻和各種分流電容時的噪聲和失真。SFDR相對不受影響,保持在66至68 dB范圍內。但是,對于50 pF至200 pF范圍內的電容,THD大幅增加(從-65至-62 dB),SNR大幅降低(從59降至低至52 dB)。SNR降低是由未完全穩定的保持到跟蹤瞬變的毛刺引起的高次諧波混疊引起的;在876b條件下,它們在AD4輸出端的基帶信號中顯示為噪聲。

對于更高的并聯電容值,SNR會大大提高,但代價是帶寬。(例如)200 pF時,整個系統的-3 dB帶寬降至約8 MHz,輸入信號中的任何快速瞬變在單個轉換周期內都可能無法穩定到10位精度。

當使用串聯R和并聯C來優化系統行為時,考慮應用的目標非常重要。如果動態性能在寬輸入頻率范圍內至關重要,則最好使用20 Ω串聯電阻將分流電容保持在100 pF以下。如果要優化噪聲性能,請考慮更長的RC時間常數,以及是否可以用瞬態響應換取低噪聲。在任何情況下,在AD10采樣時鐘進行跟蹤保持轉換之前,輸入有時間建立至876位精度,性能最佳。還要記住,AD8011非常安靜,可以在早期階段濾除寬帶噪聲,而不必擔心AD8011噪聲會降低SNR。

審核編輯:郭婷

-

CMOS

+關注

關注

58文章

5724瀏覽量

235700 -

轉換器

+關注

關注

27文章

8726瀏覽量

147424 -

運算放大器

+關注

關注

215文章

4952瀏覽量

173138

發布評論請先 登錄

相關推薦

AD8275 ADC驅動器,具有電平轉換功能,可簡化信號調理

Linear推出ADC驅動器LT6350

ADC驅動器或差分放大器設計指南

如何針對設計選擇合適的差分ADC驅動器

三種不同的ADC驅動器架構和應用分析

ADI-高速差分ADC驅動器設計指南

應用示例—ADC驅動器

應用示例—ADC驅動器

評論