通過以雙倍采樣率多路復用(例如)一對轉換器的輸出來對多個模數(shù)轉換器進行時間交錯,現(xiàn)在已經(jīng)是一個成熟的概念——布萊克和霍奇斯于 1980 年首次提出。1, 2在設計 7 位、4MHz 模數(shù)轉換器 (ADC) 時,他們確定時間交錯解決方案需要的芯片面積比同類的 2 MHz 模數(shù)轉換器n閃存轉換器設計。事實證明,這種新概念在他們的設計中具有巨大的價值,但節(jié)省空間并不是它的唯一好處。ADC的時間交錯提供了一種概念上簡單的方法,用于乘以現(xiàn)有高性能ADC的采樣速率,例如14位、105 MSPS AD6645和12位、210 MSPS AD9430。在許多不同的應用中,這一概念已被用于使需要極高采樣率模數(shù)轉換的系統(tǒng)受益。

雖然標準ADC產(chǎn)品的速度和分辨率已經(jīng)遠遠超過4 MHz和7位,但時間交錯ADC系統(tǒng)(有充分的理由)并沒有遠遠超過8位分辨率。然而,在8位性能水平下,這一概念已在測試和測量行業(yè)中得到廣泛采用,特別是對于寬帶數(shù)字示波器。安捷倫實驗室最近開發(fā)的 20 GSPS、8 位 ADC 證明它繼續(xù)在這個市場上產(chǎn)生影響3并被安捷倫技術無限公司采用?示波器系列。4事實上,時間交錯式ADC系統(tǒng)在8位電平上蓬勃發(fā)展,但在需要高分辨率、寬帶寬和穩(wěn)定動態(tài)范圍相結合的應用中,它們仍然不足。

12位和14位電平的時間交錯ADC系統(tǒng)的主要限制因素是通道匹配的要求。提供8 dB動態(tài)范圍的50位系統(tǒng)可以容忍0.25%的增益失配和5 ps的時鐘偏斜誤差。這種精度水平可以通過傳統(tǒng)方法實現(xiàn),例如匹配物理通道布局、使用通用ADC基準電壓、預篩選器件和有源模擬調整,但在更高的分辨率下,要求要嚴格得多。到目前為止,采用更多創(chuàng)新匹配技術的設備尚未商業(yè)化。

本文將詳細概述12位和14位時間交錯ADC系統(tǒng)的匹配要求,討論先進的數(shù)字后處理技術作為使能技術的理念,并介紹采用迄今為止最有前途的解決方案高級濾波器組(AFB)的器件。?),來自 V Corp Technologies, Inc.5, 6

時間交錯過程概述

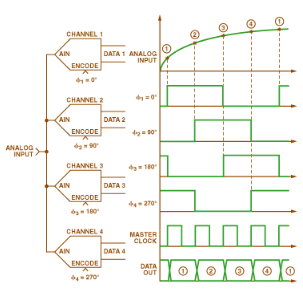

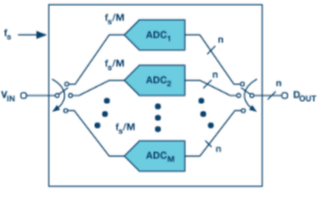

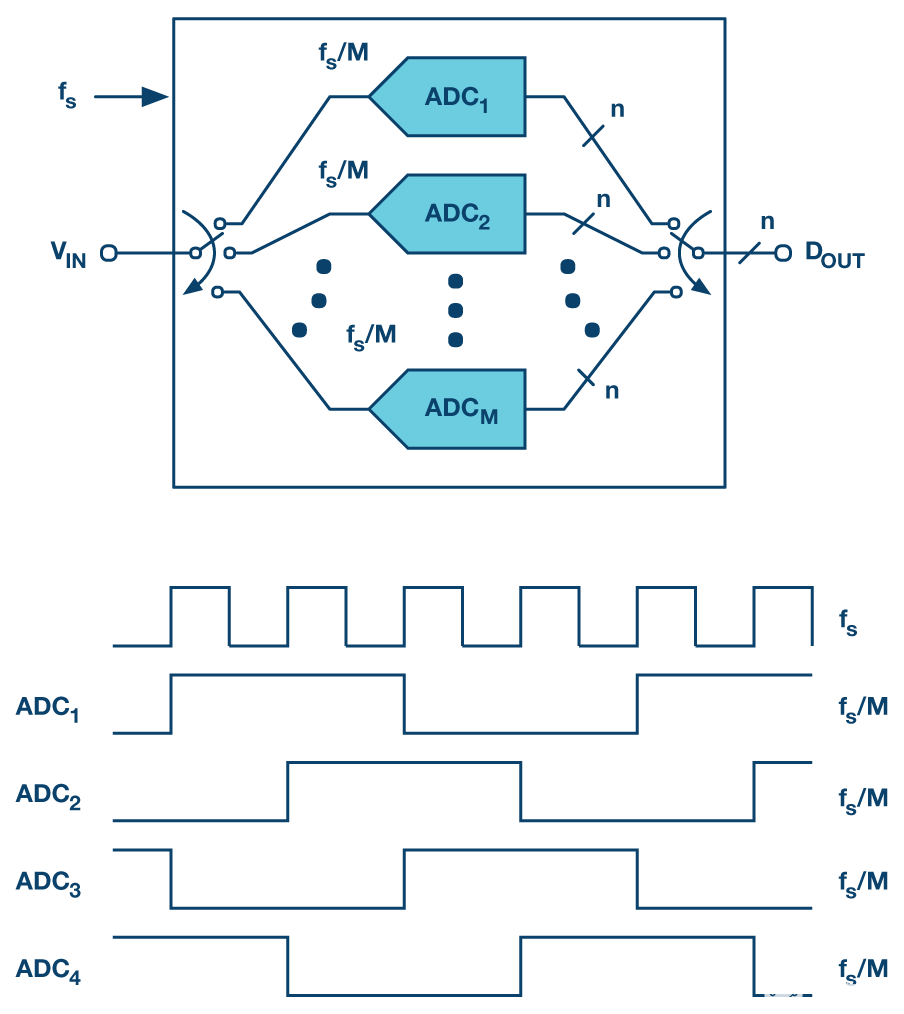

ADC系統(tǒng)的時間交錯采用以總系統(tǒng)采樣速率的1/m采樣速率運行m ADC的概念。每個通道的時鐘都處于一個相位,使系統(tǒng)作為一個整體能夠以相等間隔的時間增量進行采樣,從而創(chuàng)建單個A/D轉換器全速采樣的無縫圖像。圖1顯示了典型四通道、時間交錯ADC系統(tǒng)的模塊圖和時序圖。四個ADC通道中的每一個都以系統(tǒng)采樣速率的四分之一運行,間隔為90°。最終輸出數(shù)據(jù)流是通過以正確的順序(例如,1、2、3、4、1、2等)交錯所有單獨的通道數(shù)據(jù)輸出來創(chuàng)建的。在雙轉換器示例中,兩個ADC通道的時鐘頻率為整個系統(tǒng)采樣速率的一半,并且它們彼此異相180°。

圖1.四通道時間交錯ADC系統(tǒng)。

為簡單起見,本文主要關注雙轉換器系統(tǒng),但當需要闡明關鍵性能差異時,將討論四轉換器系統(tǒng)。大多數(shù)框圖、數(shù)學關系和解決方案將突出顯示雙通道配置。

時間交錯的設計挑戰(zhàn)

如前所述,通道間匹配對時間交錯ADC系統(tǒng)的動態(tài)范圍性能有直接影響。ADC通道之間的失配會導致動態(tài)范圍下降,在FFT圖中,動態(tài)范圍下降表現(xiàn)為雜散頻率分量,稱為鏡像雜散和失調雜散。與時間交錯ADC系統(tǒng)相關的鏡像雜散是ADC通道之間增益和相位不匹配的直接結果。增益誤差和相位誤差產(chǎn)生彼此正交的誤差函數(shù)。兩者都有助于在相同頻率位置的鏡像雜散能量。失調雜散由ADC通道之間的失調差產(chǎn)生。與鏡像雜散不同,偏移雜散不依賴于輸入信號。對于給定的失調失配,失調雜散將始終處于同一電平。對這些雜散行為的廣泛研究產(chǎn)生了幾種數(shù)學方法來表征信道匹配誤差與動態(tài)范圍性能之間的關系。7, 8

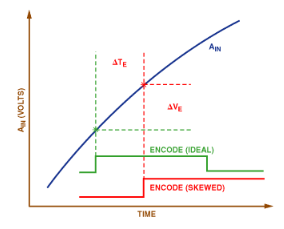

雖然這些方法徹底且非常有用,但這里使用的“誤差電壓”方法提供了一種簡單的方法來理解這種關系,而無需深入研究復雜的數(shù)學推導。該方法基于ADI公司應用筆記AN-501中使用的相同理念9建立ADC中孔徑抖動與信噪比(SNR)下降之間的關系。誤差電壓定義為“預期”采樣電壓與“實際”采樣電壓之差。這些差異是由一大部分誤差造成的,這些誤差分為三個基本類別:增益(圖2)、相位(圖3)和失調(圖4)失配。

圖2.增益不匹配導致的電壓誤差。

圖3.由于編碼/時鐘偏差導致的電壓誤差。

圖4.失調失配導致的電壓誤差。

在雙轉換器交錯系統(tǒng)中,增益和相位失配產(chǎn)生的誤差電壓導致位于奈奎斯特減去模擬輸入頻率的鏡像雜散。失調失配會產(chǎn)生誤差電壓,導致位于奈奎斯特的失調雜散。由于偏移雜散位于奈奎斯特頻段的邊緣,雙通道系統(tǒng)的設計人員通常可以圍繞該頻段規(guī)劃系統(tǒng)頻率,并將精力集中在增益和相位匹配上。圖5顯示了雙通道系統(tǒng)的典型FFT圖。

圖5.典型的雙轉換器交錯FFT圖。

在四轉換器交錯系統(tǒng)中,有三個鏡像雜散和兩個失調雜散。由ADC通道之間的增益和相位失配產(chǎn)生的鏡像雜散位于(1)奈奎斯特減去模擬輸入頻率和(2)奈奎斯特加或減模擬輸入頻率的一半。偏移雜散位于奈奎斯特和奈奎斯特的一半(波段中間)。圖6顯示了四轉換器系統(tǒng)的典型FFT圖,說明了這五個雜散的位置。

圖6.典型的四轉換器交錯FFT圖。

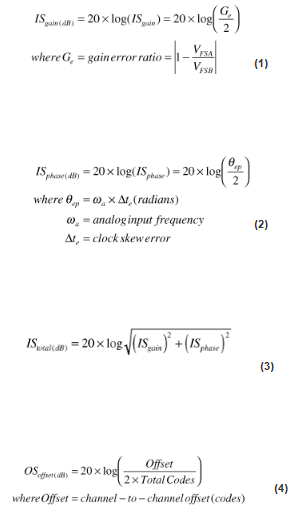

一旦知道三個失配組中每個組的誤差電壓,就可以使用以下公式來計算鏡像和失調雜散(IS獲得是階段是總這抵消) 在單音、雙轉換器系統(tǒng)中:

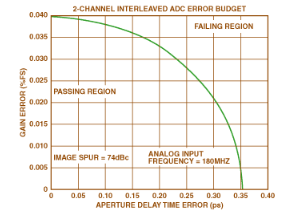

如前所述,增益和相位誤差產(chǎn)生正交誤差函數(shù)7,需要它們對圖像支線的個人貢獻的“和方根”組合。使用這些公式,可以制定誤差預算,以確定維持給定動態(tài)范圍要求所需的匹配級別。例如,在12 MHz輸入頻率下,74位動態(tài)范圍要求為180 dBc,則需要增益匹配優(yōu)于0.02%,孔徑延遲匹配優(yōu)于300 fs!如果增益可以完美匹配,則孔徑延遲匹配可以“放松”到大約350 fs。圖7顯示了此12位、180 MHz示例的詳細“誤差預算曲線”示例。

圖7.誤差預算:12 位、2 通道、180MHz 輸入。

表I提供了幾種不同情況的匹配要求,以說明使經(jīng)典的時間交錯A/D轉換系統(tǒng)在寬帶寬上以12位和14位分辨率工作所需的極高精度。

表 I. 時間交錯 ADC 匹配要求。

|

180 MHz 時的性能 要求 |

SFDR (dBc) |

增益 匹配 (%) |

光圈 匹配 (fs) |

| 12 位 | 74 | 0.04 | 0 |

|

12 位 |

74 |

0 | 350 |

|

12 位 |

74 |

0.02 | 300 |

|

14 位 |

86 |

0.01 |

0 |

|

14 位 |

86 |

0 | 88 |

|

14 位 |

86 |

0.005 | 77 |

寬帶寬時間交錯ADC系統(tǒng)的傳統(tǒng)方法

傳統(tǒng)的2通道時間交錯ADC系統(tǒng)采用圖8所示的基本配置。傳統(tǒng)時間交錯ADC系統(tǒng)中的第一級匹配是通過減少通道之間的物理和電氣差異來實現(xiàn)的。例如,增益匹配通常通過使用公共基準電壓和精心匹配的物理布局來控制。相位匹配是通過手動調整時鐘(或模擬輸入)路徑的電氣長度和/或通過控制時鐘分配電路的電氣特性(上升/下降時間、偏置電平、觸發(fā)電平等)的特殊調整技術來實現(xiàn)的。失調匹配取決于各個ADC的失調性能。

圖8.傳統(tǒng)時間交錯ADC的功能圖

其中許多匹配方法都基于仔細的模擬設計和調整技術。雖然有很多優(yōu)秀的想法可以滿足這些苛刻的匹配要求,但其中許多都需要額外的電路來增加自己的誤差源,這違背了實現(xiàn)精確增益和相位匹配的最初目的。這種想法的一個例子是設置兩個不同時鐘信號的上升和下降時間。任何能夠提供這種控制水平的電路都會受到電源電壓和溫度對每個通道相位行為的影響。

先進的數(shù)字后處理

隨著新數(shù)字信號處理技術的發(fā)展,以及廉價、高速、可配置的數(shù)字硬件平臺(DSP、FPPGA、CPLD、ASIC 等)的進步,為時間交錯 ADC 性能的突破開辟了道路。與傳統(tǒng)的模擬匹配技術相比,數(shù)字后處理方法有幾個優(yōu)點。它們在實現(xiàn)方面非常靈活,其精度可以遠遠超過目標ADC分辨率。數(shù)字信號處理技術如何影響時間交錯系統(tǒng)架構的概念視圖如圖9所示。該概念采用一組數(shù)字校準傳遞函數(shù)來處理每個ADC的輸出數(shù)據(jù),從而創(chuàng)建一組新的“校準輸出”。這些數(shù)字校準傳遞函數(shù)可以使用各種數(shù)字濾波器配置(FIR、IIR等)來實現(xiàn)。它們可以像調整一個通道的增益一樣簡單,也可以像在寬帶寬和溫度范圍內調整每個通道的增益、相位和失調一樣復雜。

寬帶寬和溫度匹配是使用數(shù)字后處理技術提高時間交錯ADC系統(tǒng)性能的最大機遇和挑戰(zhàn)。在寬帶寬和溫度范圍內為多個ADC通道設計數(shù)字校準傳遞函數(shù)所需的數(shù)學推導極其復雜且不容易獲得。然而,在這一領域投入了大量的學術工作,創(chuàng)造了許多有趣的解決方案。其中一個解決方案被稱為高級過濾器庫(AFB),其為重大突破提供平臺的能力非常突出。

圖9.數(shù)字后處理架構示例。

高級過濾器組 (AFB)

AFB是首批商用數(shù)字后處理技術之一,對時間交錯ADC系統(tǒng)的性能產(chǎn)生重大影響。通過在寬帶寬和溫度范圍內提供精確的通道間增益、相位和失調匹配,AFB完全有能力在高速12/14位應用領域牢固地建立時間交錯ADC系統(tǒng)。除了匹配功能外,AFB還為ADC系統(tǒng)提供相位線性化和增益平坦度補償。圖10顯示了采用AFB的系統(tǒng)的基本框圖表示。

圖 10.空軍基地基本框圖。

通過使用獨特的多速率FIR濾波器結構,AFB可以很容易地實現(xiàn)到方便的數(shù)字硬件平臺中,例如FPGA或CPLD。FIR系數(shù)是使用專利方法計算的,該方法涉及從圖9所示的方程開始,然后應用各種高級數(shù)學技術來求解數(shù)字校準傳遞函數(shù)。

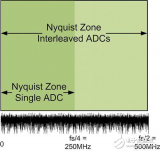

AFB使時間交錯ADC系統(tǒng)能夠使用高達90%的奈奎斯特頻段,并且可以配置為在轉換器的任何奈奎斯特區(qū)(例如,第一、第二、第三等)工作。可以使用一組邏輯輸入來選擇適當?shù)哪慰固貐^(qū),這些邏輯輸入控制所需的FIR系數(shù)。

空軍基地設計示例

AD12400是ADI公司利用時間交錯和AFB的全新產(chǎn)品系列的首款產(chǎn)品。其性能將用于說明將最先進的ADC設計與先進的數(shù)字后處理技術相結合可以實現(xiàn)的目標。圖11顯示了AD12400的框圖及其關鍵電路功能。AD12400采用獨特的模擬前端電路,具有400 MHz輸入帶寬、兩個12位、200 MSPS ADC通道,以及采用高級現(xiàn)場可編程門陣列(FPGA)的AFB實現(xiàn)方案。它采用上面討論的許多經(jīng)典匹配技術以及非常低抖動的時鐘分配電路進行設計。這些關鍵組件相結合,開發(fā)出一款 12 位、400 MSPS ADC 模塊,該模塊在 90% 的奈奎斯特頻段和 85°C 溫度范圍內性能非常好。它具有 400 MHz 的模擬輸入帶寬。

圖 11.AD12400原理框圖

ADC的傳遞函數(shù)是在制造過程中通過寬帶寬、寬溫度范圍測量獲得的。該檢定例程將ADC的測量傳遞函數(shù)直接饋送到AFB系數(shù)計算過程中。一旦對ADC進行了表征,并計算了所需的FIR系數(shù),F(xiàn)PGA就會被編程,產(chǎn)品就可以開始工作了。使用AFB的特殊FIR結構和系數(shù)計算過程實現(xiàn)寬帶寬匹配。通過使用板載數(shù)字溫度傳感器選擇多個FIR系數(shù)組之一,可實現(xiàn)寬溫度性能。

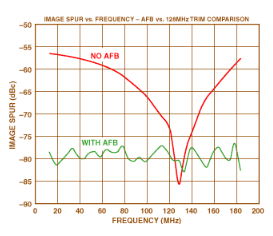

這項技術的真正影響可以在圖12和圖13中看到。圖12顯示了該系統(tǒng)第一個奈奎斯特區(qū)的鏡像雜散性能。圖12中的第一條曲線表示2通道時間交錯系統(tǒng)的性能,該系統(tǒng)經(jīng)過精心設計,可在布局中提供最佳匹配。該曲線中鏡像雜散的行為表明,該系統(tǒng)是在128 MHz的模擬輸入頻率下手動調整的。圖13的類似觀察表明,手動微調溫度為40°C。

圖 12.在頻率范圍內“前后”手動調整系統(tǒng)的性能。

圖 13.在溫度范圍內“前后”手動調整系統(tǒng)的性能。

盡管AD12400 ADC采用了精心的PCB布局、緊密匹配的前端電路、緊密匹配的時鐘分配電路以及通用基準電壓,但隨著頻率和/或溫度偏離手動調整條件,動態(tài)范圍會迅速下降。通過分析影響該電路的一些敏感因素,可以在任何雙轉換器時間交錯ADC系統(tǒng)中預測這種快速的衰減速率。例如,典型的高性能12位ADC的增益溫度系數(shù)為0.02%/°C。 在這種情況下,溫度變化10°C會導致增益變化0.2%,導致鏡像雜散為60 dBc(參見公式1)。僅考慮這種單一ADC溫度特性,預測的鏡像雜散比圖3所示的30°C性能差13 dB。

相比之下,當啟用AFB補償時,這些圖中顯示的動態(tài)范圍性能仍然穩(wěn)定。事實上,在近12 MHz的帶寬和190°C的溫度范圍內,動態(tài)范圍性能超過了40位電平。 這種方法的另一個顯著優(yōu)勢是,通過使用額外的FIR系數(shù)組,溫度范圍實際上可以從所示的20°C至60°C范圍擴展到0°C至85°C,如AD12400所示。

結論

時間交錯正逐漸成為高速ADC系統(tǒng)性能增強的重要趨勢。先進的數(shù)字后處理方法(如AFB)為分辨率水平的嚴格通道匹配要求提供了一種方便的解決方案,這是以前時間交錯系統(tǒng)無法實現(xiàn)的。當與現(xiàn)有的最佳ADC架構相結合時,先進的DSP技術(如AFB)已準備好將高速ADC系統(tǒng)的性能提升到一個新的水平,并促進在醫(yī)療成像、精密藥物分配器(流體流量測量)、合成孔徑雷達、數(shù)字波束形成通信系統(tǒng)和高級測試/測量系統(tǒng)等要求苛刻的市場中大幅改進產(chǎn)品和系統(tǒng)。該技術將在不久的將來帶來許多突破,包括14位/400 MSPS和12位/800 MSPS ADC系統(tǒng)。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

9094瀏覽量

152014 -

adc

+關注

關注

99文章

6714瀏覽量

549434 -

PCB

+關注

關注

1文章

2105瀏覽量

13204

發(fā)布評論請先 登錄

基于時間交錯技術實現(xiàn)10位/400 MSPS ADC的設計

具有專利的運動精確圖像視頻后處理器

拓展一些關于交錯ADC的觀點

ADC 的時間交錯特性討論資料下載

基于數(shù)字后處理算法的并行交替采樣ADC系統(tǒng)

淺談模數(shù)轉換器(ADC)的時間交錯

利用CTLE和時間交錯閃存ADC來降低ADC分辨率

交錯ADC:揭開謎團

評論