問:我讀過你們的數(shù)據(jù)手冊和應(yīng)用筆記,也參加了你們的研討會,但我仍然對如何處理ADC上的模擬(AGND)和數(shù)字(DGND)接地引腳感到困惑。數(shù)據(jù)手冊通常說要在器件上將模擬和數(shù)字地連接在一起,但我不希望ADC成為系統(tǒng)的星形接地點(diǎn)。我該怎么辦?

A.首先,不要因?yàn)槟鷮θ绾翁幚砟M和數(shù)字接地感到困惑而感到難過。很多人也是如此!大部分混淆首先來自ADC接地引腳的標(biāo)記。引腳名稱 AGND 和 DGND 是指組件本身內(nèi)部發(fā)生的情況,并不一定意味著您應(yīng)該在外部使用它們。讓我解釋一下。

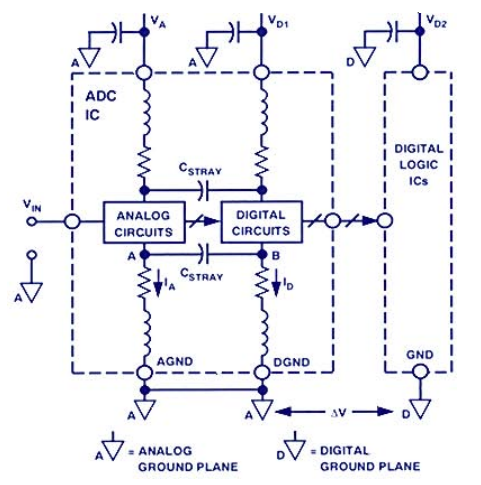

在同時具有模擬和數(shù)字電路的IC內(nèi)部,例如ADC,接地通常保持獨(dú)立,以避免將數(shù)字信號耦合到模擬電路中。該圖顯示了ADC的簡單模型。對于將芯片上的焊盤連接到封裝引腳相關(guān)的引線焊電感和電阻,IC設(shè)計人員實(shí)際上無能為力。快速變化的數(shù)字電流在B點(diǎn)產(chǎn)生電壓,該電壓將不可避免地通過雜散電容耦合到模擬電路的A點(diǎn)。盡管如此,IC設(shè)計人員的工作還是使芯片工作。但是,您可以看到,為了防止進(jìn)一步耦合,AGND和DGND引腳應(yīng)在外部連接在一起,以最小的引線長度連接到相同的低阻抗接地層。DGND連接中的任何額外外部阻抗都會導(dǎo)致B點(diǎn)產(chǎn)生更多的數(shù)字噪聲;反過來,它將通過雜散電容將更多的數(shù)字噪聲耦合到模擬電路中。雖然這是一個非常簡單的模型,但這有助于說明這一點(diǎn)。

Q. 好的,您告訴我將IC的AGND和DGND引腳連接到同一接地層 - 但我在系統(tǒng)中維護(hù)單獨(dú)的模擬和數(shù)字接地層。我希望它們只在一個點(diǎn)上連接在一起:電源返回全部連接在一起并連接到機(jī)箱接地的公共點(diǎn)。現(xiàn)在我該怎么辦?

A.如果您的系統(tǒng)中只有一個數(shù)據(jù)轉(zhuǎn)換器,您實(shí)際上可以按照數(shù)據(jù)手冊中的規(guī)定進(jìn)行操作,并在轉(zhuǎn)換器上將模擬和數(shù)字接地系統(tǒng)連接在一起。您的系統(tǒng)星形接地點(diǎn)現(xiàn)在位于數(shù)據(jù)轉(zhuǎn)換器上。但這可能是非常不可取的,除非您最初在規(guī)劃系統(tǒng)時考慮到了這個想法。如果將多個數(shù)據(jù)轉(zhuǎn)換器位于不同的PCB上,則概念就會崩潰,因?yàn)槟M和數(shù)字接地系統(tǒng)在多個PCB上的每個轉(zhuǎn)換器上連接在一起。這是對地面循環(huán)的完美邀請!

問:我想我已經(jīng)想通了!如果我必須在器件上將AGND和DGND引腳連接在一起,并且我想保持單獨(dú)的系統(tǒng)模擬和數(shù)字接地,我將AGND和DGND連接到PCB上的模擬接地層或數(shù)字接地層,但不能同時連接兩者。右?現(xiàn)在,既然ADC既是模擬器件又是數(shù)字器件,那么應(yīng)該選擇哪一個?

答:正確!現(xiàn)在,如果將AGND和DGND引腳都連接到數(shù)字接地層,則模擬輸入信號將產(chǎn)生數(shù)字噪聲總和,因?yàn)樗赡苁菃味说模⒁阅M接地層為基準(zhǔn)。

Q. 所以正確的答案是將AGND和DGND引腳都連接到模擬接地層?但是,這不會在我安靜的模擬接地層上注入數(shù)字噪聲嗎?輸出邏輯的噪聲容限是否降低了,因?yàn)樗F(xiàn)在以模擬接地層為基準(zhǔn),而所有其他邏輯都以數(shù)字接地層為基準(zhǔn)?我計劃將ADC輸出運(yùn)行到背板三態(tài)數(shù)據(jù)總線,這開始時會非常嘈雜,所以我認(rèn)為我需要我能得到的所有噪聲容限。

A.好吧,從來沒有人說生活是輕松或公平的!通過崎嶇不平的道路,您得出了正確的結(jié)論,但是您提出的問題 - 模擬接地層上的數(shù)字噪聲和ADC輸出上的噪聲容限降低 - 實(shí)際上并不像看起來那么糟糕;它們是可以克服的。讓幾百毫伏的電壓損壞數(shù)字接口顯然比將相同的損壞信號施加到模擬輸入端要好,因?yàn)?6位、10 V輸入范圍ADC的最低有效位僅為150 μV!首先,DGND引腳上的數(shù)字接地電流不可能真的那么糟糕,否則它們首先會降低ADC的內(nèi)部模擬部分!如果將ADC的電源引腳旁路到模擬接地層,使用高質(zhì)量的高頻陶瓷電容來產(chǎn)生高頻噪聲(例如0.1 μF),則將這些電流隔離到IC周圍的非常小的區(qū)域,并且它們對系統(tǒng)其余部分的影響很小。

數(shù)字噪聲容限會有所降低,但如果小于幾百毫伏左右,則通常可以使用TTL或CMOS邏輯。如果您的ADC具有單端ECL輸出,則可能需要在每個數(shù)字輸出上放置一個推挽門,即同時具有真輸出和互補(bǔ)輸出的推挽門。將該柵極封裝的接地連接到模擬接地層,并在接口上差分連接邏輯信號。使用另一端的差分線路接收器,該接收器接地至數(shù)字接地層。模擬和數(shù)字接地層之間的噪聲現(xiàn)在是共模的,其中大部分將在差分線路接收器的輸出端被抑制。您可以對TTL或CMOS使用相同的技術(shù),但通常有足夠的噪聲容限,不需要差分傳輸技術(shù)。

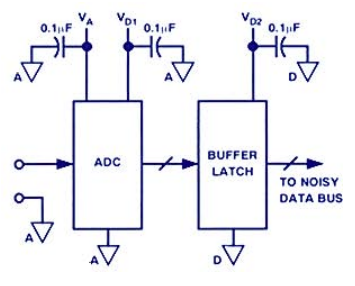

但是,你說的一件事讓我非常困擾。通常,將ADC輸出直接連接到噪聲數(shù)據(jù)總線是不明智的。總線噪聲可能通過雜散內(nèi)部電容耦合回ADC模擬輸入,范圍為0.1至0.5 pF。最好將ADC輸出直接連接到靠近ADC的中間緩沖鎖存器。緩沖鎖存器接地至數(shù)字接地層,因此其輸出邏輯電平現(xiàn)在與系統(tǒng)其余部分的輸出邏輯電平兼容。

問:我想我現(xiàn)在明白了,但是你為什么不一開始就調(diào)用ADC AGND的所有接地引腳;然后這些一開始就不會出現(xiàn)?

答:也許吧。但是,如果進(jìn)貨檢查人員在這些引腳之間連接歐姆表,并發(fā)現(xiàn)它們實(shí)際上并未在封裝內(nèi)連接在一起怎么辦?整個批次可能會被拒絕 - IC可能會被吹!此外,ADC數(shù)據(jù)手冊有一個傳統(tǒng),即我們必須標(biāo)記引腳以指示其真實(shí)功能,而不是我們希望它們是什么。

問奧克現(xiàn)在,這里有一個我一直保存為您的終極測試的問題!我有一位同事設(shè)計了一個具有獨(dú)立模擬和數(shù)字接地系統(tǒng)的系統(tǒng)。我的同事說,ADC的AGND引腳連接到模擬接地層,DGND引腳連接到數(shù)字接地層,系統(tǒng)工作正常!你怎么解釋這一點(diǎn)?

A.首先,僅僅因?yàn)椴?a href="http://www.1cnz.cn/v/" target="_blank">推薦練習(xí)并不一定意味著您在某些時候無法逃脫它,從而陷入一種虛假的安全感。(這是墨菲定律中鮮為人知的定律之一)。有些ADC對AGND和DGND引腳之間的外部噪聲不太敏感,可能是您的同事不小心選擇了其中一個。可能還有其他解釋 - 這需要我們探討您的同事對“工作正常”的定義 - 但關(guān)鍵是制造商在這些工作條件下不能保證ADC的規(guī)格。對于像ADC這樣的復(fù)雜組件,不可能在所有可能的工作條件下測試器件,尤其是那些一開始不推薦的工作環(huán)境!你的朋友這次很幸運(yùn),但你可以肯定,如果這種做法在未來的系統(tǒng)設(shè)計中繼續(xù)下去,墨菲定律最終會趕上他(或她)。

問:我想我現(xiàn)在理解ADC接地原理,但是DAC呢?

A.同樣的理念也適用。DAC的AGND和DGND引腳應(yīng)連接在一起并連接到模擬接地層。如果DAC沒有輸入鎖存器,則驅(qū)動DAC的寄存器應(yīng)以模擬接地層為基準(zhǔn)并接地,以防止數(shù)字噪聲耦合到模擬輸出。

問:包含ADC、DAC和DSP的混合信號芯片(如ADSP-21msp5O語音帶處理器)怎么樣?

一個。同樣的理念也適用。您永遠(yuǎn)不應(yīng)該認(rèn)為復(fù)雜的混合信號芯片(如ADSP-21msp50)只是一個數(shù)字芯片!應(yīng)該應(yīng)用我們剛剛討論的相同準(zhǔn)則。盡管16位Σ-Δ型ADC和DAC的有效采樣速率僅為8 ksps,但轉(zhuǎn)換器的工作過采樣頻率為1 MHz。該器件需要一個外部 13MHz 時鐘,并通過鎖相環(huán)從中生成一個內(nèi)部 52MHz 處理器時鐘。所以你看,成功應(yīng)用這個器件需要了解精密和高速電路的設(shè)計技術(shù)。

Q. 這些設(shè)備的模擬和數(shù)字電源要求如何?我應(yīng)該購買單獨(dú)的模擬和數(shù)字電源還是使用相同的電源?

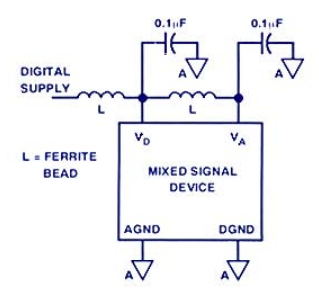

A.這實(shí)際上取決于您的數(shù)字電源上的噪聲量。例如,ADSP-21msp50具有用于+5 V模擬電源和+5 V數(shù)字電源的獨(dú)立引腳。如果您有一個相對安靜的數(shù)字電源,您可能也可以將其用于模擬電源。確保使用一個 0.1μF 陶瓷電容器對器件上的每個電源引腳進(jìn)行正確去耦。切記去耦至模擬接地層,而不是數(shù)字接地層!您可能還需要使用鐵氧體磁珠進(jìn)行進(jìn)一步隔離。下圖顯示了正確的排列。更安全的解決方案是使用單獨(dú)的+5 V模擬電源。如果可以承受額外的功耗,則可以使用三端穩(wěn)壓器從安靜的+5 V或+15 V電源產(chǎn)生+12 V電壓。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

184文章

17735瀏覽量

250501 -

芯片

+關(guān)注

關(guān)注

456文章

50886瀏覽量

424185 -

adc

+關(guān)注

關(guān)注

98文章

6503瀏覽量

544871

發(fā)布評論請先 登錄

相關(guān)推薦

詢問應(yīng)用工程師:接地(再次)

詢問應(yīng)用工程師:接地(再次)

評論