創建時鐘

使用SDC命令create_clock創建時鐘,時鐘周期20,占空比50%的時鐘信號;

create_clock-nameCLK-period20[get_portsCLK]-waveform{07}

-waveform 時鐘占空比,不指定該選項,則時鐘默認占空比為50%

生成時鐘

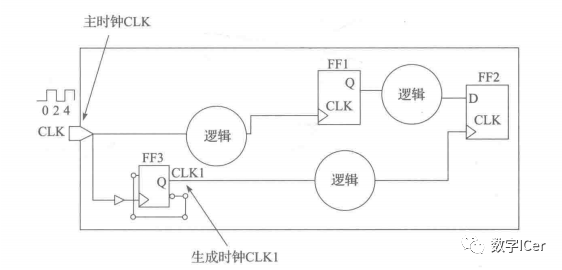

生成時鐘:是基于一個主時鐘并通過相關邏輯轉換后,在相位,頻率,占空比等方面和主時鐘有一定變化的分支時鐘;

生成時鐘的時鐘源來自主時鐘,其相位參考主時鐘;

生成時鐘可以通過以下方式生成:

時鐘分頻

時鐘倍頻

時鐘門控

通過SDC命令 create_generated_clock 來定義生成時鐘:

create_generated_clock-nameclk_gen-source[get_portsCLK][get_pins{DFF/Q}]-divide_by3

-source 設定生成時鐘的源引腳

divide_by 3 :3分頻

divide_by:表示生成時鐘通過分頻生成;

multiply_by :表示生成時鐘通過倍頻生成;

edges: 占空比設置

生成時鐘

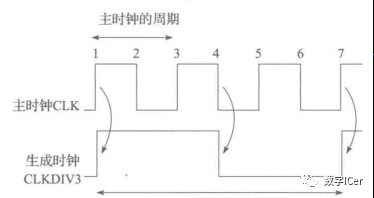

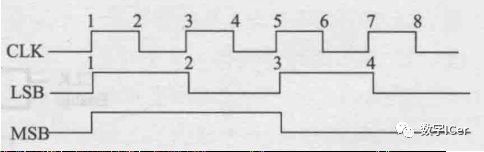

可對生成時鐘占空比進行設置:

占空比進行設置

create_generated_clock-nameCLK_LSB-source[get_portsCLK][get_pins{DFF/Q}]-edges{135}

create_generated_clock-nameCLK_LSB-source[get_portsCLK][get_pins{DFF/Q}]-edges{159}

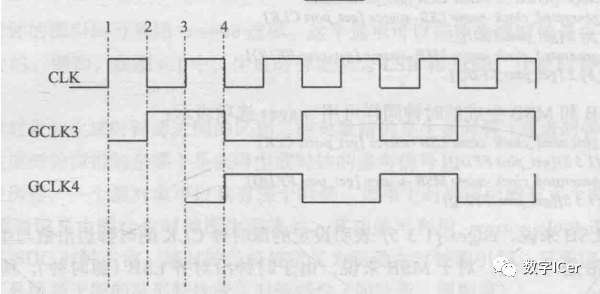

分頻器由源時鐘下降沿觸發:

源時鐘下降沿觸發

create_generated_clock-nameGCLK3-source[get_portsCLK][get_pins{DFF/Q}]-edges{246}

create_generated_clock-nameGCLK4-source[get_portsCLK][get_pins{DFF/Q}]-edges{468}

虛擬時鐘

虛擬時鐘即設計中不存在的時鐘,定義虛擬時鐘應滿足:

設計中的某個時鐘實際存在,但其時鐘源不是來自設計中任何引腳和端口;

由于虛擬時鐘和設計中的任何引腳和端口無直接關系,故定義虛擬時鐘時并不指定時鐘端口;

虛擬時鐘用于作為輸入輸出端口延時約束的時鐘源;

通過SDC命令創建虛擬時鐘:

create_clock-nameVIRTUAL_CLK-period10-waveform{05}

IO端口延遲

輸入延遲:在一個時鐘周期內,外部邏輯的輸出數據到達設計輸入端口所需的時間;

輸出延遲:在一個時鐘周期內,設計輸出端口數據到達外部邏輯所需的時間;

通過SDC命令set_input_delay在輸入端口指定延遲;

set_input_delay-clockCLK1.2[get_ports{IO}]

set_input_delay-max-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}] set_input_delay-min-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}]

-add_delay:通知工具除了現存的約束外,這是一個額外的約束,不會覆蓋前一個約束;如果沒有-add_delay,那么后面的約束會覆蓋前面的約束。

通過SDC命令set_output_delay在輸出端口指定延遲;

set_output_delay-max-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}]

set_output_delay-min-add_delay-clock[get_clocks{CLK}]15[get_ports{IO}]

負延遲:

下面值可能是負值:set_input_delay -max

set_input_delay -min

set_output_delay -max

set_output_delay -min

時鐘分組

同步時鐘:時鐘存在固定的相位關系,來自同一個時鐘源;異步時鐘:不存在固定的相位關系;

為了讓時序工具忽略異步時鐘之間的時序路徑或串擾分析,SDC提供了set_clock_groups命令,表明時鐘組之間的時序路徑不必考慮;

set_clock_groups-name{clk_group1}-group{GCCK}-group{RCLK}

-asynchronous:時鐘彼此不共享相位關系時可使用;

例:

set_clock_groups-name{clk_group1}-group[get_clocks{CCK1CLK2CLK3}]-group[get_clocks{CCK4CLK5CLK6}]

表示:CLK1,CLK2,CLK3分別異步于CLK4,CLK5,CLK6;

偽路徑

不需要做時序分析的時序路徑,可以通過偽路徑忽略該路徑,使得工具對該路徑不進行時序分析;

set_false_path-from[get_clocksCLK1]-to[get_clocksCLK2]

定義兩個時鐘域CLK1和CLK2之間的路徑為偽路徑;

set_false_path-through[get_pinsX1]-through[get_pinsX2]

定義按X1->X2的順序通過X1 X2引腳的路徑為偽路徑;

-from,-to,-through指定false的路徑;

-from X1 -to X2:表示從起點X1到終點X2的路徑;

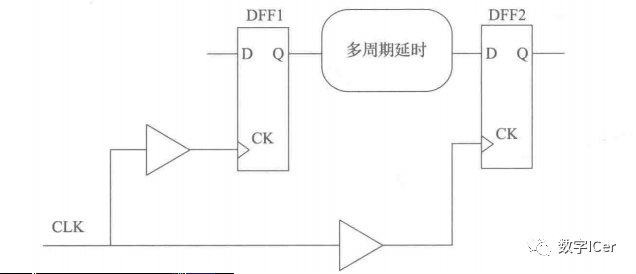

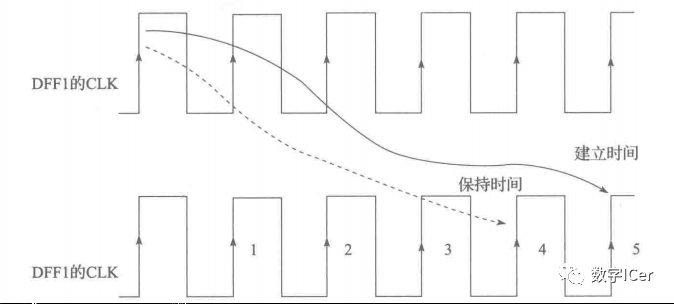

多周期路徑

多周期路徑,存在時序路徑較長或者信號在延時等于幾個時鐘周期的時間,如果仍然按照單周期進行約束,可能會出現時序違例,如下圖所示:

通過SDC命令set_multicycle_path:

set_multicycle_path-from[get_pinsDFF1/Q]-to[get_clocksDFF2/D]-setup5 set_multicycle_path-from[get_pinsDFF1/Q]-to[get_clocksDFF2/D]-hold4

-setup和-hold成對出現;

保持時間比建立時間少一個周期;

最大最小延遲

當需要點對點對某些路徑進行約束時,可通過最大最小延遲實現;

異步電路之間

輸入信號直接通過組合邏輯后輸出

當約束定義的是時序路徑中的節點時,則約束的僅在兩個節點之間;

set_max_delay-from[get_portsA1]-to[get_portsA2]8 set_min_delay-from[get_portsA1]-to[get_portsA2]5

上述定義A1到A2之間的時序路徑的約束最大延時8ns最小延時6ns;

當約束定義是時鐘時,最大最小延時將應用于該時鐘源所控制的所有路徑;

set_max_delay-from[get_clocksCLK1]-to[get_clocksCLK2]8 set_min_delay-from[get_clocksCLK1]-to[get_clocksCLK2]5

上述定義從時鐘域CLK1到CLK2之間的所有時序路徑的約束最大延時為8ns,最小延時為6ns;

IO環境建模

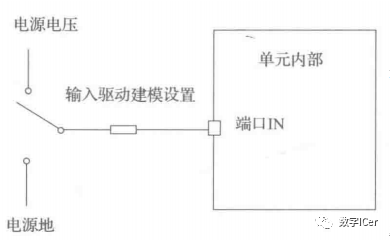

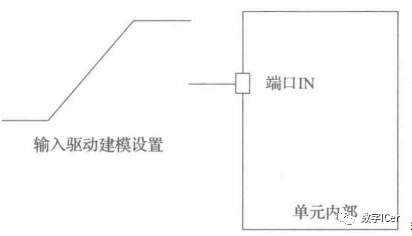

輸入驅動建模:默認情況下,如果沒有設置外部輸入驅動,時序分析工具則默認外部輸入驅動為無窮大;

推薦查看:綜合對象及環境屬性

1.set_drive

設置外部輸入驅動信息,通過該命令定義驅動該引腳的輸入驅動電阻值,通過該驅動電阻值計算出驅動端的轉換時間,并計入時序路徑延時信息;

當定義為0時,代表輸入端驅動力為無窮大;

set_drive0[get_portsCLK]

上述定義CLK輸入的驅動值為無窮大;

set_drive-rise0.4[all_inputs] set_drive-fall0.3[all_inputs]

上述命令定義所有輸入的驅動值,上拉驅動電阻為0.4,下拉驅動電阻為0.3;

-min指定最小電阻,用于保持時間分析;

-max指定最大電阻,用于建立時間分析;

如果不指定-max和-min,那么指定的值既用于建立時間分析,也用于保持時間分析;

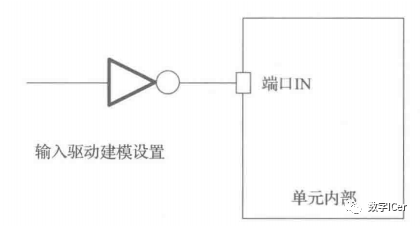

2.set_driving_cell

指定驅動單元

set_driving_cell-lib_cellINVX1M[all_inputs]

上述命令定義設計所有驅動力等價于單元庫中INVX1M單元的驅動力;

-lib_cell:指定驅動引腳的單元;

3.set_input_transition

通過set_input_transition 定義驅動該引腳的輸入驅動端轉換時間,設置的轉換時間越大驅動力越小,當定義為0時,其代表輸入端驅動力無窮大;

輸出負載建模:默認情況下,如果沒有設置外部輸出負載,時序分析工具則默認外部輸出負載為0;

1.輸出負載可通過SDC命令set_load,定義外部負載為一個等效電容,其電容值即為負載值(指定的是負載的實際電容值);

set_load10[all_outputs] set_load[expr[load_of$LIB_NAME/AND2X1M/A]*3][all_outputs]

上述命令定義所有輸出負載等效為庫中與門AND2X1M的引腳A的電容值的3倍;

負載類型:-pin_load,-wire_load可以指定負載類型是引腳負載還是線負載;

2.set_port_fanout_number value port_list

指定輸出的扇出數(如果已知外部寄生負載并且已經通過set_load指定了外部寄生負載,則這個命令沒有具體含義)

3.set_fanout_load value port_list

指定扇出負載(根據標準負載指定負載值)

其他時鐘特性

1.時鐘轉換時間:

時鐘在高低電平狀態下切換所需要的延時;

通過SCD命令 set_clock_transition 來定義時鐘轉換延時;

-rise 提供時鐘上升沿的轉換時間;

-fall 提供時鐘下降沿的轉換時間;

-max和-min 設置轉換時間的最大最小條件;

set_clock_transition-rise0.2[get_clocksCLK] set_clock_transition-fall-min0.2[get_clocksCLK] set_clock_transition-fall-max0.4[get_clocksCLK]

該命令僅用于預布局階段,即時鐘樹綜合完成之前,再時鐘樹生成之后,該命令不應用于任何的后布局時序分析;

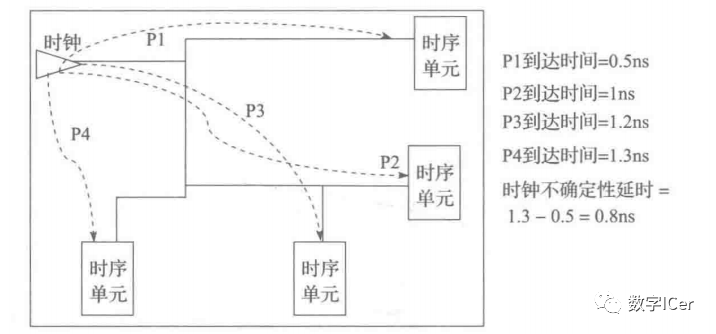

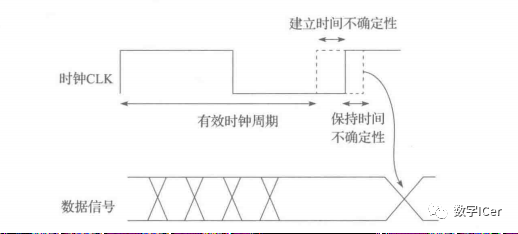

2.時鐘不確定性

實際時鐘本身與理想時鐘存在一定的差異,比如時鐘抖動,時鐘偏斜等因素;

時鐘偏斜:時鐘到達不同觸發器時間差異;

時鐘抖動:時鐘周期的不良偏差;

如上圖,時鐘到達P4時間為1.3ns,到達P3時間為1.2ns,那么不確定性延時為1.3-1.2=0.1ns;

通過SDC命令set_clock_uncertainty 可將時鐘偏斜和抖動模型化;

set_clock_uncertainty0.5[get_clocksCLK1] set_clock_uncertainty-setup0.5[get_clocksCLK2] set_clock_uncertainty-hold0.2[get_clocksCLK2]

以上時鐘不確定性為建立時間0.5ns,保持時間0.2ns;如下圖所示:

不同時鐘的不確定性

對于不同時鐘不確定度建模時,源時鐘可用-form,目的時鐘可用-to;

#C1到C2的建立時間和保持時間不確定度 set_clock_uncertainty-fromC1toC2-setup0.5 set_clock_uncertainty-fromC1toC2-hold0.5 #C1上升沿到C2下降沿的不確定度 set_clock_uncertainty-rise_fromC1fall_toC20.5 #C1和C2之間的不確定度 set_clock_uncertainty-fromC1toC20.5 set_clock_uncertainty-fromC2toC10.5

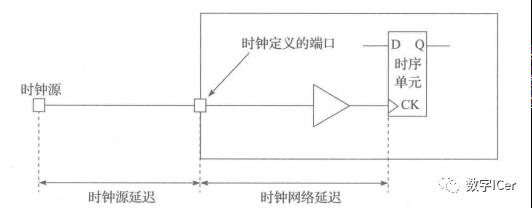

3.時鐘延遲

時鐘信號從時鐘源輸出端到達時序單元時鐘輸入端(如觸發器)所需要的時間,稱為時鐘延遲;

時鐘延遲包括源延遲和網絡延遲,源延遲是指源時鐘到達時鐘定義的端口的延遲;

網路延遲是指時鐘定義的端口到時序單元時鐘輸入端的延遲;

通過SDC命令set_clock_latency來定義時鐘延遲信息:

-source 設定源延遲:

set_clock_latency-source0.5[get_clocksC1]

set_clock_latency-source-early0.5[get_clocksC1] set_clock_latency-source-late1.0[get_clocksC1]

最長路徑的延遲可用-late,最短路徑的延遲可用-early。

或者:

set_clock_latency-source-min0.5[get_clocksC1] set_clock_latency-source-max1.0[get_clocksC1]

當未設定-source時,表示網路延遲;

#上下降沿網路延遲 set_clock_latency0.5-rise[get_clocksC1] set_clock_latency0.3-fall[get_clocksC1]

時鐘網路延遲和時鐘源延遲區別:

時鐘網絡延遲是時鐘樹生成前的設置,當實際時鐘樹生成后,時鐘網絡延遲將通過set_propagated_clock被時鐘樹的實際結果所替代;而時鐘源延遲則會一直存在。

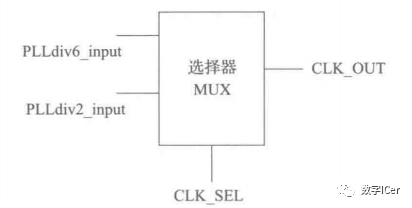

模式分析

恒定狀態約束:

根據設計中不同模式的需要,通過設置恒定狀態約束來定義時鐘選擇端口的對應狀態值,

在多個模式中選擇的時候,設定指定單一模式(相當于mux選擇器);

通過SDC命令set_case_analysis定義恒定狀態約束;

如上圖,假如CLK_SEL為0時,選擇PLLdiv6_input,CLK_SEL為1時,選擇PLLdiv2_input,則可設

set_case_analysis0[get_pins{mux.CLK_SEL}]

上述定義模式端口mux.CLK_SEL恒定狀態為0;

可以是0,1,rising,falling

其他SDC命令

指定工作條件和要執行分析類型:

set_operaing_conditions-maxss_1v62_125c-libraryss_1v62_125c

指定相應工作條件的庫(根據PVT溫度,電壓,工藝決定)

線負載模型:

set_wire_load_model-namesmic18_wl10-libraryss_1v62_125c

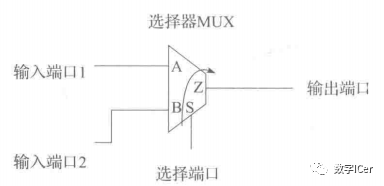

屏蔽時序弧:

set_disable_timing-fromS-toZ[get_cellsMUX]

上述命令屏蔽選擇器單元MUX中從S端到Z端的時序弧;

最大轉換時間:

set_max_transition0.8[all_outputs]

上述命令定義所有輸出驅動最大轉換時間為0.8ns;

最大電容負載:

set_max_capacitance0.6[all_outputs]

上述命令定義所有輸出驅動最大電容負載為0.6pF;

最大扇出:

set_max_fanout15[all_outputs]

上述命令定義所有輸出驅動最大扇出為15;

附:SDC命令

SDC約束分為:

時序約束

面積與功率約束

設計規則約束

接口約束

特定模式和配置約束

設計要求的異常

其他命令

時序約束

命令包括指定時鐘特性,端口延遲,引腳和路徑命令;

create_clock

create_generated_clock

set_clock_groups

set_clock_uncertainty

set_clock_latency

set_clock_transition

set_input_delay

set_output_delay

set_propagated_clock

set_clock_gating_check

set_ideal_latency

set_ideal_network

set_ideal_transition

set_max_time_borrow

set_resistance

set_time_derate

set_data_check

group_path

set_load

set_drive

set_input_transiton

set_fanout_load

面積與功率約束

set_max_area

create_valtage_area

set_level_shifter_threshold

set_level_shifter_strategy

set_max_dynamic_power

set_max_leakage_power

設計規則約束

set_max_transition

set_max_capacitance

set_min_capacitance

set_max_fanout

接口約束

set_load

set_drive

set_driving_cell

set_fanout_load

set_port_fanout_numberset_input_transitionset_input_delay

set_output_delay

特定模式和配置約束

set_case_analysis

set_logic_dc

set_logic_zero

set_logic_one

時序例外

set_false_path

set_multicycle_path

set_max_delay

set_min_delay

set_disable_timing

其他命令

set_wire_load_model

set_wire_load_mode

set_wire_load_selection_group

set_wire_load_min_block_size

set_units

set_operating_condition

sdc_version

SDC查詢命令

get_cells

get_ports

get_pins

get_nets

get_clocks

all_inputs

all_output

all_registers

all_clocks

get_libs

get_lib_cells

get_lib_pins

current_design

審核編輯:劉清

-

分頻器

+關注

關注

43文章

447瀏覽量

49884 -

SDC

+關注

關注

0文章

48瀏覽量

15534 -

時鐘信號

+關注

關注

4文章

448瀏覽量

28542 -

CLK

+關注

關注

0文章

127瀏覽量

17158

原文標題:一文了解下SDC約束怎么寫

文章出處:【微信號:處芯積律,微信公眾號:處芯積律】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

VIVADO時序約束及STA基礎

ETD第14期:SDR源同步接口時序約束方法

如何將Altera的SDC約束轉換為Xilinx XDC約束

調用timequest工具對工程時序進行分析

時序約束的步驟分析

時序分析基本概念—SDC概述

時序分析的設計約束SDC怎么寫呢?

時序分析的設計約束SDC怎么寫呢?

評論