在芯片功能驗(yàn)證中,仿真波形一直是調(diào)試的重要手段。通過觀測分析波形,工程師可以推斷代碼是否正常運(yùn)行,電路的功能是否正確,設(shè)計(jì)是否滿足預(yù)期。波形解決了芯片驗(yàn)證調(diào)試中可觀測性的問題,雖然單獨(dú)依賴觀測波形不足以解決調(diào)試的所有問題,但是波形是一個(gè)最基本的手段。很多FPGA和硬件設(shè)計(jì)工程師都將仿真波形看作是硬件調(diào)試的示波器或者邏輯分析儀。

數(shù)字電路中的波形通常由四值邏輯表示,包括:1 - 高電平,0 - 低電平, X - 不定態(tài),Z - 高阻態(tài)。

當(dāng)然,為了降低復(fù)雜度,有些仿真系統(tǒng)簡單地忽略不定態(tài)和高阻態(tài),僅使用二值邏輯表示。波形系統(tǒng)就是將仿真數(shù)據(jù)通過可視化的方式顯示出來。高級波形系統(tǒng)需要更多功能,包括對協(xié)議事務(wù)級(protocol transaction),混合信號(mixed signals),文本輸入輸出(File I/O)等功能的顯示。目前的大部分EDA廠商工具,都將波形系統(tǒng)都嵌入在各個(gè)仿真器和調(diào)試工具中,成為緊密結(jié)合的一部分。

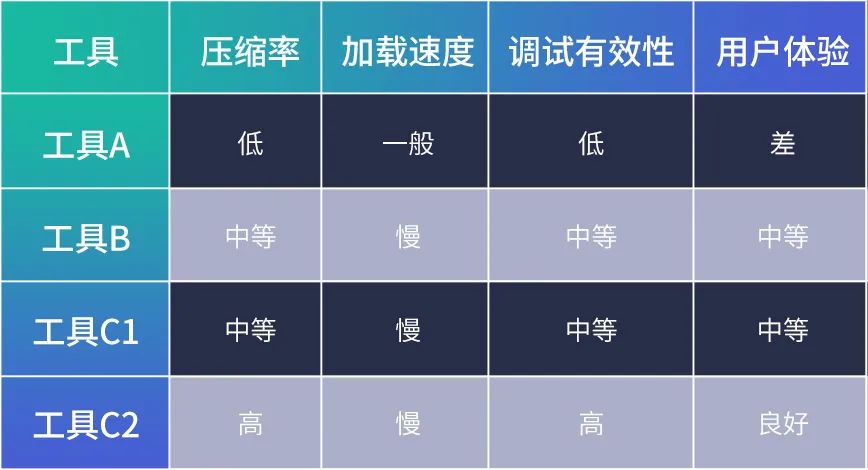

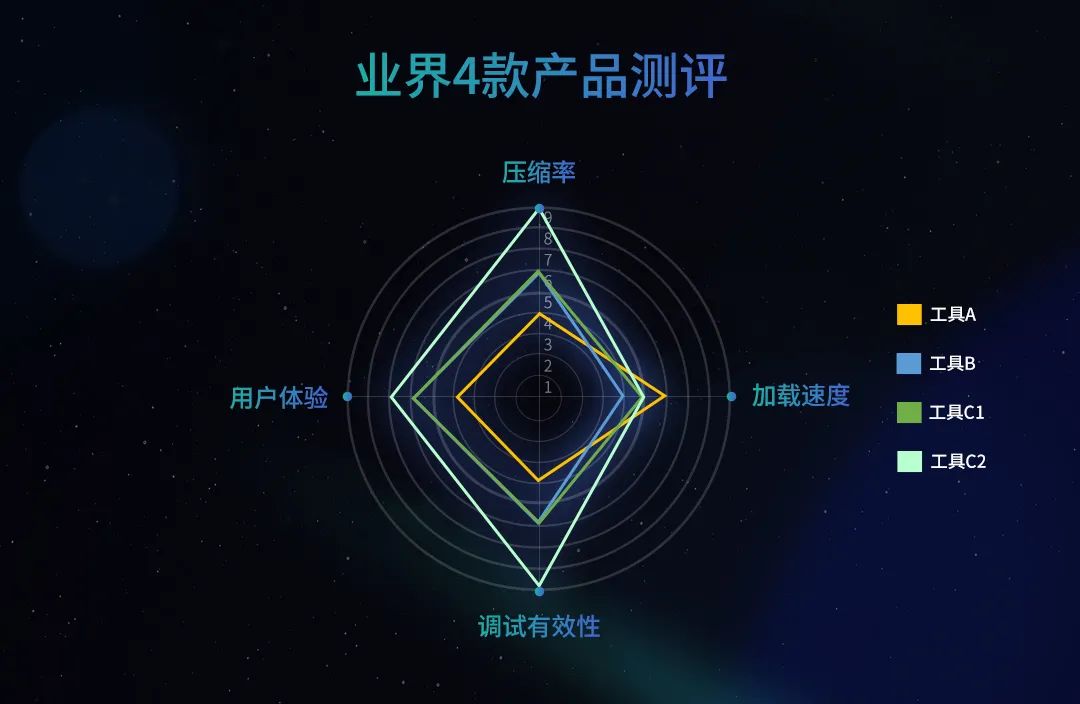

業(yè)界的有多種波形格式,除了VCD是一個(gè)公開的標(biāo)準(zhǔn)格式之外,其他商業(yè)性質(zhì)的各具特點(diǎn),在性能和功能上各有優(yōu)缺點(diǎn)。目前業(yè)界最普遍使用的是C2工具,它具有非常高效的數(shù)據(jù)壓縮率,用戶界面也非常友好,但是在大型設(shè)計(jì)上數(shù)據(jù)加載還是稍慢,底層優(yōu)化有待進(jìn)一步改進(jìn)。C1工具操作性稍顯復(fù)雜,人機(jī)界面的易用性還有很大的提升空間。B工具中規(guī)中矩,它和A工具在數(shù)據(jù)壓縮率上都不能和C2工具相比。下列表格列出各自的一些特性。

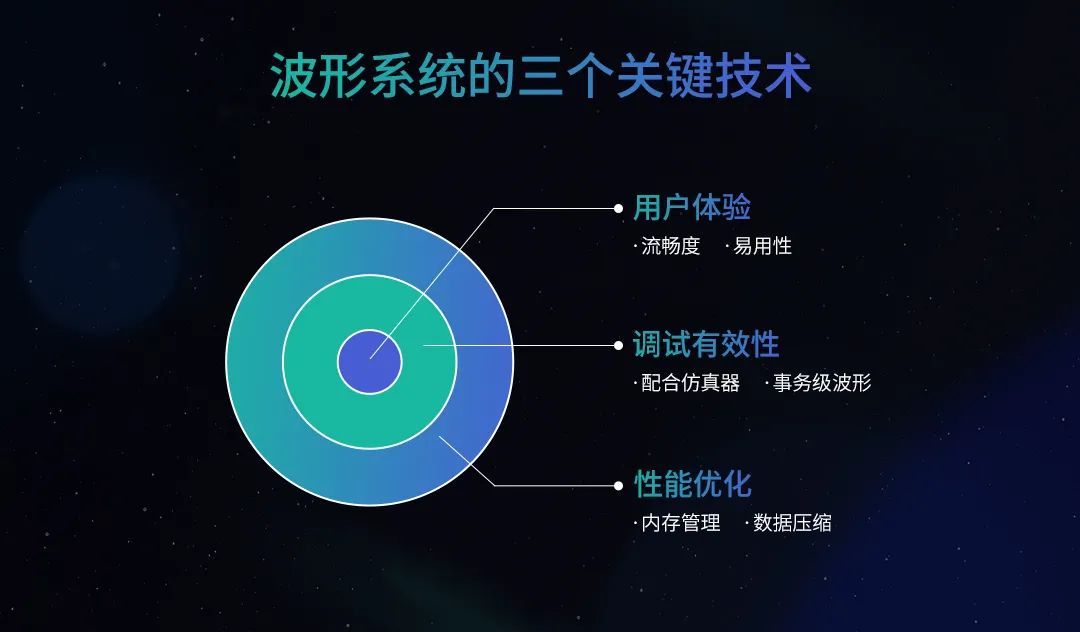

波形系統(tǒng)在芯片驗(yàn)證中至關(guān)重要,設(shè)計(jì)驗(yàn)證工程師在使用波形調(diào)試的時(shí)候,對EDA工具有很高的期待,也提出了很多具體的要求。本文將探討波形系統(tǒng)的三個(gè)關(guān)鍵技術(shù),通過這些具體的技術(shù)細(xì)節(jié)理解,工程師可以深入的了解波形系統(tǒng)的性能和易用性,以便將來選擇工具時(shí)做出更好的判斷。

一個(gè)IP可能包含著數(shù)千萬個(gè)的信號,這些信號隨時(shí)間產(chǎn)生的數(shù)據(jù)量是巨大的。如果在波形系統(tǒng)中不對數(shù)據(jù)進(jìn)行有效的壓縮,而只是簡單的隨時(shí)間來記錄波形數(shù)據(jù),這樣最終的數(shù)據(jù)量將是巨大的。即便在目前磁盤價(jià)格日益下降的今天,這樣的數(shù)據(jù)量對于一個(gè)復(fù)雜IP或者SOC的調(diào)試來說,這種大量的磁盤空間積聚也是無法接受的。一個(gè)巨大的波形不僅僅對磁盤空間產(chǎn)生各種挑戰(zhàn),最大的問題還在于當(dāng)調(diào)試器調(diào)用這些數(shù)據(jù)的效率。

業(yè)界比較通用的波形開放標(biāo)準(zhǔn)是基于VCD (Value Change Dump)格式的,這個(gè)格式是基于IEEE1364標(biāo)準(zhǔn)的,也就是VerilogHDL標(biāo)準(zhǔn)中定義的一個(gè)用文本方式存儲波形的數(shù)據(jù)格式。這種格式主要是記錄波形的名稱,對應(yīng)數(shù)值變化的時(shí)間點(diǎn),和數(shù)值變化量。他的最核心的思想是只在Value change(VC)的時(shí)候做數(shù)據(jù)和時(shí)間點(diǎn)記錄,而在沒有VC時(shí)候不做任何記錄。

由于它不用記錄每個(gè)時(shí)間點(diǎn)的波形數(shù)值,從某種意義上來說也有一定的數(shù)據(jù)壓縮效果。但即便如此,在一個(gè)復(fù)雜IP中產(chǎn)生的VCD文件尺寸也可能超過幾百GB,由于是文本數(shù)據(jù)格式,工具在讀取文件索引數(shù)據(jù)上效率也不高,因此,在大型設(shè)計(jì)中利用VCD做波形調(diào)試,會(huì)遇到很多性能瓶頸。

各大EDA商業(yè)公司都有自己的波形格式。雖然具體的標(biāo)準(zhǔn)都是私有的,但大致都是基于數(shù)據(jù)庫的方式來存儲和管理波形數(shù)據(jù)。這些數(shù)據(jù)不僅僅是存儲,還會(huì)進(jìn)一步地壓縮和優(yōu)化,以便減少磁盤開銷,并讓工具更有效地讀取和管理數(shù)據(jù)。由于波形是調(diào)試的重要工具,各大EDA廠家都有針對波形的壓縮技術(shù),對調(diào)試器的圖形波形界面都做了優(yōu)化,方便用戶的使用,最大程度提高調(diào)試的效率。然而,除了關(guān)鍵的壓縮技術(shù)之外,對工具來說還有一個(gè)重要的特性就是內(nèi)存管理技術(shù)。

一個(gè)調(diào)試工具的內(nèi)存管理技術(shù)決定了這個(gè)工具的可用性和易用性。在當(dāng)下大量數(shù)據(jù)交互的仿真技術(shù)領(lǐng)域,優(yōu)秀的內(nèi)存管理技術(shù)對工具而言至關(guān)重要。簡單的來說,內(nèi)存管理就是工具需要數(shù)據(jù)放置在磁盤或者內(nèi)存中尋求一個(gè)平衡點(diǎn),或最優(yōu)化的比率。

過多的數(shù)據(jù)放在磁盤,每次工具在加載波形時(shí)候會(huì)非常緩慢;過量的數(shù)據(jù)加載到內(nèi)存,會(huì)造成內(nèi)存爆炸,讓整個(gè)服務(wù)器運(yùn)行緩慢,從而也導(dǎo)致效率和用戶體驗(yàn)下降。

有個(gè)笑話,說某工程經(jīng)理特別要求工程師必須在中午12點(diǎn)開始加載波形調(diào)試,加載過程中內(nèi)存基本耗盡,服務(wù)器無法做其他事情,吃完午飯午休后,工具完成波形加載,工程師就可以看波形開始調(diào)試工作了,這樣就可避免時(shí)間浪費(fèi)。這個(gè)笑話雖然經(jīng)不起仔細(xì)推敲,但是它反映了某些工具在內(nèi)存管理上的缺陷和不足,會(huì)導(dǎo)致嚴(yán)重的性能問題和降低用戶體驗(yàn)。無論如何,一款好的調(diào)試工具都要解決或者避免這些問題。

除了上述提到的底層核心技術(shù)以外,對于波形工具技術(shù)本身來說,它必須具備幾個(gè)關(guān)鍵應(yīng)用層面技術(shù):仿真器的高效配合,以及場景級(scenario)和事務(wù)級(transaction) 操作類型的表示。雖然波形非常直觀地反映了設(shè)計(jì)內(nèi)部的信號變化,但是設(shè)計(jì)本身是RTL,而且是信號間有相互關(guān)聯(lián),因此調(diào)試不能僅僅依賴于觀測波形,很多時(shí)候工程師需要仿真器的配合讓調(diào)試變得更加有效。

RTL和測試平臺(testbenches)在運(yùn)行后,其實(shí)本身很類似通用軟件代碼運(yùn)行過程,很多工程師在觀測波形變化的時(shí)候也希望能了解代碼的執(zhí)行情況;同樣在代碼調(diào)試的過程中,很多時(shí)候需要理解代碼的執(zhí)行過程和相對應(yīng)的信號變化。這個(gè)時(shí)候?qū)Ψ抡嫫鞯膯尾絼?dòng)態(tài)調(diào)試可以配合波形變化,工程師可以直觀的了解某段代碼的執(zhí)行過程和信號變化。這種類似軟件單步調(diào)試的方式也是芯片驗(yàn)證中常用的手段之一。

信號驅(qū)動(dòng)追蹤(signal driver tracing)是一種常用的調(diào)試技術(shù),它通過某個(gè)信號查詢它的驅(qū)動(dòng)源頭。當(dāng)用戶在波形界面上發(fā)現(xiàn)信號在某個(gè)時(shí)刻出現(xiàn)問題后,用戶可以追蹤這個(gè)信號的驅(qū)動(dòng)源,這樣調(diào)試類似結(jié)果到原因(effect and cause)推導(dǎo)過程,大大加強(qiáng)了調(diào)試的有效性。通常信號的源頭可能不是單一而是多個(gè),用戶可以選擇在波形界面來觀測多個(gè)源頭,也可以通過仿真器和調(diào)試器的配合來選擇使用代碼或者電路圖(schematic)方式進(jìn)行觀測。這種信號溯源技術(shù)需要仿真器和調(diào)試工具的有機(jī)結(jié)合,底層也需要高效數(shù)據(jù)庫的支持。

事務(wù)級視圖(Transaction Viewer)。在復(fù)雜設(shè)計(jì)中大量的信號里厘清數(shù)據(jù)真實(shí)含義是非常困難的,用戶往往需要參考幾十個(gè)信號的量的變化來確定數(shù)據(jù)類型和操作。例如,一個(gè)AXI協(xié)議的讀寫操作涉及到的信號可能有20多個(gè)。完成一次讀寫需要用戶在一段時(shí)間內(nèi)觀測大量信號的變化,這種操作效率低下,不利于長時(shí)間的調(diào)試過程。Transaction viewer可在圖形界面提供更高層次的視角,讓用戶直觀地了解這些transaction的數(shù)據(jù)類型和定義,而不需要再從底層信號分析數(shù)據(jù)。有了這個(gè)工具,用戶可以快速分析調(diào)試數(shù)據(jù),包括enum type, class based transaction, sequence item等等。當(dāng)然,要實(shí)現(xiàn)一個(gè)transaction可視化,還是需要仿真器配合,以及代碼的一些額外工作,比如使用驗(yàn)證IP (VIP),或者使用SystemVerilog等高級建模語言描述。

波形工具和其他的驗(yàn)證工具不一樣,它是一個(gè)頻繁和用戶交互的圖形界面,這些交互體現(xiàn)在用戶的鼠標(biāo)鍵盤操作和對圖形長時(shí)間的肉眼觀測;和大多商業(yè)軟件或者移動(dòng)App一樣,這個(gè)工具需要用戶長時(shí)間操作和交互,用戶體驗(yàn)成為了波形工具至關(guān)重要的一個(gè)因素。用戶體驗(yàn)通俗來說就是工具的流暢度和易用性。加載波形的速度,波形窗口縮放的響應(yīng),代碼和波形相互對應(yīng)(cross-probing),波形比較與合并等,都可以看成是工具的流暢度的體現(xiàn)。

工具的流暢度,除了工具自身的優(yōu)化,主要還取決于上面談到的數(shù)據(jù)壓縮和內(nèi)存管理的優(yōu)化。一個(gè)好的波形工具應(yīng)該能讓工程師很快上手操作,而不需要花費(fèi)時(shí)間學(xué)習(xí)或培訓(xùn)。簡單的功能可以快速地通過菜單選項(xiàng)實(shí)現(xiàn),復(fù)雜的功能也可以開放數(shù)據(jù)接口,讓用戶編程操作。

上述談到的幾點(diǎn)其實(shí)都是相互關(guān)聯(lián)的。優(yōu)秀的性能可以保證工具的流暢度,而調(diào)試的效率也有助于提升工具的用戶體驗(yàn)。波形系統(tǒng)只是仿真調(diào)試工具中的一個(gè)部分,調(diào)試工具還有很多很多其他的核心技術(shù),比如代碼和電路圖調(diào)試等。但是觀測波形是驗(yàn)證工程師最常用的一種手段,作者希望通過介紹波形系統(tǒng)中的一些基本技術(shù)讓用戶將來選擇工具時(shí)更加有針對性。同時(shí)也希望驗(yàn)證工程師能利用好工具,提升工作效率。

-

FPGA設(shè)計(jì)

+關(guān)注

關(guān)注

9文章

428瀏覽量

26508 -

EDA工具

+關(guān)注

關(guān)注

4文章

267瀏覽量

31785 -

VCD

+關(guān)注

關(guān)注

0文章

37瀏覽量

34719 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1605瀏覽量

80578 -

調(diào)試器

+關(guān)注

關(guān)注

1文章

303瀏覽量

23716

發(fā)布評論請先 登錄

相關(guān)推薦

波形系統(tǒng)三大關(guān)鍵點(diǎn)解析

波形系統(tǒng)三大關(guān)鍵點(diǎn)解析

評論