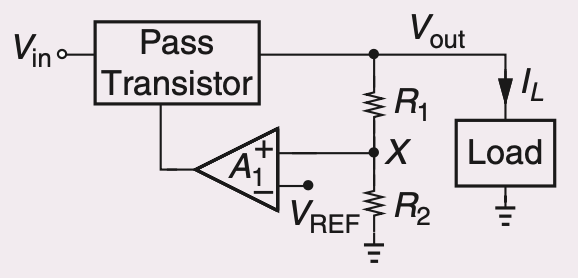

我們當然希望LDO的輸出準確、負載(電流)變化時能夠快速響應。

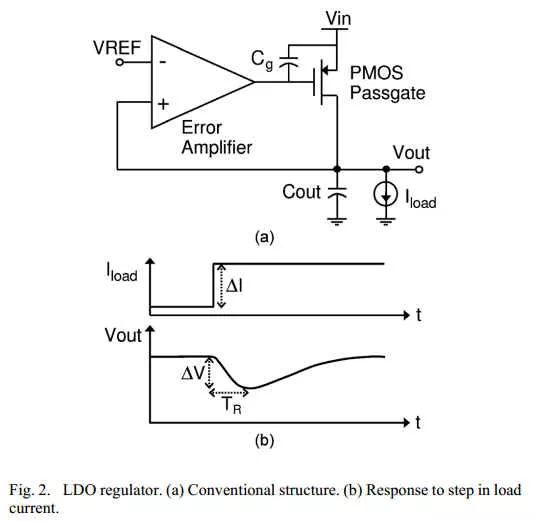

像圖2所示:

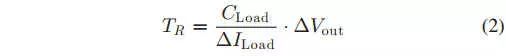

這是傳統結構,該結構的響應時間受限于feedback loop delay反饋環路延遲,即,當負載電流從空載到重載時,Vout上被Iload下拉,反饋環路要工作,防止Vout繼續下降,這段時間就是TR,叫做Load response time,這幾個變量之間的關系表示為:

如圖2(a)結構,我們常常要考慮環路的穩定性,從而限制了loop bandwidth,所以TR時間約1~3us。

保守設計decap電容1.46nF,△I為24mA,這么計算下來,要想△V在10mV以下,TR需要低于610ps。

-->10mV****的設計要求算是很苛刻了,比如我們實際上允許 0.1V ,那么TR計算約為 6.1us 。

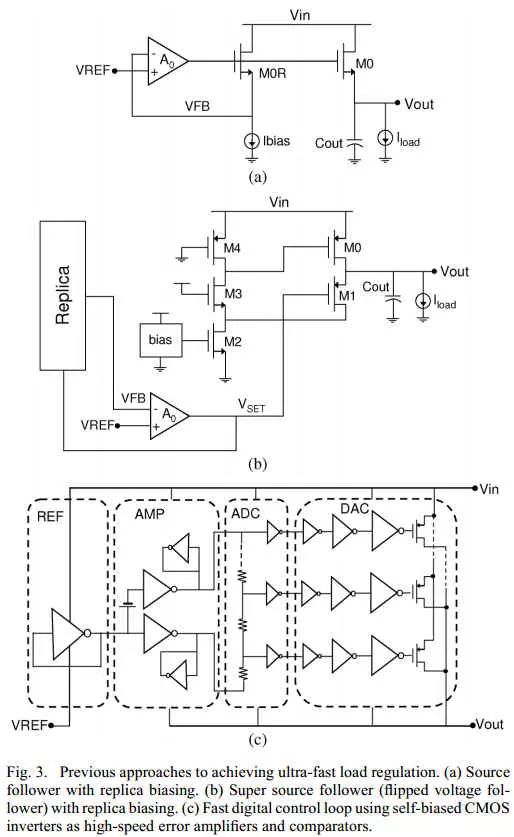

我們看有哪些方式可以實現ultra-fast load regulation。

圖 3(a) 原型來源于 2005 , Area-Efficient Linear Regulator With Ultra-Fast Load Regulation.

直接采用source follower(圖1(a))利用傳輸管M0源端的低阻抗特性達到fast load regulation,缺點是低電源電壓下,VG的headroom不夠。

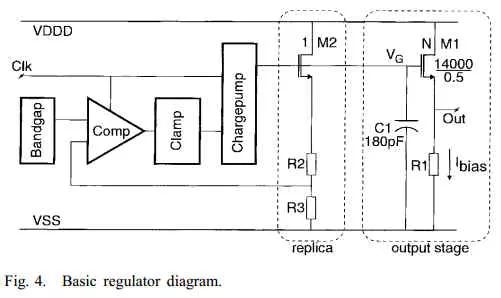

圖1(b)做了個charge pump提升輸出NMOS管的柵壓,這個M0R通路不去觀測VOUT輸出波形,load regulation只依賴于M0管的I-V曲線,90mV的△V對應于Imin和Imax比值約1:10.

這里又引用了 1998 Embedded 5V-to-3.3V Voltage Regulator for Supplying Digital IC's in 3.3V CMOS Technology 。

你覺得****C1 是什么作用? 180pF 。

比如這里要求輸出最大偏差±300mV=600mV。包含兩個部分1)control part; 2)輸出的variation。分配給前者200mV,后者400mV。而輸出400mV的偏差又來源于兩個部分,首先是取決于M1尺寸的Vgs偏差,其次是輸出OUT經M1的Cgs耦合后在VG上的偏差。

減小輸出節點到M1柵端的coupling。

C1和M1占據了整個LDO的面積,C1做的越大,VG上的ripple就越小。M1就可以不用做的太大;

C1做的越小,VG偏差大,留給M1的Vgs余量小,也就是說M1就需要做很大了。

這里C1和M1的面積存在折中。

200uA的偏置電流Imin,100mA的負載電流Imax,400mV最差動態偏差(140°C),那么就需要W/L位14000um/0.5um, C1為180pF。這個時候M1的柵端VG電壓為4.5V高壓,不過沒有關系,這是3.3V的工藝。M1采用最小尺寸,工作在Weak inversion區,最大化gm/I。The typical large-signal output resistance for these dimensions is about 3Ω。

這篇文章handle the maximum specified peak load currents針對的是負載電流的“峰值”。我們都知道Peak load currents in digital circuits can be much larger than the average current而峰值通常遠遠大于平均電流。

對于圖4電流,需要一個start-up circuit is required for pre-charging VG in order to initialize circuit operation.啟動電路來初始化輸出。

為什么使用 Replica Feedback ?

不直接去sense輸出電壓,而是復制了一個通路。版圖上,the replica transistor is located at the center of the output power transistor array.

"Replica"通路保證輸出工作在dc工作點附近,保證環路不直接受負載電流影響。

從圖5看出來,使用"replica"通路,紋波改善了一半。

這種結構的設計要點還包括:

- Charge pump

- Clamp

- Power-Down Mode

- Start-up circuit

再回到2005那篇 paper ,對super source follower結構的輸出阻抗的小信號分析,可以學習一下。

空載,偏置電流流過M4和M0,M2關斷,M0管流過small bias current。

當負載電流增大,VOUT電壓掉落,M4關斷,電流流過M2的源端,拉低M0的柵端電壓,使M0導通更多,電流從VIN到VOUT去補償整個droop。

這里不考慮CDIE情況下,輸出阻抗表現為單極點:

也就是說,the decoupling capacitor is not required to make the P-stage stable.

這里輸出阻抗可以建模為電阻R和電感L的串聯,其中:

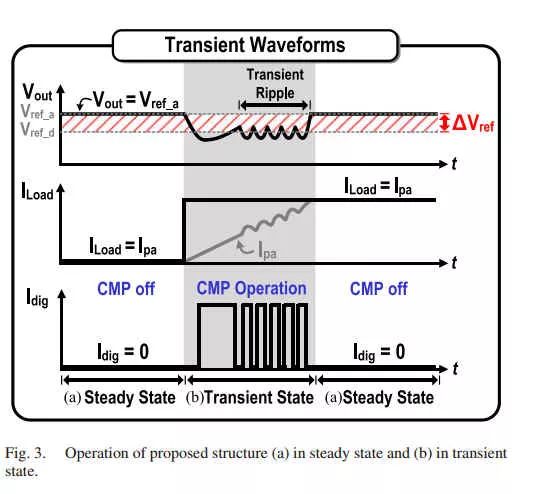

我主要想講的是圖 4 ,基于CMP比較器結構的 REGULATOR 。

在這里,the propagation delay of the comparator determines the load response time即,比較器的傳播延遲決定了所謂的負載響應時間。

然后這里又講了一個基于CMP結構的REG的缺點: self-generated output ripple 。

從圖4(a)和(b),a fast comparator is desirable not only to achieve a small value of TR but also because of its effect on the output ripple.比較器速度越快,負載響應時間TR越快,輸出節點紋波越小。

接下來說一下 Distributed Regulator System 。

比如在DDR3 I/O應用下,文章提取了Vout電源網絡的RC模型,如果只使用一個 REGULATOR ,在最大負載電流下, IR****上的壓降高到 24mV 。 采用了分布式設計,這個IR drop可以將位2.4mV。分布式設計/布局的另一個好處:power dissipated in the passgates is more evenly spread across the chip。

當然,這種分布式設計也是有問題的,叫做Load Sharing Problems.

后面的就是提出解決方案,Dual-loop結構。

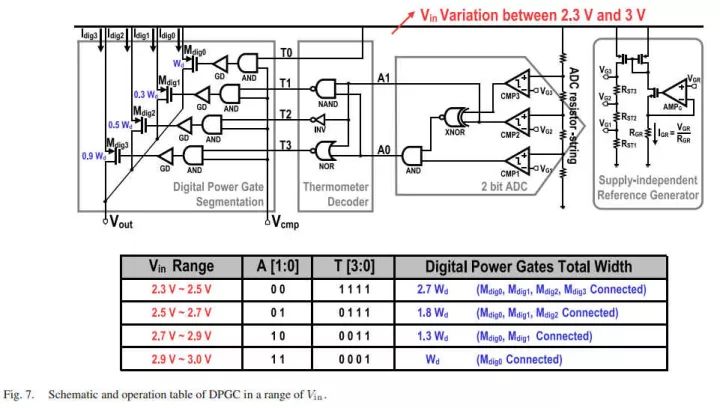

最后回到2018年的這篇針對于NAND里LDO設計的最新文章,可謂是非常有趣,而我只能讀懂一點點。。。

輸入電源電壓 2.3-3V , LDO**輸出 2.1V , 20ns響應150mA負載電流,輸出droop**為 225mV 。靜態電流功耗 81uA ,片上輸出電容 2nF 。

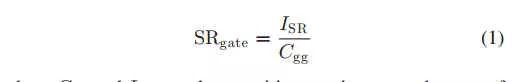

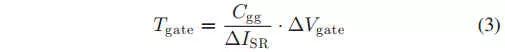

怎么去提高輸出傳輸管柵端的SRgate?

要么費功耗ISR,要么減小Cgg,不好弄。。。

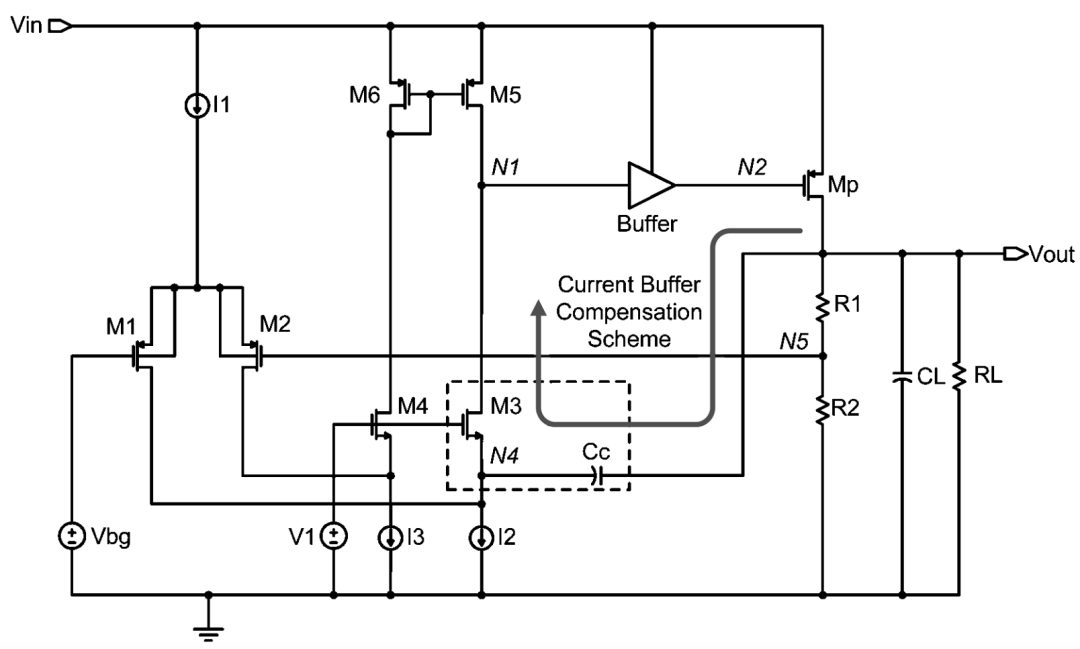

這里結合了基于AMP和基于CMP的LDO結構,提出了兩者結合的設想:

單單采用基于AMP結構,只能增加Ibias電流了,如果不然,像圖1(a)所示,Vout droop會很大;

單單采用基于CMP結構,雖然不存在穩定性問題,但是這個結構我們之前也從引用的文章里看出,他有自己固有的紋波;

兩個結構結合,基于AMP結構工作在穩態,保證精度;基于CMP結構提供快速的響應速度,在steady state下并不work,所以不存在intrinsic output ripple了,如圖3。

...In other words, CMP-based LDO assists AMP-based LDO to minimize ΔVout only during the transient state, in which AMP-based LDO does not yet regulate Vout...注意AMP和CMP工作區間以及這里△VREF。

雖然CMP在穩態時不工作,但是考慮到負載瞬態響應,我們需要把比較器的傳播延遲降到最小,不然的話,△Vout又增大了。

重新給出the duration time from the point at which Vout drops to that at which it stops is called the response time of Vout...TR的表達式:

基于AMP結構的LDO,我們當然期望傳輸管的Vgate能降到一定電壓,使MPa產生足夠大的電流補償Iload,Ipa快速的接近于Iload。

△Vgate是Mpa柵端的變化值。看圖4(a),TR=Tgate。

對圖4(b)來說,TR取決于CMP的傳播延遲和柵驅動電路gate driver。

Tdelay是ns級,比Tgate快多了。

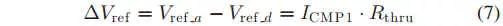

△ Vref****有什么用?

用來分立AMP和CMP的操作。

比如如果Vref_d和Vref_a非常接近,AMP和CMP同時工作,就會帶來前面講的intrinsic output ripple。為了防止CMP的self-oscillation,這里選擇△Vref should be larger than the magnitude of transient output ripple in order to ensure that CMP does not respond to Vripple in the steady state...AMP和CMP基準電壓比較點的差值△Vref至少大于輸出的紋波Vripple。

圖5是結構非常復雜的LDO整體圖。

這種高端的方式怎么去確定△ Vref****的值?這個值太大或太小有什么問題?

ICMP1取10uA,10uA電流通過7kΩ電阻,產生的壓降是70mV;反之,開關全閉合后,電阻為0,見圖5左下角表格。

圖6告訴我們△Vref的calibration和AVC的實現方式。

1->首先,B[0]~B[2]默認值111,△VREF最大70mV,將AMP和CMP兩種方式明顯隔開;

2->△Vref calibration開始,Vref_d從最接近Vref_a的配置000開始,比較器開始bang-bang控制,△Vref控制單元去記Vcmp的震蕩周期,每64個周期的下降沿產生一個短脈沖Vup。B[0]~B[2]呢,在Vup脈沖處加1,直至Vref_d離Vref_a夠遠,CMP環路不再工作,Vcmp的震蕩也結束,這就是...the minimum value at which the operation of CMP-based LDO can be separated from that of AMP-based LDO in the steady state...兩個環路基準電壓比較點的最佳差距。

由于電源電壓變化范圍在2.3V~3V,Idig變化范圍也很大。圖5中的DPGC電路通過控制Mdig的尺寸大小提供不變的Idig電流。

圖7給出DPGC實現線路:

2位ADC檢測電源電壓Vin水平,輸出結果經溫度編碼控制Mdig的尺寸。

工作在CMP模式下的Mdig處于線性區,應用線性區的管子工作I/V關系式和VIN/VOUT值可以理論計算Mdig的尺寸。

按照修正的式(10)進行理論計算,跟仿真非常接近。

-

NAND

+關注

關注

16文章

1681瀏覽量

136121 -

比較器

+關注

關注

14文章

1650瀏覽量

107185 -

電源電壓

+關注

關注

2文章

989瀏覽量

23969 -

LDO電源

+關注

關注

0文章

62瀏覽量

10449 -

NMOS管

+關注

關注

2文章

121瀏覽量

5407

發布評論請先 登錄

相關推薦

LDO的參數指標分析(1)

NAND里的LDO設計

NAND里的LDO設計

評論