GRE是Global Route Environment的縮寫,中文意思為全局布線環境,運用具備階層化意識的全面繞線引擎與圖形式互連流程規劃程序。通GRE技術在短時間就可以開發出包含眾多互連總線與芯片引腳數的復雜且高速的設計組件。此外,運用GRE技術后便于工程師實現更佳的功能密度與系統效能最大化。Cadence這項系統互連設計解決方案,為PCB設計人員提供智能型規劃和繞線的環境,節省大量的時間、增進功能密度并提升效能,同時也大幅降低成本。

01

GRE布線規劃模式

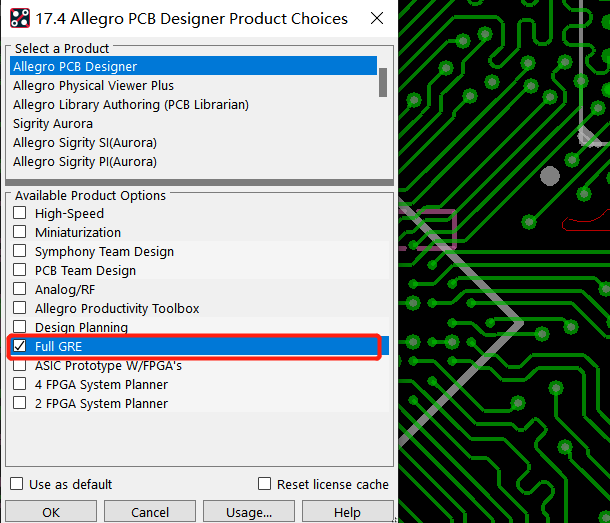

GRE提供不同的Options選項,來應對不同的設計要求,全功能的GRE功能要在Allegro啟動的時候勾選Full GRE才能實現,或者通過File菜單--Change Editor選項進行切換后勾選Full GRE復選項后才能實現。如下圖1所示。

圖1 全功能的GRE功能啟動

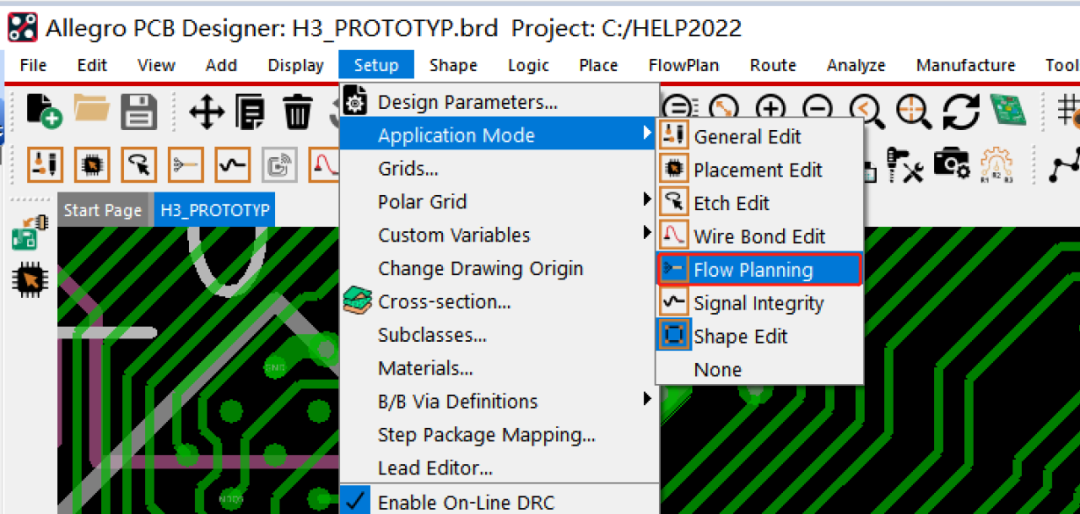

進入Allegro界面之后,想要啟動GRE首先要選擇GRE的功能模式,然后在Allegro的界面中選擇setup菜單--Application mode--Flow Planning命令切換到該模式才能實現布線GRE規劃。

圖2 模式切換到Flow Planning

02

GER的參數設置

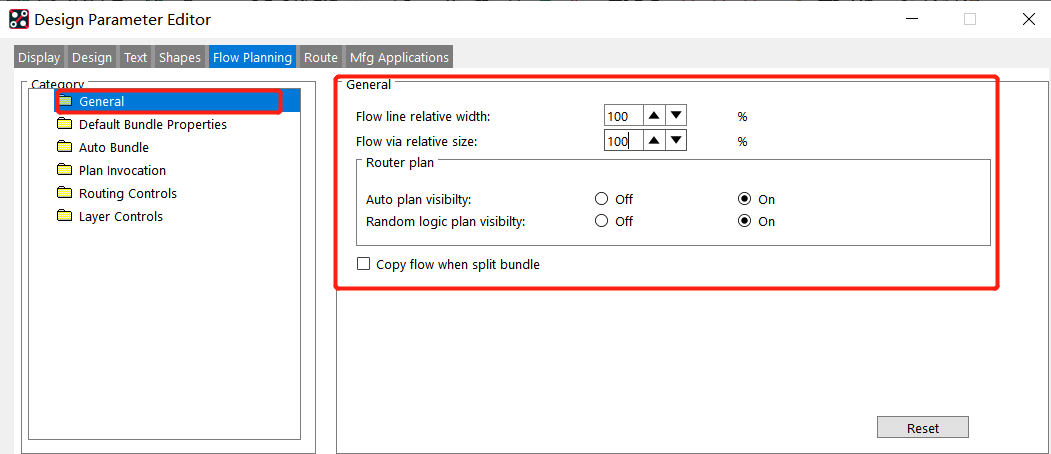

GER參數設置在Setup菜單--Design Parameter命令下的Flow Planning選項卡中。在General選項組里面,可以在設置Flow-line relative width文本框和Flow via relative size文本框中設置比例比例,用來定義一組飛線抽象成Bundle或者Flow后的寬度和過孔大小。如下圖4和5所示。一般設置成100-150%為宜,或者根據自己的經驗和板子上線的密度來定義。該參數對Bundle和Flow的設置全局有效,在該處的修改,對所有的Bundle和Flow都有效。

圖3Flow Planning General選項卡

?

?

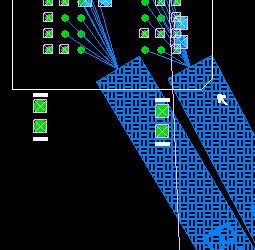

圖4 100%的顯示效果

圖5 200%的顯示效果

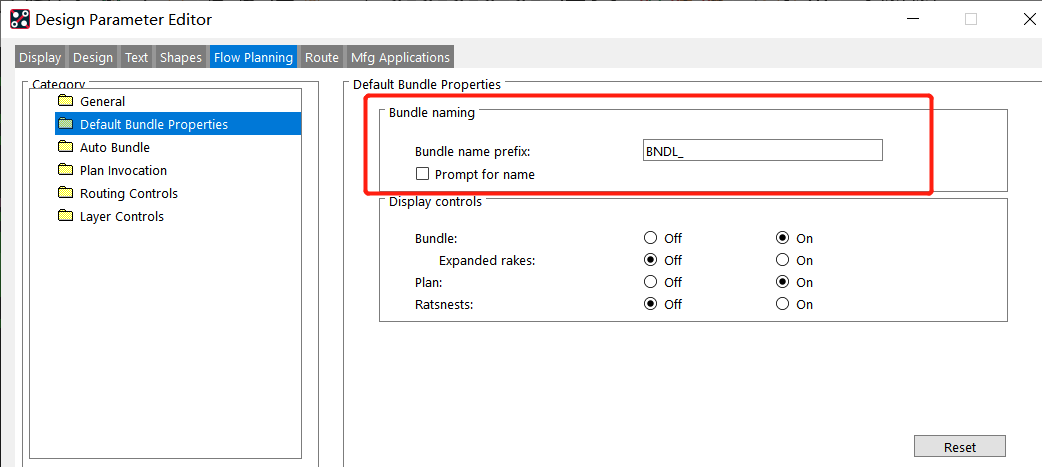

Bundle的命名規則也是可以修改的,可以針對單獨的Bundle來設置特殊的名字,點擊就能進行編輯操作。Bundle的命名設置功能有限,修改了規則只對以后新建立的有效,之前的無效。如下圖7所示。點擊Show Element命令可以查看Bundle的名稱如下圖6所示。

圖6Bundle的命名規則修改

關于Expanded Rakes選項,若該選項設置成Off,飛線的顯示是經過軟件優化過的,該模式下連接線很順暢且不存在交叉的情況,但這并不是真實的情況,它只是表明了元件和元件之間有多少飛線。若設置成On,元件和元件之間的飛線顯示的將是真實的連接關系,能看到飛線是否存在交叉不順暢的問題,建議將該項設置成On以便于對元件的布局進行調整。

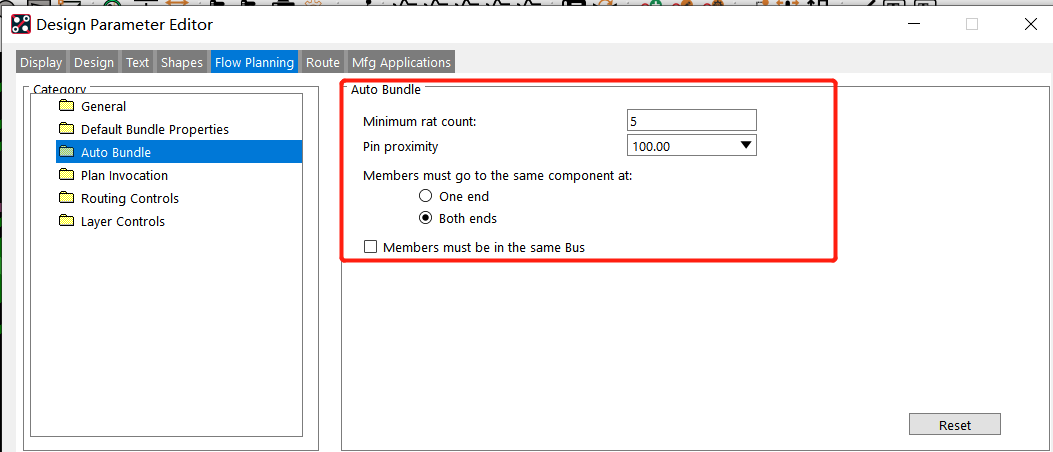

Auto Bundle的設置選項頁,用來定義自動創建Bundle時一些參數的配置,具體如下。

(1)Minimum Rat Count文本框用來定義一個Bundle最小飛線數量,默認是5,表示具備5根以上的飛線時系統才會自動創建一個Bundle。

(2)Pin Proximity文本框用來定義同一個Bundle的Pin引腳之間的最遠距離,只有在該距離之內的飛線,系統才會自動創建一個Bundle。

(3)Members must go to the same component單選框用來定義組成Bundle的飛線是否要同屬一個元件。One end單選項定義屬于同一元件網絡,Both ends單選項定義屬于不同元件網絡。

(4)Members must be in the same bus復選框用來定義組成Bundle的飛線是否屬于同一組總線。勾選后自動創建的Bundle會屬于同一個總線。如下圖7所示。

圖7Auto Bundle的設置選項

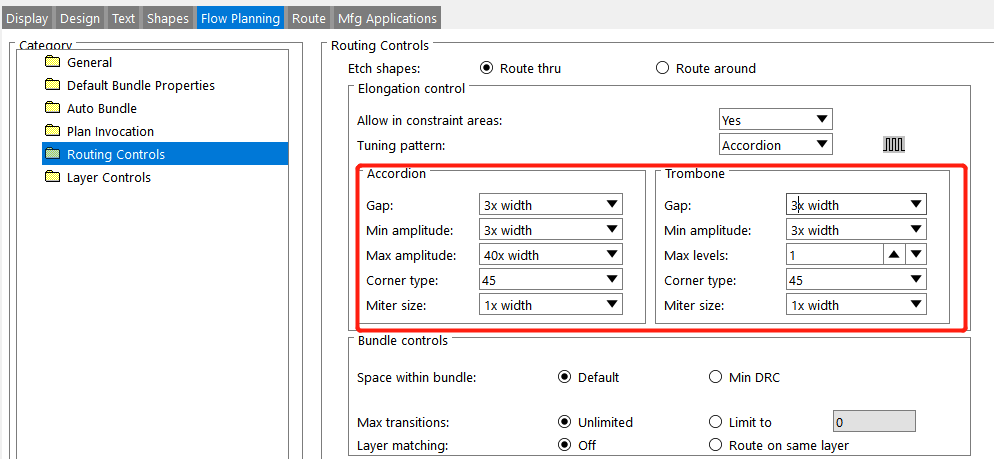

Routing Controls是布線參數的設置,設定繞線蛇形線布線的間距、和線之間的距離,線的轉角,最小的間距等參數。

圖8 Routing Controls布線參數設置

下期預告:實例講解 | GRE的處理辦法

通過4片DDR3中的1片為實例進行講解,在Allegro中GRE處理的基本元素就是Bundle,詳細講解如何手動創建、自動創建、通過規則管理器來創建Bundle,并且編輯管理Bundle的詳細操作。

教大家如何運用全局布線GRE規劃應用技術提升智能繞線規劃增強高密度PCB的設計效率。

-

布局

+關注

關注

5文章

269瀏覽量

25023 -

allegro

+關注

關注

42文章

657瀏覽量

145252

發布評論請先 登錄

相關推薦

通信開關電源參數設置方法

變頻器參數設置技巧介紹

德力西變頻器恒壓供水參數設置步驟

恒壓供水變頻器參數設置方法

金田變頻器怎么調參數設置

s120編碼器參數設置在哪里

松下伺服參數設置步驟

變頻器的基本參數設置

頻譜分析儀的參數設置方法

東元驅動器參數設置步驟及注意事項

變頻器常用參數設置技巧與指南

技術資訊 | 全局布線GRE規劃應用及參數設置

技術資訊 | 全局布線GRE規劃應用及參數設置

評論