IC片上保護設計對EOS的影響

全面的方法可以減少與EOS相關的故障

通常理解的是,芯片上ESD保護是必不可少的,以滿足人體模型(HBM)和充電裝置模型產品合格(CDM)ESD應力的可靠性要求。由工業委員會確定的ESD目標水平的當前最低安全水平(在IC行業中已廣為接受),對于HBM為1kV,對于CDM為250V,在成熟技術中具有良好的ESD設計實踐,可以提供更高的水平以確保更高的利潤。

盡管這是理想的,但在某些問題上,過高的ESD設計水平可能會導致設計良好的ESD電路在更長的時間內承受過電流,從而使其更易遭受持續時間短暫的瞬態感應EOS事件和意外損壞。同樣,如果不遵守適當的規則,處理閂鎖事件中的過電流的設計也會對EOS產生一些影響。

本文簡要回顧了這些問題,以說明強大的ESD保護不能保證IC設計免受意外EOS影響。它還總結了各種IC設計應用和相應的ESD設計方法,這些方法應說明任何不必要的EOS損壞情況。

ESD設計窗口

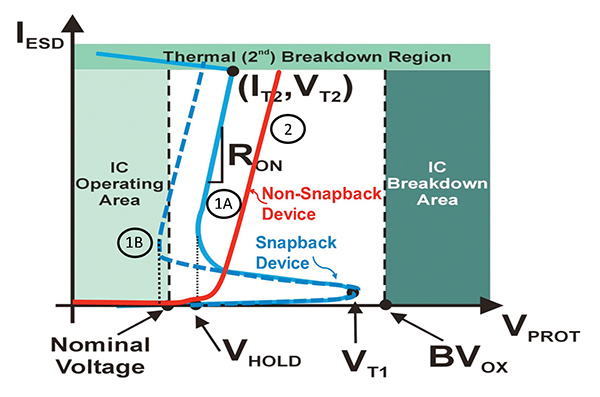

首先,必須確保ESD保護設計嚴格用于實現能夠保護所需的組件級HBM和CDM目標級別,同時又不對與柵極氧化物相關的功能和/或IC引腳可靠性產生任何負面影響的最佳電路,結或互連損壞。ESD工作區稱為“設計窗口”,如圖1所示。

圖1:ESD保護策略的典型設計窗口

任何ESD設計均受IC工作區域,IC可靠性區域以及保護鉗定義的熱效應的限制。因此,設計人員選擇合適的ESD器件,電路器件,并包括可以實現該目標的任何限制電阻。保護設備的觸發電壓(V t1)定義了它設計為導通的電平;觸發后的保持電壓(V Hold)是指應高于施加電壓的鉗位電平。最后,I t2是指ESD故障電流水平。圖1中常用保護設備的選擇是:

如藍色曲線(1A或1B)所示,NMOS晶體管在觸發點V t1處進入雙極擊穿(npn),并迅速恢復為稱為V Hold的保持電壓,并保護高達故障電流I ESD對應于ESD目標水平。(I t2,V t2)是指保護設備可能燒壞的散熱點,因此該I t2必須大于I ESD目標電流水平(例如,目標1.5 kV HBM的電流為1 Amp)。如果保護設備的導通電阻(R on)太高,則V t2也可能達到可靠性電壓極限。鉗位電路必須有效觸發,以使其電壓累積不超過柵極氧化層擊穿電壓(BV ox)或晶體管擊穿電壓。晶體管的V Hold經過設計,使其具有一定的工作電壓裕度,如曲線1A所示。相反,在具有V Hold的快速恢復裝置小于工作電壓(曲線1B)的情況下,存在EOS損壞的風險。

圖1中的第二個選擇也可以是非突跳設計,其中鉗位器調諧并傳導電流,如紅色曲線2所示。有兩種器件和電路技術都可以應用于傳統的突跳器件來產生這種情況。行為。

另一個選擇是pnpn器件,它以相似的V t1觸發,但具有更低的V Hold(等于或低于曲線1B所示的V Hold,因此要小心,以免在電路工作期間意外觸發)。如果將此pnpn器件放置在VDD引腳上,則非常危險,因為很可能會意外或意外觸發。本質上,ESD設計人員僅專注于ESD電池和通過組件的保護路徑。具有較低的V Hold的ESD優勢會帶來EOS風險,這是一個折衷方案:如果在正常操作期間觸發ESD電池,則存在無法關閉ESD電池并會傳導大量電流的高風險。持續時間比設計的時間更長。

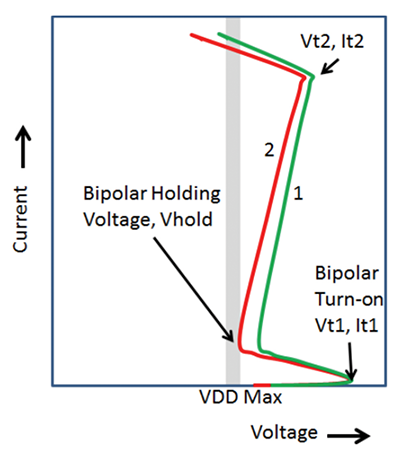

盡管通常ESD保護的設計并非旨在防止EOS事件,但根據特定的應用和操作,上述器件的ESD保護的IC 設計風格確實可以影響EOS損壞導致的故障率。環境。圖2說明了兩個不同的驟回設備,其中設備1與設備2的設計相比相對安全。設備2的EOS風險增加是由于V Hold參數低于最大允許VDD。雷卯電子可以提供ON CHIP ESD design 服務。

圖2:避免EOS損壞的快照設計

閂鎖和EOS

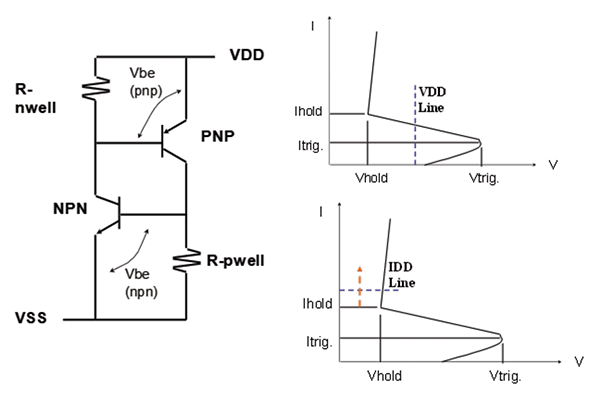

如前所述,如果不采取適當的預防措施,pnpn設備對于EOS可能會出現更多問題。圖3說明了這種容易產生EOS的ESD設計操作。此類設備的V Hold必須高于V dd或I Hold(將其保持在閂鎖模式所需的電流)要大于電源Idd電流。有一些設計方法可以實現此目的,以防止意外閂鎖導致EOS損壞。在保護設備類型錯誤(例如電源引腳上的pnpn)的情況下,已經觀察到EOS損壞。

圖3:PNPN ESD保護設備的設計操作顯示了EOS的脆弱性

即使設計人員真誠地進行了照顧,但如果OEM廠商通常沒有就應用中的實際電壓尖峰水平向他們進行咨詢,也會出現問題。因此,在某些意外情況下,可能會導致EOS損壞。此外,此外,某些涉及觸發電壓和保持電壓的設計風格可能會對整個系統產生更大的影響。因此,設計者只能防止客戶指定的應用程序需求引起的那些事件。

在根據JEDEC閂鎖規范(JESD78)進行閂鎖可靠性測試期間,如果不了解某些條件,則IO引腳上可能會發生EOS損壞。如果IO引腳具有高輸入阻抗,則電壓(在注入電流以測試閂鎖時)可能會積聚得足夠高,從而在達到測試所需的閂鎖極限之前,在意想不到的路徑上造成結擊穿損壞。這會造成不必要的EOS損壞,從而引起一些客戶誤解。在即將發布的文檔修訂版中,對JEDECJESD78測試方法進行了更好的描述,以避免這種錯誤的評估。

高速設計

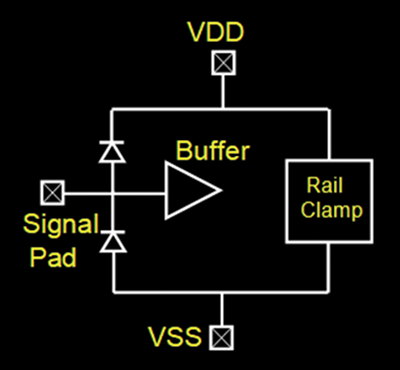

代替在IO引腳上鉗位器件的方法,用于大型數字IO環組的一種常用設計風格(參見圖4)是“軌鉗位”VDD保護設備,其中MOS保護設備在“正常工作”線性和飽和區域中工作在ESD事件傳導期間,器件不會發生雙極性擊穿。它包括一個有源MOSFET作為VDD和VSS之間的鉗位器件,其特性如圖1中的紅色曲線所示。即使在這些情況下,如果設計不能正確解決某些情況,EOS損壞也可能成為問題。例如,在正常應用期間,電源上出現的IO轉換引起的“dv/ dt”壓擺率可能會導致該設備進入電流傳導模式。

圖4:用于ESD保護策略的非快速回彈鉗

第二個考慮因素是需要先進技術的高速應用程序的數量不斷增加。通常,調整工藝技術以減輕ESD設計對EOS的意外損壞是不可取的,因為該技術針對IC應用,速度性能和產品規格需求進行了優化。ESD設計在技術表征期間進行,并在技術成熟后逐漸成熟。因此,由ESD設計人員或IO設計人員(有時由兩者)解決由特定ESD保護設計方法引起的任何EOS問題。

片上系統設計

另一方面來自使用多個電源電壓電平的片上系統(SOC)設計。在這些情況下,電源排序通常會成為任何意外觸發的內部二極管的問題。這些二極管會在順序轉換期間消耗大量功率,從而導致EOS損壞。芯片(尤其是具有多個電源域的SoC)的設計越復雜,存在意想不到的寄生路徑的可能性就越大。除非遵循仔細的設計技術,否則可能會導致EOS損壞的退貨。因此,SOCESD保護設計必須考慮到這一點。

高壓與低壓ESD設計

有人可能會認為,施加電壓越低,器件對ESD和EOS問題的敏感性就越高。相反,如果遵循謹慎的策略來保護薄柵極氧化物和晶體管較低的結擊穿電壓,則可以安全地為ESD設計低壓器件。唯一的例外可能是由于高速應用而降低了ESD目標水平。一旦設計用于ESD,它們的EOS問題就相對不那么普遍了。

另一方面,高壓應用經常使用SCR型保護器件。盡管這些器件提供更高的ESD保護級別,但同時它們的設計窗口通常更窄(最大工作電壓和IC擊穿區域之間的開銷較小),并且幾乎總是使V Hold遠低于最大工作電壓。在非ESD條件下觸發這些設備可能會導致EOS事件。

要考慮的另一方面是,與使用低壓設備的保護設計相比,使用高壓設備的保護設計在開啟模式下具有更高的功耗。這樣,當設備無法保護或ESD設備本身發生故障時,可利用更多的能量在故障區域造成材料損壞。EOS損壞與設備設計所處的工作電壓或環境之間存在一些相關性。有一些設計建議可以緩解這些情況[1]。

絕對最大電壓(AMR)和EOS

如行業委員會關于EOS的白皮書[1]所述,遵循AMR指南對于避免EOS損壞至關重要。ESD保護設備可能會超過AMR,但這僅在短暫的觸發瞬變期間(在ESD操作時序持續時間內),并且不會造成傷害。但是在持續施加電壓較長的情況下,超過AMR是危險的。

但是,應注意的是,隨著柵極電介質更薄的發展,進一步的技術進步和新穎的晶體管工藝技術將降低擊穿電壓,并繼續縮小設計窗口。擊穿電壓的這種降低直接轉化為AMR電壓的降低,并且隨后可能開始影響表現出EOS損害的PPM返還率。

客戶與供應商溝通

總之,如果不遵循適當的保護設計技術和預防措施,ESD設計風格可能會導致EOS損壞。對于實施的任何保護設計選擇,ESD設計人員都必須了解特定引腳的應用,對EOS的任何潛在影響,并注意任何其他注意事項。

通過適當的預先通信可以避免許多EOS損壞。客戶必須告知設計人員有關的應用電壓范圍,任何可能的電壓過沖和下沖等。供應商必須對ESD保護鉗的觸發電壓和保持電壓有足夠的了解,在最大工作電壓和擊穿電壓之間要有足夠的裕度,并選擇在“ESD設計窗口”安全操作區域中起作用的夾具,等等。

-

ESD

+關注

關注

48文章

2030瀏覽量

172933 -

EOS

+關注

關注

0文章

123瀏覽量

21182

發布評論請先 登錄

相關推薦

顯示器視頻接口的ESD保護器件選擇指南

ST NPI 新上架產品【ESDA5WY】Datasheet

ESD保護電路POWERclamp原理

TWS 藍牙耳機 ESD EOS保護方案

優恩半導體推出一系列適用于高速數據信號ESD和EOS的保護器件

ESD對電子元件的影響 如何選擇ESD保護元件?

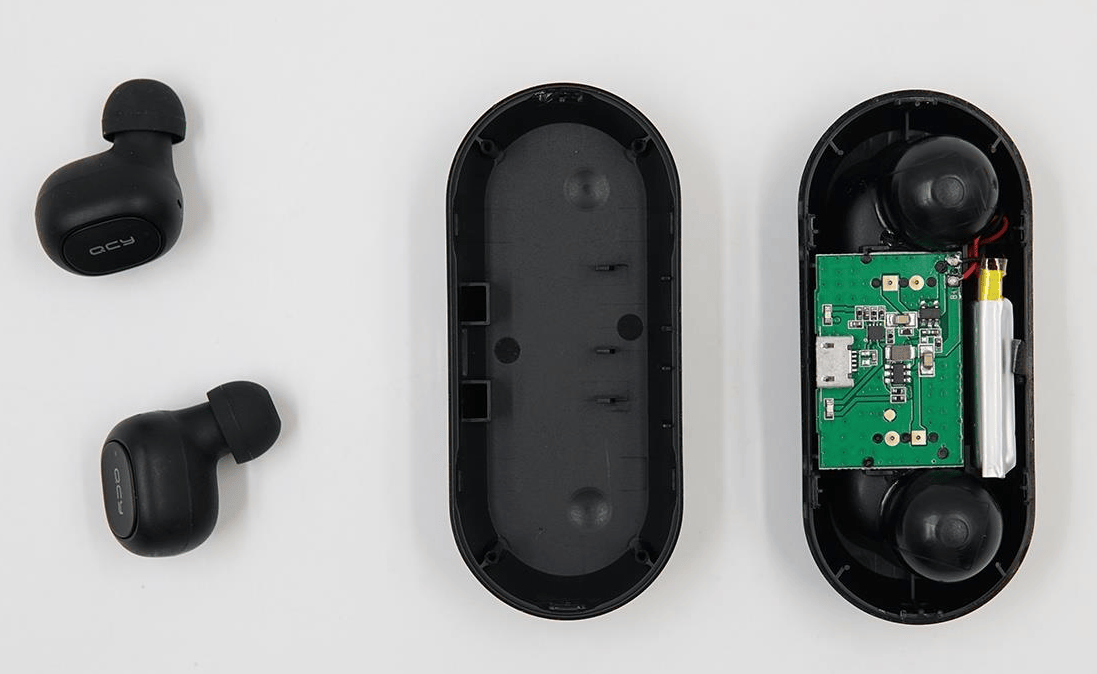

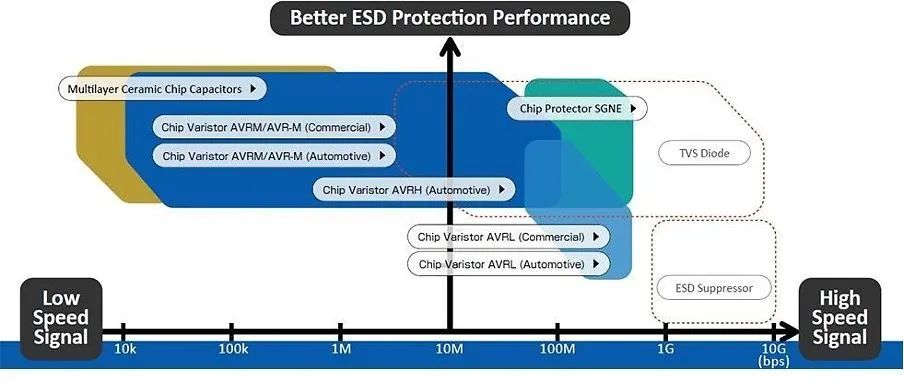

TDK | 如何選擇ESD保護元件?

On chip ESD和EOS保護設計

On chip ESD和EOS保護設計

評論