從低功耗實時監視到具有用于人機界面 (HMI) 的多屏圖形顯示的高級多媒體應用,汽車、工業、機器人、樓宇控制和其他關鍵 嵌入式系統應用預期需要承擔更加多樣化的工作負載。在滿足這些廣泛的功能要求的同時,它們還必須能夠支持嚴格的安全標 準,降低成本,減少占用空間以及優化功耗 / 性能平衡。

迄今為止,為滿足這些有時往往相互沖突的要求,開發人員不得不犧牲功能,或增加必要的設備來支持特定的圖形、安全性和 安全等要求,導致設計和制造的復雜性增加。開發人員真正需要的是一種單一的解決方案,能夠跨眾多關鍵的嵌入式系統應用 支持各式各樣滿足上述要求的產品。

本文將簡單介紹關鍵嵌入式系統設計的演變過程。然后展示如何使用 NXP Semiconductors 專門設計的多核應用處理器來應對 開發人員面臨的挑戰,這些處理器可以支持快速擴展的需求列表,包括眾多功能性和安全認證能力。

嵌入式系統設計的演變過程注意事項 嵌入式設備在支持一組有限的系統功能方面的傳統角色,在很大程度上已經被可提供廣泛功能的設備的需求所取代。例如,在 工業應用中,智能工具和設備對于增強型 HMI 功能的需求要求處理器能夠在滿足更多傳統工業實時要求的同時,提供優化的 圖形。同樣,汽車應用向包含功能域集群和網關的分層架構發展的趨勢,推動了能夠完全滿足這些要求的處理器的需求(圖 1)。

圖 1:朝著更加層次化的汽車系統架構發展的趨勢創造了對集成度更高的可擴展處理器解決方案的需求。(圖片來源:NXP Semiconductors)

在每個功能域中,對于更復雜功能的需求不斷提升性能和集成功能的門檻。例如,平視顯示器的出現需要能夠確保向駕駛員持 續提供關鍵圖形信息的解決方案。除了這些新一代的顯示器之外,增強駕駛員感知能力的需求與日俱增,也對攝像頭接口以及 高性能地執行能夠提供睡意檢測功能的高級識別軟件提出了更多的要求。

隨著應用的持續發展,為滿足日益多樣化的要求,同時最大限度減少設計的占用空間并降低成本和復雜性,對于高度集成的可 擴展解決方案的需求也變得更加迫切。利用 NXP 的 i.MX 8 系列應用處理器,開發人員可以將兼容的處理器平臺與一系列必要 的功能和性能相結合,來支持各種各樣的應用需求。在 NXP 的 i.MX 8 家族中,i.MX 8X 系列滿足了中端汽車和工業應用所需 的安全認證處理器的新興需求。

多核架構管理多樣化的工作負載 開發人員在實現用于汽車和工業應用的設備時所面臨的一大難題是過寬的需求廣度。在開發人員預期處理實時或高級應用處理 工作負載的情況下,對智能子系統的需求卻將這些截然不同的計算類型合并到一起。開發人員越來越需要能夠在支持功能安全 要求的同時提供可靠的實時響應和高性能應用執行的解決方案。

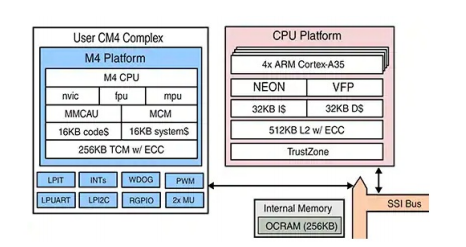

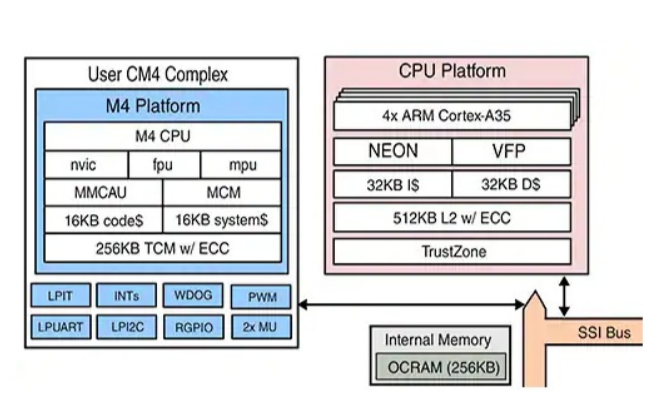

NXP i.MX 8X 系列處理器可提供實時功能、高性能處理,而且功耗很低,可充分利用復雜的多核中央處理器 (CPU) 架構來管 理多樣化的計算工作負載(圖 2)。

圖 2:NXP i.MX 8X 系列使用由 Arm Cortex-M4 (CM4) 嵌入式處理器和多個 Arm Cortex-A35 應用處理器構成的多核架構來支 持混合軟件工作負載。(圖片來源:NXP Semiconductors)

對于通用型實時處理任務,i.MX 8X 器件包括一個帶浮點單元 (FPU)、內存保護單元 (MPU)、內存映射加密加速單元 (MMCAU) 和混合控制模塊 (MCM) 的 Arm Cortex-M4 (CM4) 處理器。為了支持傳感器和致動器等外部外設,此用戶 CM4 復 合體將嵌套向量中斷控制器 (NVIC) 與一套全面的接口和模塊相結合,包括低功耗周期性中斷定時器 (LPIT)、脈沖寬度調制 (PWM) 以及在汽車和工業應用中通常需要的其他功能。一對高速緩存存儲器和具有糾錯碼 (ECC) 功能的緊耦合存儲器 (TCM),有助于最大限度減少對外部存儲器的訪問,加快執行速度和處理存儲器錯誤。

為了快速執行應用工作負載,該 CPU 平臺由多個高能效的 Arm Cortex-A35 應用處理器 (AP) 構成,其中兩個 AP 在 8DualXPlus 處理器(例如 MIMX8UX6AVLFZAC)中,四個 AP 在 8QuadXPlus 處理器(例如 MIMX8QX6AVLFZAC)中。 除了專用指令 (I$) 和數據 (D$) 高速緩存外,該 CPU 平臺還包括帶有 ECC 的 512 KB 2 級 (L2) 共享高速緩存。

該架構的 Arm Cortex-A35 內核可提供軟件兼容性和性能可擴展性,從而支持 32 位向后兼容性和 64 位性能。為了進一步加快 計算密集型算法(如信號處理和機器學習)的執行速度,Arm Cortex-A35 處理器提供了矢量浮點 (VFP) 處理和 Arm 的 Neon 單指令多數據 (SIMD) 架構擴展。為了加快用于圖像處理、計算機視覺和機器學習的軟件的執行速度,Arm 計算庫提供了經優 化適用于 Arm 處理器和圖形處理單元 (GPU) 架構的函數,而開源代碼 Ne10 C 庫則提供了經 Arm 優化適用于計算密集型操 作的函數。

專用引擎分擔主 CPU 的負荷 除了用戶 CM4 復合體和 Arm Cortex-A35 多核 CPU 平臺之外,該架構還提供了專門用于多媒體應用的額外引擎。除了用于音 頻和語音編解碼器處理的數字信號處理器 (DSP) 之外,該架構還集成了 GPU 和視頻處理單元 (VPU)。該器件的 GPU 支持標 準圖形庫,使用具有 16 個執行單元的四個獨立的四分量浮點矢量 (VPU) 和高性能二維位傳輸引擎來加速操作。VPU 用于處 理常見的視頻格式,加速解碼高達 4Kp30(逐行、30 Hz)的視頻和編碼高達 1080p30 的視頻。反過來,該芯片的專用顯示 控制器模塊可以將圖形輸出驅動至多達三個獨立的顯示器。

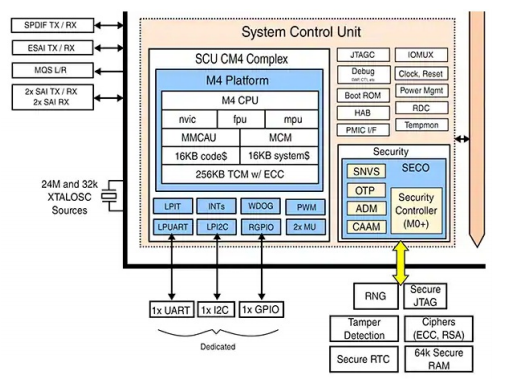

為進一步實現最大化性能,i.MX 8X 架構還集成了更多處理器內核,這些內核旨在將主 CPU 平臺從通常在執行系統管理和安 全性服務時發生的其他處理負載中解放出來。針對系統管理,該架構的系統控制單元 (SCU) 集成了一個與用戶 CM4 復合體匹 配的 CM4 復合體,但將其保留完全專用于 SCU 操作,而且不供開發人員使用(圖 3)。

圖 3:該 SCU 深度集成在 NXP i.MX 8X 處理器內,不供開發人員使用,而是使用專用的 Arm Cortex-M4 (CM4) 子系統從器 件的主要處理器分擔系統管理任務。(圖片來源:NXP Semiconductors)

除了管理電源、時鐘和其他內部功能外,該 SCU 還控制正常操作中的引腳多路復用和輸入 / 輸出 (I/O) 通道驅動強度。實際 上,用戶 CM4 復合體和 Arm Cortex-A35 AP 都不能直接訪問這些不同的底層硬件功能。相反,該 SCU 起到了抽象這些功能 的作用,因此在用戶 CM4 或 AP 上運行的軟件只需調用 SCU 固件應用編程接口 (API) 函數,便可執行諸如關閉不需要的功率 域這類功能。例如,如果該功率域正在與另一個處理器共享,則該 SCU 僅確認斷電請求,但仍將該域保持通電,直到前述另 一個處理器也發出了斷電請求。

為了管理 i.MX 8X 器件廣泛的安全性支持,另一個專用處理器將在器件的安全性控制器 (SECO) 子系統中發揮作用。在 SECO 子系統內,一個集成的低功耗 Arm Cortex-M0+ 處理器用于執行固件,以支持基于硬件的安全性功能,包括用于安全密 鑰的專用總線訪問、用于安全密鑰存儲的一次性可編程 (OTP) 存儲器,以及用于其他私有數據或臨時密鑰的安全非易失性存 儲 (SNVS)(圖 4)。

圖 4:在 NXP i.MX 8X 安全性控制器 (SECO) 子系統內,一個專用的低功耗 Arm Cortex-M0+ 處理器用于管理安全性操作, 利用一條私鑰總線和多個硬件模塊實現安全存儲、加密加速和經過身份驗證的調試訪問。(圖片來源:NXP Semiconductors)

-

嵌入式

+關注

關注

5082文章

19115瀏覽量

304938

發布評論請先 登錄

相關推薦

嵌入式系統的未來趨勢有哪些?

【「嵌入式Hypervisor:架構、原理與應用」閱讀體驗】+第三四章閱讀報告

數字式稱重傳感器的功能演變過程

嵌入式視覺系統實現智能化所面臨的挑戰該怎么解決?

入門物聯網,嵌入式是關鍵

入門物聯網,嵌入式是關鍵

入門物聯網,嵌入式是關鍵

SoC平臺安全要求1.0

基于多密碼算法IP核集成方法實現安全芯片功能多樣化

嵌入式系統設計的演變過程中如何實現功能和安全要求說明

buck電路的演變過程

了解關鍵嵌入式系統設計的演變過程如何滿足多樣化的功能和 安全要求

了解關鍵嵌入式系統設計的演變過程如何滿足多樣化的功能和 安全要求

評論