現代工業設備系統要求越來越復雜,既要強大的多任務的事務處理能力,又需要低延時實時任務處理能力的需求,特別是工業自動化控制領域(如數控機床、機械臂)、電力監測領域(如DTU、繼保設備、一二次融合設備)等應用場景尤為迫切。為了滿足日益復雜的系統要求,創龍科技推出了基于Xilinx Zynq-7020/7010實現的雙系統解決方案。

Xilinx Zynq-7020/7010是一款集成雙核ARM Cortex-A9 + Artix-7 FPGA架構的單芯片SoC,它的OpenAMP框架可實現雙核ARM Cortex-A9非對稱使用方案,從而使雙核ARM實現分別跑兩個系統:一個ARM Cortex-A9跑Linux,一個ARM Cortex-A9作為實時核跑RTOS(FreeRTOS)或者裸機。實時核與FPGA端進行低延時的高速數據交換與實時通訊控制,從而滿足低延時的實時任務要求。而跑Linux的 ARM核作為更上層應用,處理更復雜的業務事務。

Xilinx Zynq-7020/7010單芯片SoC方案配合雙系統的應用為工業控制、電力一二次融合設備、醫療電子、測試測量、汽車電子、通信等應用提供了更靈活、更具成本優勢的解決方案。

1、echo_test案例

1.1 案例功能

案例功能:CPU0使用RPMsg向CPU1發送數據,CPU1接收到數據后再使用RPMsg向CPU0回傳數據。CPU0對回傳的數據進行驗證,并輸出驗證結果。

1.2 操作說明

將CPU1裸機或FreeRTOS可執行文件復制到評估板文件系統“/lib/firmware/”目錄下,并執行如下命令加載CPU1程序。

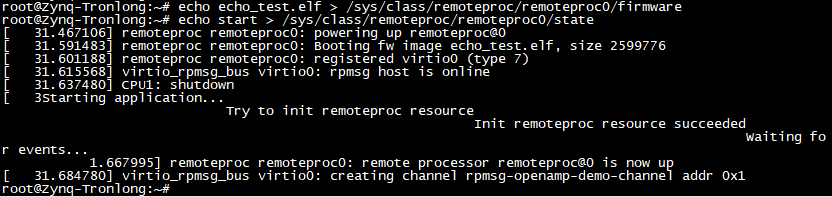

Target# echo echo_test.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

圖 3

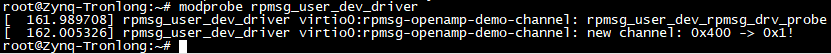

執行如下命令加載RPMsg驅動,并在“/dev/”目錄下生成RPMsg設備節點。

Target# modprobe rpmsg_user_dev_driver

圖 4

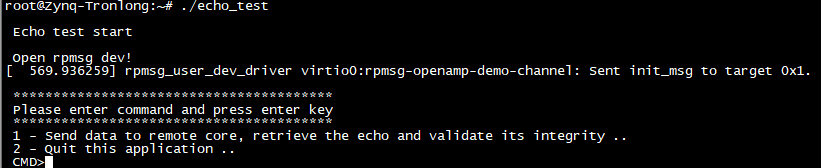

將CPU0應用程序可執行文件復制到評估板文件系統,并執行如下命令通過RPMsg與CPU1進行通信。

Target# ./echo_test

圖 5

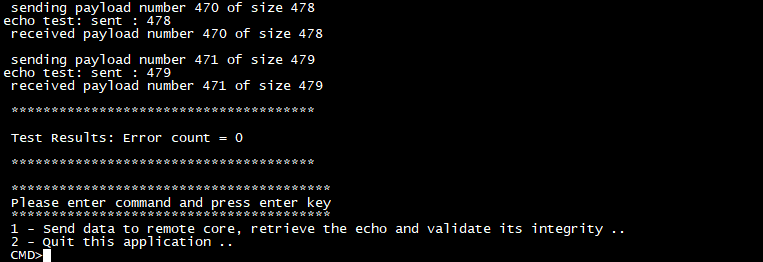

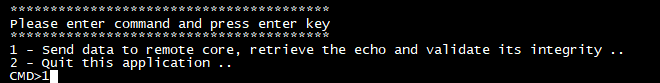

輸入1,并按回車鍵進行測試。

圖6

圖7

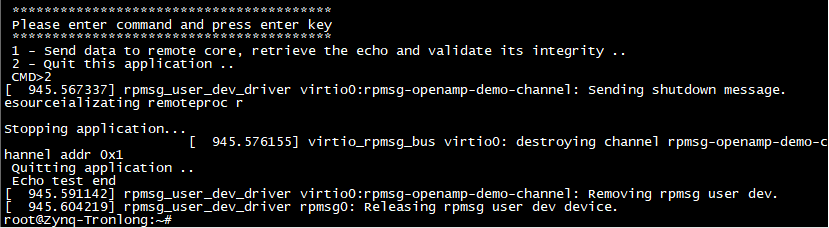

輸入2,并按回車鍵退出測試。

圖 8

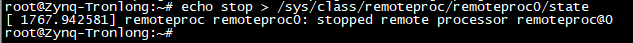

執行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

圖 9

2、matrix_multiply案例

2.1 案例功能

案例功能:CPU0隨機生成兩個矩陣并使用RPMsg向CPU1發送數據,CPU1接收到數據后進行矩陣乘法運算,再使用RPMsg向CPU0回傳運算結果,然后CPU0通過串口終端輸出運算結果。

2.2 操作說明

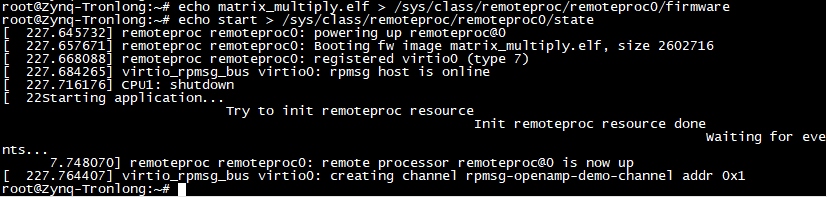

將CPU1裸機或FreeRTOS可執行文件復制到評估板文件系統“/lib/firmware/”目錄下,并執行如下命令加載CPU1程序。

Target# echo matrix_multiply.elf > /sys/class/remoteproc/remoteproc0/firmware

Target# echo start > /sys/class/remoteproc/remoteproc0/state

圖 10

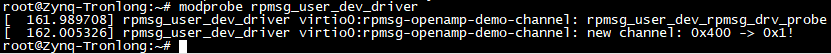

執行如下命令加載RPMsg驅動,并在“/dev/”目錄下生成RPMsg設備節點。

Target# modprobe rpmsg_user_dev_driver

圖 11

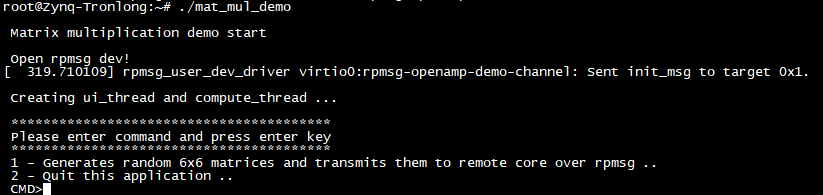

將CPU0應用程序可執行文件復制到評估板文件系統,并執行如下命令通過RPMsg與CPU1進行通信。

Target# ./mat_mul_demo

圖 12

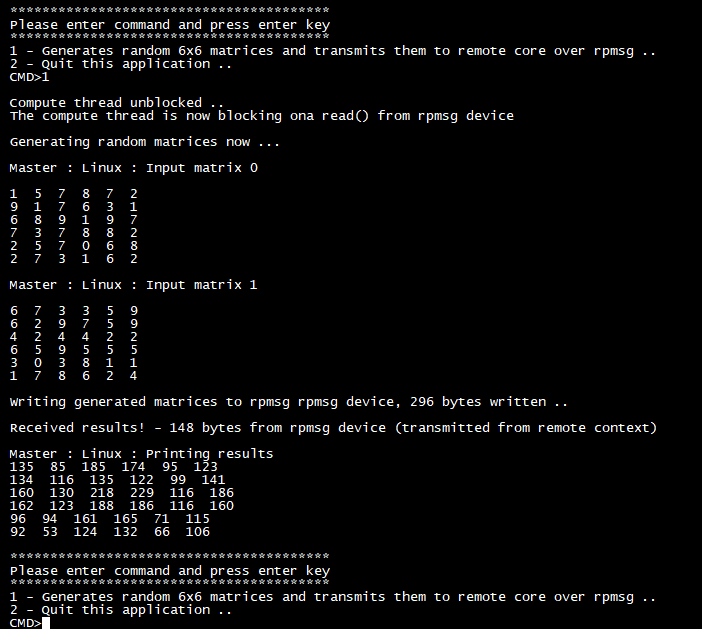

輸入1,并按回車鍵進行測試。

圖 13

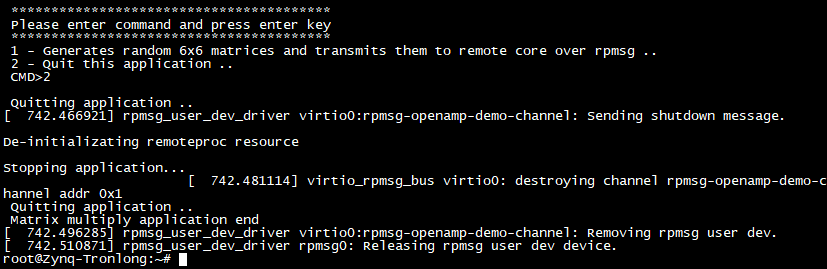

輸入2,并按回車鍵退出測試。

圖 14

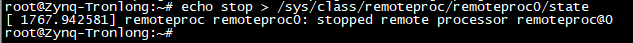

執行如下命令,停止CPU1程序。

Target# echo stop > /sys/class/remoteproc/remoteproc0/state

圖 15

3、內存分配說明

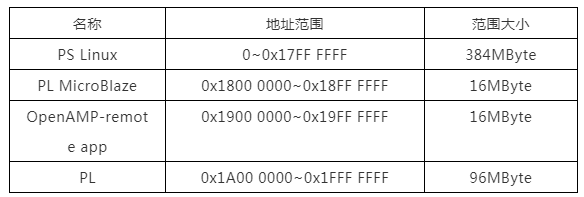

512MByte DDR容量版本核心板的內存地址分配如下:

表 1

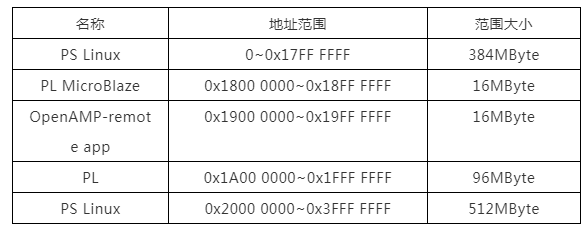

1GByte DDR容量版本核心板的內存地址分配如下:

表 2

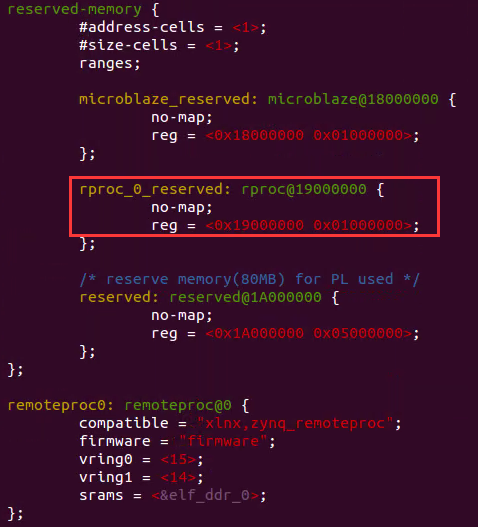

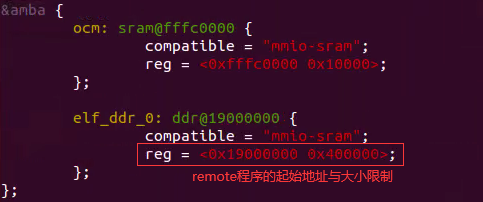

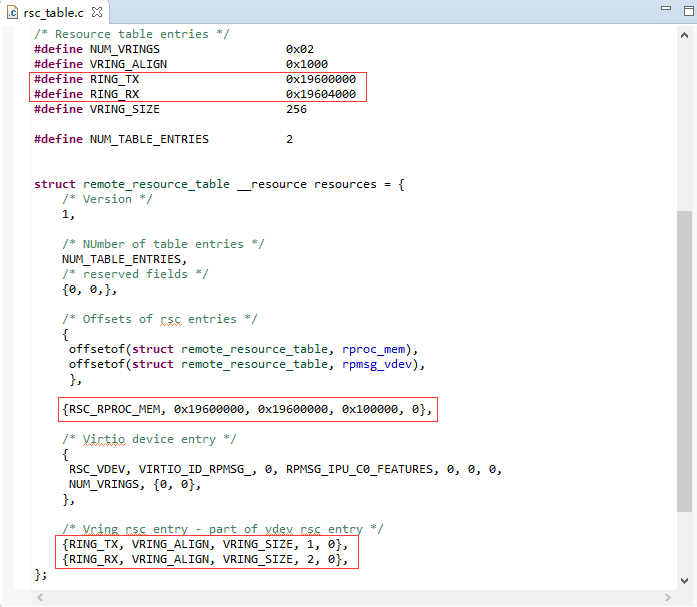

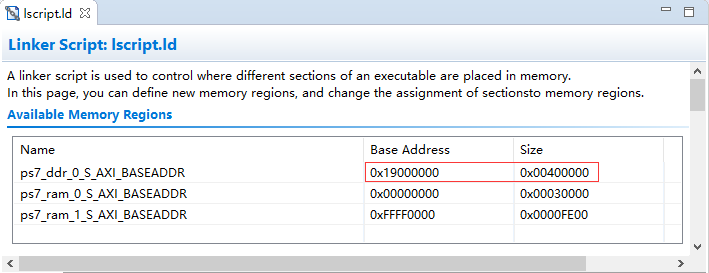

如需修改CPU1程序(OpenAMP-remote app)內存地址空間范圍,可通過更改設備樹文件tlz7x-easyevm-s.dts、資源表rsc_table.c及鏈接文件lscript.ld對內存地址空間進行重新分配。三者需同步修改并保持一致,以確保固件程序鏈接地址與設備樹配置的elf_ddr_0對應。所使用的資源(內存和virtio設備資源)不能超出設備樹文件配置的內存范圍。

圖 16設備樹文件tlz7x-easyevm-s.dts配置

圖 17設備樹文件tlz7x-easyevm-s.dts配置

圖 18 CPU1程序資源表rsc_table.c配置

圖 19 CPU1程序鏈接文件lscript.ld配置

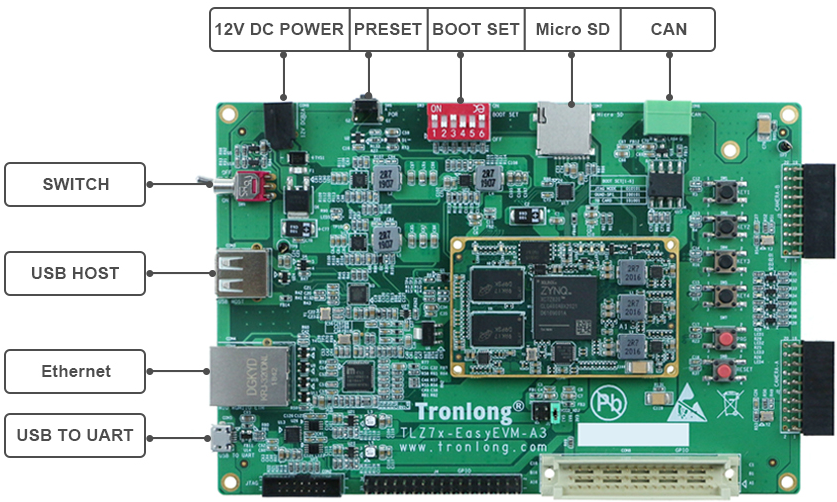

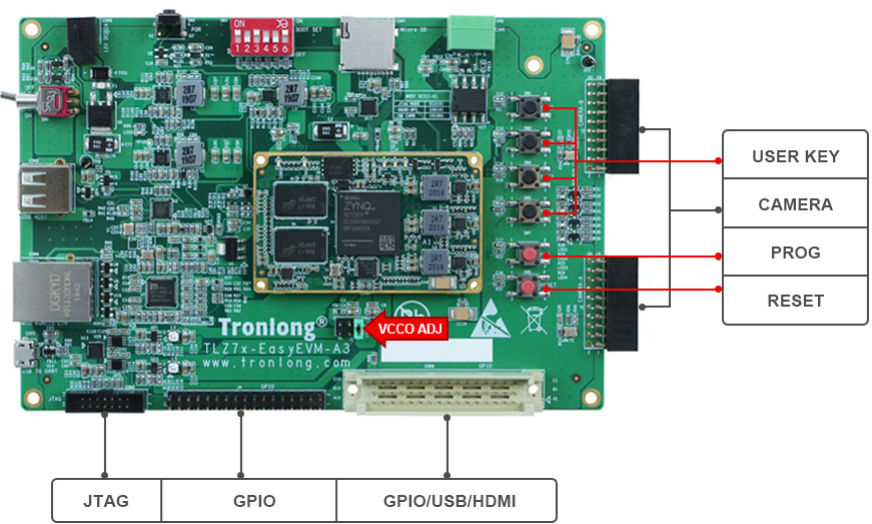

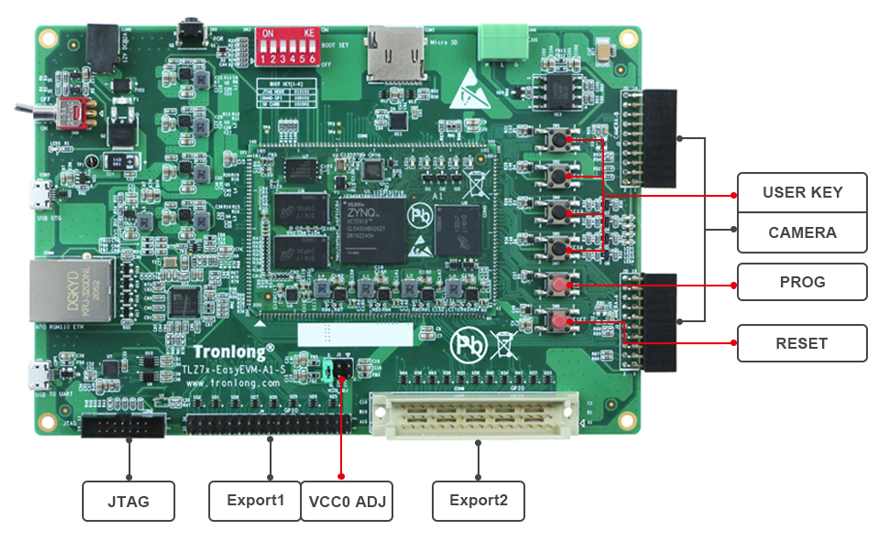

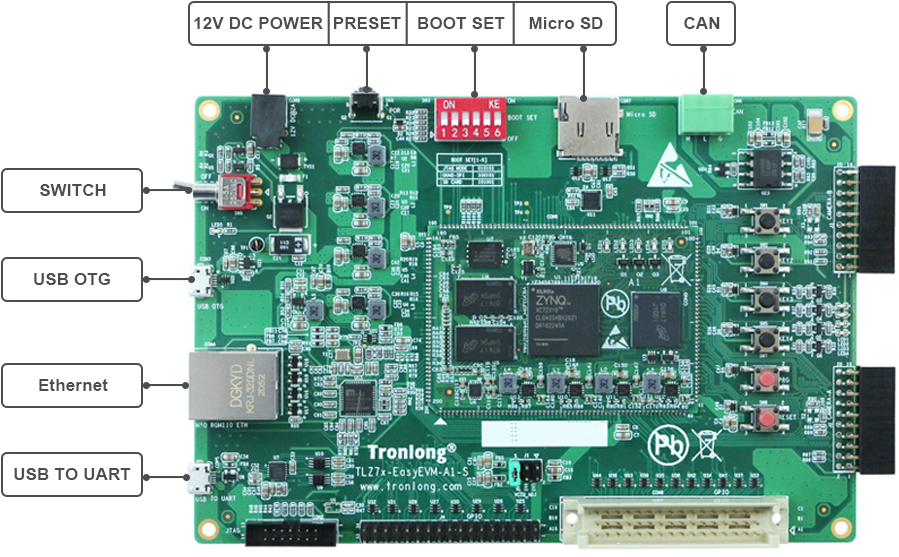

上述推文中的案例是在創龍科技(Tronlong)基于Zynq-7010/7020處理器設計的兩款工業評估板——TLZ7x-EasyEVM、TLZ7x-EasyEVM-S上實現的,它由核心板+底板構成,用戶使用核心板進行二次開發時,僅需專注上層運用,降低了開發難度和時間成本,可快速進行產品方案評估與技術預研。

圖 1 TLZ7x-EasyEVM硬件資源框圖

圖 2 TLZ7x-EasyEVM硬件資源框圖

圖 3 TLZ7x-EasyEVM-S硬件資源框圖

圖 4 TLZ7x-EasyEVM-S硬件資源框圖

-

FPGA

+關注

關注

1629文章

21748瀏覽量

603805 -

ARM

+關注

關注

134文章

9100瀏覽量

367769 -

嵌入式

+關注

關注

5083文章

19133瀏覽量

305657 -

Linux

+關注

關注

87文章

11311瀏覽量

209689

發布評論請先 登錄

相關推薦

Littelfuse推出新型TPSMB非對稱TVS二極管

Littelfuse推出TPSMB非對稱TVS二極管系列

喜報丨羅萊迪思“分布式投影設備”被評為2024年浙江省優秀工業產品!

“雙系統”出爐!瑞芯微RK3562J非對稱AMP:Linux+RTOS/裸機

業界首款用于SiC MOSFET柵極保護的非對稱瞬態抑制二極管系列

非對稱的ARM雙系統,如何實現工業產品的低延時——基于ZYNQ

非對稱的ARM雙系統,如何實現工業產品的低延時——基于ZYNQ

評論