- PCB板布線錯誤;

- 單片機質量有問題;

- 晶振質量有問題;

- 負載電容或匹配電容與晶振不匹配或者電容質量有問題;

- PCB板受潮,導致阻抗失配而不能起振;

- 晶振電路的走線過長;

- 晶振兩腳之間有走線;

- 外圍電路的影響。

- 排除電路錯誤的可能性,因此你可以用相應型號單片機的推薦電路進行比較。

- 排除外圍元件不良的可能性,因為外圍零件無非為電阻,電容,你很容易鑒別是否為良品。

- 排除晶振為停振品的可能性,因為你不會只試了一二個晶振。

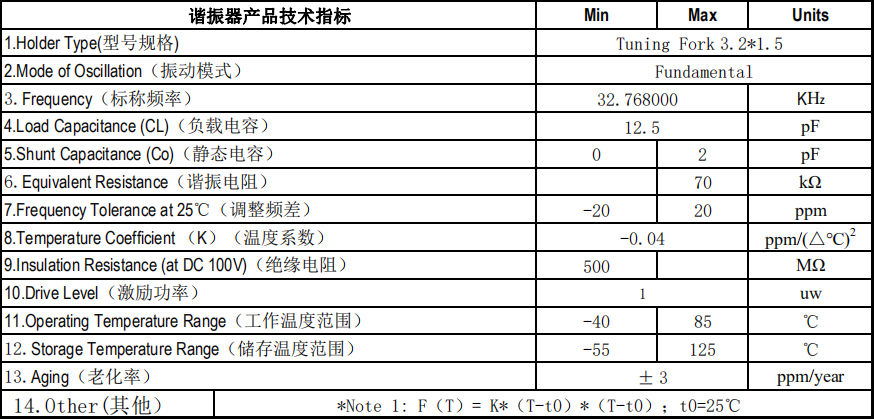

- 試著改換晶體兩端的電容,也許晶振就能起振了,電容的大小請參考晶振的使用說明。

- 在PCB布線時晶振電路的走線應盡量短且盡可能靠近IC,杜絕在晶振兩腳間走線。

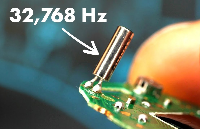

32.768kHz晶振是市面上使用最為廣泛的一類晶振。愛普生/EPSON目前提供三類32.768kHz晶振產品以滿足客戶不同需要,分別是:32.768kHz有源晶振(OSC),32.768kHz無源晶振(X’tal)和內置32.768kHz晶體諧振器的實時時鐘模塊(RTC)。

有源晶振(OSC)和實時時鐘模塊(RTC)由于內置了相應的電路,因而不太容易出現不起振的問題。在實際使用時不需要考慮相對復雜的頻率匹配問題。

不起振的情況主要出現在無源晶振上,尤其是kHz級別的無源晶振(X’tal),而MHz級別的AT晶振則相對少見。

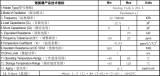

電路結構與晶體單元不匹配。由此導致產生頻率不夠穩定、停止起振或振蕩不穩定等問題。因此在電路設計時,為了獲得穩定的振蕩,通常情況下石英晶體單元與振蕩電路的匹配十分重要。

解決晶振不起振至少要對以下三個要素:對振蕩頻率(頻率匹配)、振蕩裕度(負阻抗)和激勵功率的三項進行評估

電路結構與晶體單元不匹配。由于概率問題,在小批量試產時由于數量少,沒有及時發現。

如何避免晶振不起振導致的時間延誤、不良率高

晶振本身的一致性、穩定性好是解決不起振問題的關鍵之一。如果晶振本身的穩定性、一致性不好,電路結構與其的匹配就無從談起。

盡可能選擇有源晶振,有源晶振的價格要比無源晶體貴,但是由于原廠已經配置好了內部電路,基本不存在電路匹配問題,也就極大避免了晶振不起振問題的發生。

-

晶振

+關注

關注

34文章

2859瀏覽量

68007 -

時鐘

+關注

關注

10文章

1733瀏覽量

131454

發布評論請先 登錄

相關推薦

低功耗輸出頻率32.768kHz的汽車用晶振SG-3031CMA

為什么32.768KHz晶振這么火? 到底應用在哪些領域?

愛普生32.768kHz晶振FC-135:小型化為高端產品帶來的卓越優勢

32.768Khz晶振使用經驗分享

SMD3215 32.768KHZ貼片晶振 ±20ppm,批量價6毛5左右

32.768kHz晶振不起振的原因與解決

32.768kHz晶振不起振的原因與解決

評論