引言

Preface

隨著芯片設計規模的增加,傳統基于單顆 FPGA 的設計調試方法已經不能滿足對大型設計的調試需求,因此多 FPGA 聯合調試技術應運而生。

本次國微思爾芯白皮書《先進多FPGA聯合深度調試方法剖析》分析了用戶在進行大規模原型驗證過程中的多 FPGA 聯合調試難題,并介紹了一種新型 FPGA 原型驗證深度跟蹤調試解決方案,用于幫助客戶在 SoC 開發過程中解決調試問題,從而加速設計驗證、縮短驗證周期。本調試解決方案還提供了不同使用模式,可以用于靈活適配不同用戶的使用場景。

核心內容

Main Point

大規模原型驗證調試中的挑戰

傳統的基于單顆 FPGA 的設計調試方法是在單顆 FPGA 中插入嵌入式邏輯分析儀的方式進行調試的,這種調試方式適用于 單顆 FPGA 的獨立調試應用場景。但是隨著設計規模的增長,當單顆 FPGA 無法滿足原始設計規模時,原始設計就會被分割到多顆 FPGA 中,在此應用場景下傳統基于單顆 FPGA 的設計調試方法存在各種問題。

多FPGA的深度跟蹤調試解決方案

針對 SoC 原型驗證系統中調試需求,本文提出了一種多 FPGA 的深度跟蹤調試解決方案。主要包含以下內容:

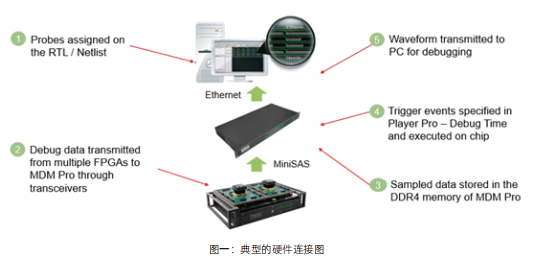

硬件連接及工作流程

基于調試 IP 的探針信號標記過程

基于 GT 的調試信號傳輸

基于 DDR4 的波形數據存儲

基于以太網的波形數據上傳和遠程調試

基于外部高速采樣時鐘和內部邏輯時鐘采樣

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603012 -

調試

+關注

關注

7文章

578瀏覽量

33923

發布評論請先 登錄

相關推薦

“2025 IC風云榜”揭曉,思爾芯獲“年度最佳解決方案獎”

FPGA做深度學習能走多遠?

思爾芯創新實踐成果通過上海市高新技術成果轉化項目認定

思爾芯再度榮膺2024中國IC設計行業TOP 10 EDA公司

年度技術突破EDA公司!思爾芯憑先進解決方案榮獲2024中國IC設計成就獎

演講預告|思爾芯邀您共聚中國IC領袖峰會,一起探索“芯”未來

思爾芯林俊雄:需求驅動產品創新,提升芯片設計競爭力

第五屆EDA挑戰賽賽果公布!思爾芯“戰隊”成績斐然

國微思爾芯多FPGA聯合深度調試新思路

國微思爾芯多FPGA聯合深度調試新思路

評論