航芯“通用MCU技術常見問題”上線啦!

日常工作中,我們的銷售或技術工程師經常會收到來自用戶的問題,其中一些問題是比較常見的,所以為滿足日常用戶對航芯產品使用及服務的了解,航芯特此推出“通用MCU技術常見問題”專題,分為F0專題及F4專題,歡迎大家持續關注!

F0專題 - 工具篇

1

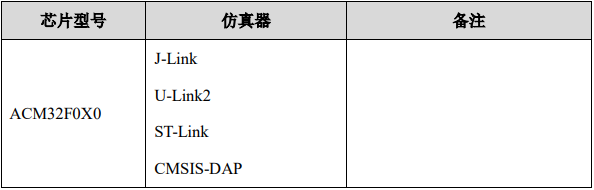

1.1 Keil-Debug 工具

ACM32F0X0 系列支持的在線仿真器包括:J-Link、U-Link2、ST-Link、CMSIS-DAP,使用 J-Link 在線調試時,Keil 推薦在 MDK5.0 以上。

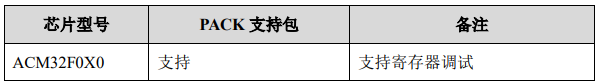

1.2 Keil-Pack 支持包

ACM32F0X0 系列提供 PACK 支持包,詳細信息如下表:

1.3 Keil 工程編譯失敗或 F12 無法跳轉

請確認工程文件目錄沒有中文名稱。

2

IAR

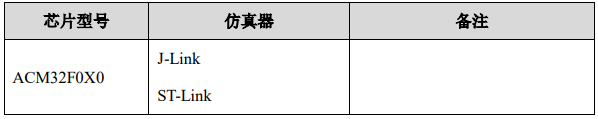

2.1 IAR-Debug 工具

ACM32F0X0 系列支持的在線仿真器包括:J-Link、ST-Link,使用 J-Link 在線調試時,IAR 推薦在 IAR8.50(含)以上。

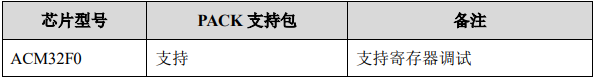

2.2 IAR-Pack 支持包

ACM32F0X0 系列提供 PACK 支持包,詳細信息如下表:

3

開發板仿真調試

ACM32F0X0 系列開發板自帶 CMSIS-DAP 在線仿真器,用戶使用時可直接使用 USB 連接線將開發板 LinkUSB 端口與 PC 端的 USB 接口直接連接,WIN7 需要安裝 SDK 中的USB 驅動(AisinoChipCDC.inf),WIN7 以上系統免驅。

4

開發板串口調試

ACM32F0X0 系列開發板自帶串口調試芯片,與 CMSIS-DAP 為同一個 USB 接口,連接 PC 端后需要安裝 USB 轉串口驅動(AisinoChipCDC.inf),此時設備管理器顯示設備名稱:AisinoChip Virtual Com Port,該虛擬串口主要有兩個功能:

1. 作為串口下載 MCU 固件使用。

2. 作為用戶 APP 應用程序串口調試輸出。

注意:ACM32F0X0 芯片使用 PA9/PA10 作為串口的輸入/輸出管腳,因此在使用MCU的 PA9/PA10 與第三方串口助手連接調試時,需要將其與串口調試芯片斷開。

F0專題 - 應用篇

1

硬件設計

1.1 是否與 SXX32FXXX 硬件兼容?

ACM32F0X0 系列芯片硬件管腳可以與 SXX32FXXX 管腳做到兼容,原 SXX32FXXX的部分電源管腳被 ACM32F0X0 復用作為外設管腳,詳細的硬件管腳配置及復用功能可參考《ACM32FXXX 對比 SXX32FXXX 差異說明.pdf》,具體以文檔為準。

1.2 硬件設計注意事項

1.2.1 電源電路

ACM32F0X0 系列芯片 VDD/VDDA 電壓輸入范圍:1.7V~3.6V,VDD 與 VDDA 之間建議用磁珠隔離,GND 與 AGND 之間建議用 0Ω 電阻隔離。

1.2.2 外部晶振電路

ACM32F0X0 系列芯片外部高速晶振輸入范圍:4~48MHz,典型值推薦使用 8MHz 或者12MHz,無需外接 RF反饋電阻。

1.3 是否支持 FSMC/SDIO/以太網/ISO7816 接口?

暫不支持。

2

SDK 接口驅動庫

2.1 驅動庫版本

2.1.1 Keil-MDK 接口驅動庫版本

ACM32F0X0 系列芯片外設接口驅動庫提供 HAL 庫(Hardware Abstraction Layer),除部分型號芯片外,暫不提供 SPL 庫(Standard Peripherals Library),LL 庫(Low-Layer)暫不支持,詳細信息可咨詢銷售或 FAE。

2.1.2 能否提供驅動庫移植說明?

可以,請參考《ACM32 固件庫_使用說明.pdf》文檔。

2.1.3 寫入啟動序列后如何回到 Boot 模式?

軟件程序中需要預留 HAL_EFlash_Return_To_Boot()接口函數。

2.1.4 Flash 程序如何實現回到 Boot 模式?

軟件程序在執行完 HAL_EFlash_Return_To_Boot()后,如需回到 Boot 模式,可以采用重新上下電、外部 RSTN 管腳復位或 Flash 程序設置 EFC_RST 寄存器進行復位,其中 EFC_RST復位前需要將系統時鐘降低至 64MHz 以下。

2.2 系統時鐘

2.2.1 系統時鐘如何切換至外部時鐘源?

ACM32F0X0 系列芯片上電默認使用內部時鐘,如需使用外部晶振作為時鐘源,需要將軟件程序中的宏定義 PLL_SOURCE_FROM 修改成外部時鐘即可。

2.2.2 內部 RC 時鐘精度是多少?

ACM32F0X0 系列芯片內部 RC64M/RC32K 精度大概率在±1%(含溫漂)左右。

2.3 中斷優先級配置

2.3.1 M0 內核中斷優先級配置

根據 M0 內核手冊可知 Interrupt Priority Registers 寄存器的bit[7:6]用于設置中斷優先級,優先級大小為 0>1>2>3,高優先級中斷可以打斷低優先級中斷,實現中斷嵌套。

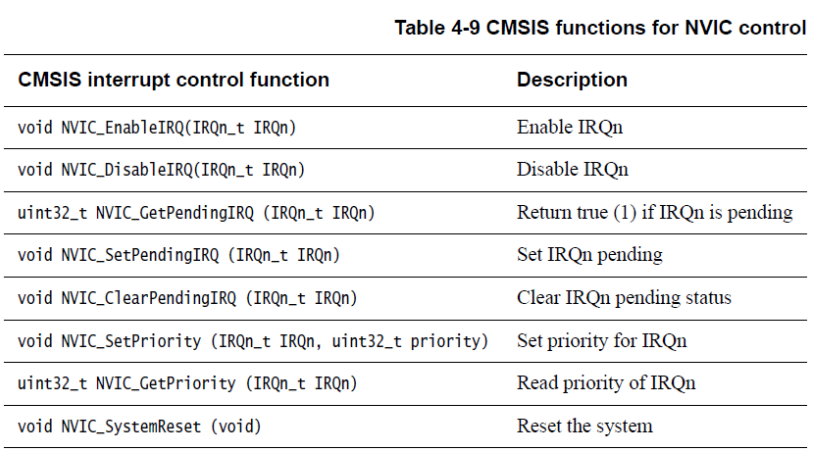

M0-NVIC 相關函數如下表:

2.4 中斷向量表地址偏移

2.4.1 M0-IAP 升級中斷向量表地址偏移

根據 M0 內核手冊可知該架構不提供中斷向量偏移寄存器 REG_NVIC_VECTOR,因此在做 IAP 升級功能時,如需要實現中斷向量表地址偏移,可借助系統寄存器中的中斷向量表重映射寄存器(VECTOROFFSET)實現,相關參考代碼如下:

/* Vector Table Relocation in Internal FLASH */ SCU->VECTOROFFSET = EFLASH_BASE | VECT_TAB_OFFSET | SCU_VECTOROFFSET_VOFFSETEN;2.5 低功耗

2.5.1 STOP 模式下功耗偏高

根據應用電路情況,可將未使用的管腳配置成模擬模式,已使用的管腳根據外部電路,配置成數字模式,選擇合適的上下拉或輸出合適的高低電平。

3

固件下載

3.1 是否支持 J-Flash 下載固件?

支持,請參考《航芯通用 MCU 使用 JFlash 燒錄程序的方法說明.pdf》文檔。

3.2 是否支持離線批量燒錄?

支持,離線燒錄器詳細信息可咨詢銷售或FAE。

3.3 原廠固件下載工具 UART 波特率自適應失敗

請使用最新版本的下載工具(Aisinochip_MCU_Download_Tool_v1.4.0.3.exe(含)以上)。

4

補充功能

4.1 是否支持 Flash 讀保護?

支持,請參考《航芯 ACM32F 系列芯片 Flash 讀保護功能說明.pdf》文檔。

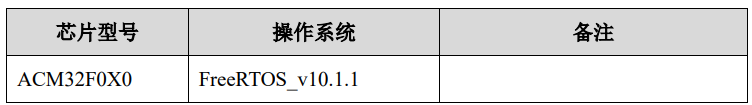

支持 uCOS-II、FreeRTOS 和 RT-Thread 操作系統,詳細信息如下表:

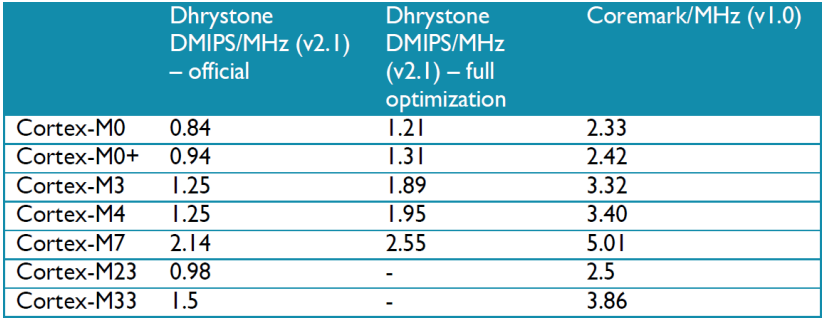

4.3 Dhrystone 測試性能

M0 內核:Keil 優化等級-O3, Dhrystone 2.1 測試 0.70 MIPS/MHz。

5

GPIO

5.1 輸入是否支持 5V tolerant?

ACM32F0X0 系列不支持,詳細信息可參考對應型號的 DataSheet 文檔。

5.2 GPIO 管腳上電默認狀態?

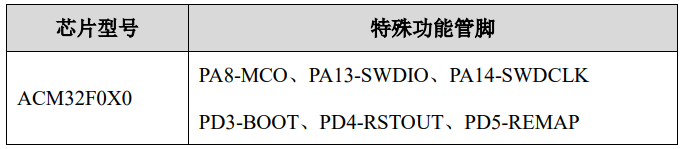

ACM32F0X0 系列芯片上電,除部分特殊的功能管腳外(見下表),其余管腳默認狀態為模擬模式(數字功能失效,上下拉電阻失效)。詳細信息請參考《航芯 ACM32FXXX 系列芯片 GPIO 應用手冊.pdf》文檔。

5.3 PC13/14/15 作為通用管腳注意事項

除正常配置 GPIO 管腳功能外,還需要調用 RTC 相關寄存器,相關參考代碼如下:

/* RTC access enable */ System_Enable_Disable_RTC_Domain_Access(FUNC_ENABLE); __HAL_RTC_PC13_SEL(0); // GPIO function __HAL_RTC_PC13_PULL_UP_ENABLE(); __HAL_RTC_PC13_DIGIT();5.4 GPIO 最高翻轉速率?

GPIO 翻轉速率最高 50Mbps。

5.5 FT 和 TC 管腳的區別

FT:5V 耐壓的管腳 IO,TC:標準 1.7V~3.3V 的管腳 IO。FT 管腳相對于 TC 管腳可以防止外部 IO 電流倒灌。

6

TIMER

6.1 PWM-duty=0 輸出異常

建議通過配置成 GPIO 功能軟件繞過,或通過 MOE/OSSI/OSSR/CCxE/CCxNE 組合位配置 PWM 模式繞過。

6.2 CCRx 輸出比較波形周期不準

建議嘗試打開 CCRx 寄存器預裝載功能。如使用 CCRx 功能實現計數延時功能,則需要關閉 CCRx 預裝載功能。

6.3 TIMx 剎車源信號極性如何配置?

對于 TIMx_BKIN 外部管腳和 COM1&2_OUT 源信號,可通過 TIMx_BDTR 寄存器的BKP 位設置;對于 CPU_LOCKUP、SRAM_PARITY 和 LVD_LOCK 內部信號,剎車源極性不需要設置。

7

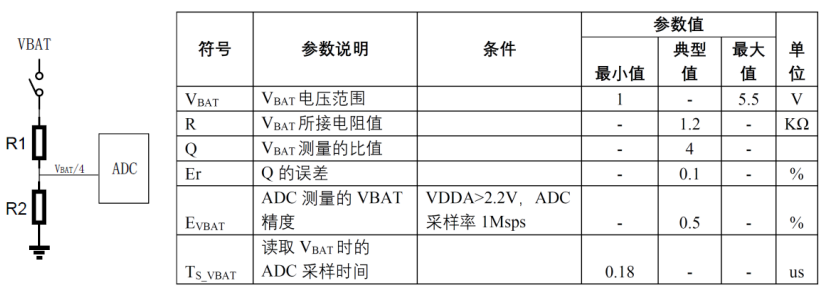

7.1 ADC_VBAT(1/4 分壓)需要外部分壓嗎?

不需要,內部已配置 1/4 電阻分壓,外部不需要單獨的分壓電路,如下圖所示,內部分壓電阻 R1+R2 總阻值為 1.2KΩ 左右,VBAT 為芯片 ADC 的輸入管腳。詳細信息請參考《航芯 ACM32FXXX 系列芯片 ADC 應用手冊.pdf》文檔。

7.2 ADC_Buffer 通道與普通通道是否有區別?

有區別,ADC 的 Buffer 是指緩沖放大器,相對于普通的 ADC 通道,帶 Buffer 的 ADC通道輸入范圍小一點,輸入阻抗大一點,詳細信息可參考對應型號的 DataSheet 文檔。

7.3 ADC 如何使用內部參考電壓?

部分封裝芯片 VREFP 管腳內部與 VDDA 連接在一起,因此無法使用內部參考電壓。對于單獨封裝出 VREFP 管腳的封裝芯片可以通過懸空 VREFP 管腳配置使用內部參考電壓。

7.4 ADC 正常采樣結果計算不準

可通過調用 ADC_GetVrefP 函數校準參考電壓(出廠前使用 3.0V 對 BGR 校驗)。

7.5 ADC 外部分壓后采樣值偏低,如何處理?

ADC 采樣時間不足的情況下會引入 RAIN 電阻,導致外部管腳分壓偏低,可以通過增大 ADC 采樣時間恢復正常。

8

RTC

8.1 是否支持 RTC 外部獨立供電?

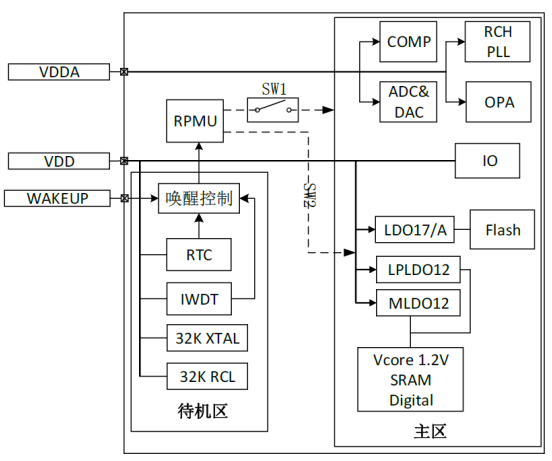

ACM32F0X0 沒有單獨 vBat 接口給內部 RTC 模塊供電(不支持外部電池給 RTC 供電,主區供電可關閉-StandBy 模式),下圖為芯片內部電源示意圖,此時 IWDT 和 RTC 仍能繼續工作。如需外部獨立給 RTC 供電方案,可參考《VBAT&VCC-WAKE_V0.2.pdf》文檔。

9

UART

9.1 是否支持 9bit 數據位傳輸?

硬件本身不支持 9bit 數據位,根據應用需要,可借助校驗位/STOP 位替代增加數據位數。

9.2 FIFO 使能 1 字節發送中斷無法產生中斷

串口發送使能+串口使能+FIFO 使能的情況下,FIFO 深度配置 1/16 字節時,發送 1 字節會直接將數據填進移位寄存器,而不經由 FIFO,進而不產生中斷;如初始化不開啟串口發送使能,在數據填充完畢后再開啟,則發送數據會經過 FIFO 再到移位寄存器,此時能正常產生中斷。

10

OPAMP

10.1 OPAMP 失調電壓如何修調?

上電后可使用芯片 NVR 內部保存的修調值,或上電循環自修正。

11

11.1 接收/發送時是否支持時間戳?

不支持。

11.2 是否支持 BUS_OFF 硬件自恢復?

不支持 BUS_OFF 硬件自恢復(ABOM 功能),可通過在 BUS_OFF 中斷中讓 CAN 總線進入恢復模式,間接實現 BUS_OFF 硬件自恢復。

11.3 是否支持禁止自喚醒?

不支持,ACM32F0X0 在檢測到 CAN_RX 上低電平后會強制喚醒。

11.4 硬件重發能否關閉?

無法關閉,ACM32F0X0 固定使能硬件重發功能。

11.5 接收 FIFO 溢出時數據如何處理?

接收 FIFO 滿時,ACM32F0X0 固定會丟棄新數據,保留老數據。

11.6 發送 FIFO 數據幀發送順序?

ACM32F0X0 的 CAN 模塊只有 13 字節的發送 FIFO,因此發送的數據幀只能依次發送,沒有額外的數據幀緩存空間。

11.7 接收數據正常,發送數據失敗

此類問題通過查看錯誤代碼獲取寄存器(CAN_ECC)可以大致了解出錯原因,若問題主要集中在 CRC 分隔符/ACK/ACK 分隔符錯誤碼,推薦 CAN 通訊時切換至外部晶振模式。

12

USB

12.1 是否支持免晶振模式?

支持,系統時鐘配置使用內部 RC 時鐘。

如系統時鐘配置外部晶振模式,建議將 USBPHY 時鐘通過 OSC_MODE 配置為強制選擇內部 RC 模式。

13

SPI

13.1 SPI 最高速率?

SPI主機模式:ACM32F0X0受GPIO速率影響,最高50Mbps;SPI從機模式:ACM32F0X0最高速率 25Mbps。

14

EXTI

14.1 PB6 無法實現 EXTI 中斷

ACM32F0X0 系列:將 PB6 管腳拉低無法觸發 EXTI 外部中斷,而將 PB7 管腳拉低時會同時觸發 EXTI_Line_6 和 EXTI_Line_7 兩種類型的外部中斷。芯片硬件問題,EXTI_Line_6和 EXTI_Line_7 內部兩個 EXTI 通路默認都選擇為 PB7 通道。

-

mcu

+關注

關注

146文章

17171瀏覽量

351517

發布評論請先 登錄

相關推薦

AFE7070中頻頻率f0最好設置在一個什么范圍?

采用MSP430FR604x MCU的水流和燃氣流量計量超聲波傳感技術的常見問題解答(FAQ)

航芯通用MCU技術常見問題 | F0專題

航芯通用MCU技術常見問題 | F0專題

評論