本期開發筆記詳細為大家介紹基于HPM6750微控制器的硬件電路設計,可以有效提高硬件設計成功率和成熟度,想了解的 “攻城獅“們趕緊上車~

01

簡介

本文檔的目的是幫助硬件工程師設計和測試基于HPM6750微控制器的硬件電路設計。它提供了關于電路板布局建議和設計清單。

本硬件指南適用于HPM6700/6400系列芯片。同時,可參考對應芯片的數據表、參考手冊、以及應用手冊。

02

電源配置

2.1電源系統

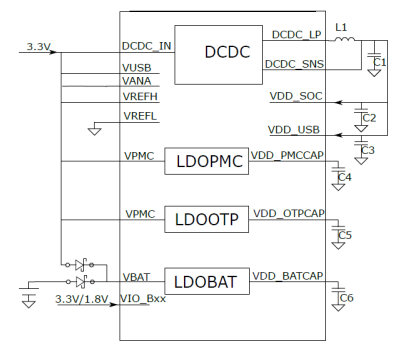

該系列芯片供電是通過對DCDC_IN 和VPMC 腳輸入3.0-3.6V單一電源, 并通過內置的電壓調節器提供系統所需的VDD_SOC, VDD_PMCCAP, VDD_OTPCAP, V_BATCAP 電源。

當電源DCDC_IN 和VPMC 掉電后,通過VBAT 腳為實時時鐘(RTC) 和備份寄存器提供電源。每個I/O 電源VIO_Bxx 根據相應負載接3.3V 或1.8V電源。電源控制圖如圖1,適用于HPM6700/6400芯片。若無另行說明,所有電壓都以VSS 為基準,VSS接地。 圖1電源控制圖電源域信號電平和去耦電容的建議,請分別參見表 1和表 2 。

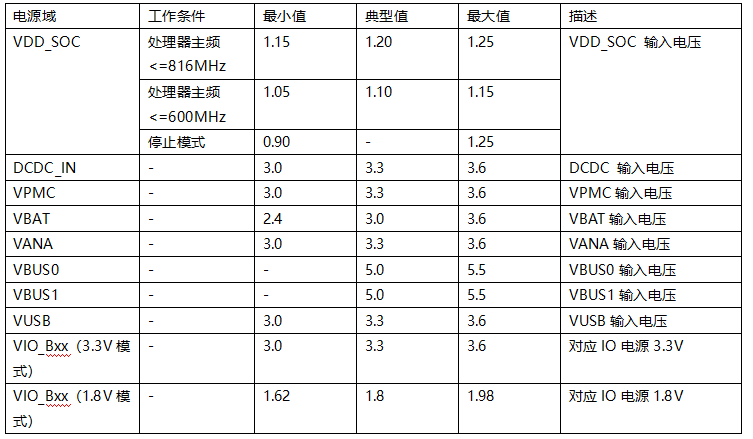

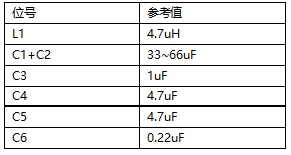

圖1電源控制圖電源域信號電平和去耦電容的建議,請分別參見表 1和表 2 。 表1 ?電源域

表1 ?電源域 表2?去耦電容推薦值

表2?去耦電容推薦值

2.2 提升A/D 轉換器性能以及參考電壓的特別要求

為了提高轉換精度, ADC 電路配有獨立電源入口,可以由外圍電路做電源濾波以減小 PCB 上的噪聲,對于需要高精度采樣的場合,可以配合高精度的參考電壓源實現高精度的AD采樣。?一個獨立的 VANA 引腳給 ADC 供電。建議使用低噪音LDO供電。?VSS引腳提供了獨立的電源接地連接。?VREFH/VREFL為芯片提供高精度低溫飄的外部參考電壓,例如REF431, 可以提升ADC的采樣精度。VREFH上的電壓范圍為2.4 V 到 3.6V。VREFH/VREFL需要在Pin 附近增加去耦電容,通常采用10nF。

(此處劇透:先楫會推出AD采樣精度報告,想了解更多,請關注后期推送)

2.3上電時序

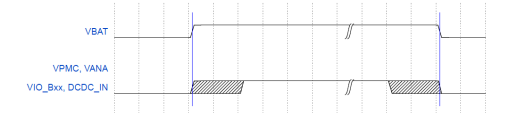

上電時序要求:要求VBAT 不晚于其他電源上電。如果VBAT 和其他3.3V 電源引腳使用相同的供電,則系統對上電時序沒有要求。掉電時序要求:VBAT 電源不能早于其他電源掉電。 圖2電源時序

圖2電源時序

03

3.1晶振/陶振

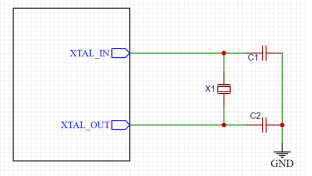

諧振器和負載電容必須盡可能地靠近振蕩器的引腳,以盡量減小輸出失真和起振時間。

負載電容值必須根據所選振蕩器的不同做適當調整。對于 C1 和 C2,建議使用專為高頻應用設計、可滿足晶振或諧振器的要求且大小介于5pF 到 25 pF(典型值)之間的高質量陶瓷電容。 圖3外部晶振/陶瓷諧振

圖3外部晶振/陶瓷諧振

C1和C2 的大小通常相同。晶振制造商指定的負載電容通常是 C1 和 C2 的串聯組合。確定 CL1 和 CL2 的規格時,必須將 PCB和 MCU 引腳的電容考慮在內 (引腳與電路板的電容可粗略地估算為 10 pF)。

04

調試

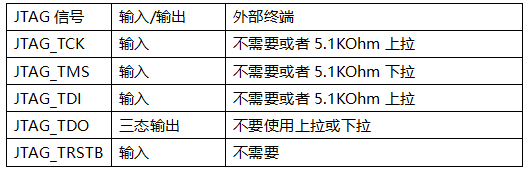

HPM6700/6400系列產品的調試系統符合The RISC-V Debug Specification, Version 0.13 規范。調試系統包括JTAG 接口轉換模塊(DTM)和調試模塊(DM)2 部分。DTM 通過標準JTAG 接口對接外部調試器,可以把JTAG 上收到的調試指令轉換成對DM 模塊的讀寫訪問。調試模塊DM 集成了調試功能,可以暫停或者恢復CPU 的運行,產生復位,以及訪問片上資源。表3 JTAG接口

以上為本期分享內容,請繼續關注,下期會推出下一篇續集,敬請留意!

-

電路設計

+關注

關注

6673文章

2451瀏覽量

204190

發布評論請先 登錄

相關推薦

HPM6750evkmini如何實現可信的執行環境?

OC6700-規格書

HPM SDK 1.6.0 FreeRTOS LTS更改及適配指南

國產高性能MCU又一力作,集成授權EtherCAT,助力工業伺服走向海內外

先楫HPM6E00新品上市在即

開發者分享 | 基于先楫RT-Thread BSP,使用CLion開發應用

HPM USB系列:HPM6700雙USB功能介紹

HPM USB系列:HPM6700雙USB功能介紹

干貨分享 | HPM6700系列硬件設計指南 (上)

干貨分享 | HPM6700系列硬件設計指南 (上)

評論