概述

AT32的微控制器內置最多三個高級12位片上SAR模擬數字轉換器(ADC)并提供自校準功能,用于提高環境條件變化時的ADC精度。在涉及模數轉換的應用中,ADC精度會影響整體的系統質量和效率。為了提高此精度,必須了解ADC相關的運作和影響精度的原因。

SAR ADC使用一個采樣電容充電至輸入信號電壓,SAR邏輯對此電壓做數據轉換。然而,這個ADC內的采樣電容是由外部的信號源直接充電的,也因著采樣電容值、輸入阻抗、還有外部線路影響,需要一段充電穩定時間來保證對輸入信號電壓量測的準確性。為達到好的ADC量測,必需設置足夠的采樣時間。否則,前一次在某一輸入通道轉換所殘余在采樣電容上的電荷,會影響目前正在進行轉換通道的準確性。ADC精度不僅取決于ADC性能和功能,還取決于ADC周圍的整體應用設計。此應用筆記旨在幫助用戶如何設置正確軟、硬件使ADC達到準確的量測,也提供相關應用上的注意事項。

ADC的誤差來源及其誤差最小化辦法

本章列出了影響ADC轉換精度的主要誤差。這些類型的誤差存在于所有ADC中,轉換質量將取決于它們的消除情況。為便于參考,將精度誤差以LSB為單位來表達。就電壓而言,通過將LSB數乘以1 LSB對應的電壓來計算電壓誤差(1 LSB=VREF+/4096或VDDA/4096)。

ADC自身誤差

ADC自身誤差為ADC本身設計和制造時所產生本體的誤差,這類誤差通常由以下靜態參數顯示:微分線性誤差(DNL)、積分線性誤差(INL)、偏移誤差(OE)、增益誤差(GE)、和總未調整誤差(TUE)。AT32微控制器數據手冊的ADC特性部分規定了這些誤差的定義和值。其中TUE為實際和理想傳輸曲線間的最大偏離,此參數指定可能發生的會導致理想數字輸出與實際數字輸出之間最大偏離誤差。(注意TUE不是DNL、INL、OE、與GE之和,它可能源自同時發生的一種或多種誤差。)

AT32 ADC自校準功能可以補償偏移誤差,在ADC使用前先進行一次自校準可保證在數據手冊揭示范圍的任何環境條件之下,TUE小于4 LSB,也就是保證12位ADC靜態準確度(accuracy)可達10位以上。

至于ADC的動態參數(如:ENOB)及其代表的誤差程度,通常在語音和特定音頻應用才會考慮,在一般MCU的應用場合不會太重視,在本文中也不于討論。

ADC環境導致的誤差

參考電壓/電源噪聲由于ADC轉換值為模擬信號電壓(VAIN)與參考電壓之比(VREF+),因此VREF+上的任何噪聲都會導致轉換后數字值的變化。在某些封裝中,VDDA模擬電源被用作參考電壓(VREF+),因此VDDA電源的質量會影響ADC誤差。VREF+幾十mV的波動就會造成十幾LSB的誤差。

就供電側噪聲而言,開關式電源模塊通常內置快速切換功率晶體管,這會在輸出中產生高頻噪聲,此切換噪聲介于15 kHz至1 MHz之間,也需留意。線性穩壓器的輸出質量更佳。如果使用切換電源,建議使用線性穩壓器供應模擬級。建議在電源線和地線之間連接具有優良高頻特性的電容。應在靠近電源的位置安裝一個0.1 μF和一個1至10 μF的電容。這些電容允許直流信號通過它們。小值電容過濾高頻噪聲,高值電容過濾低頻噪聲。要過濾高頻噪聲,還可使用與電源串聯的鐵氧體電感器(ferrite bead)。由于線的串行電阻極低,此解決方案導致的直流損失極低(可忽略不計),除非電流很大。

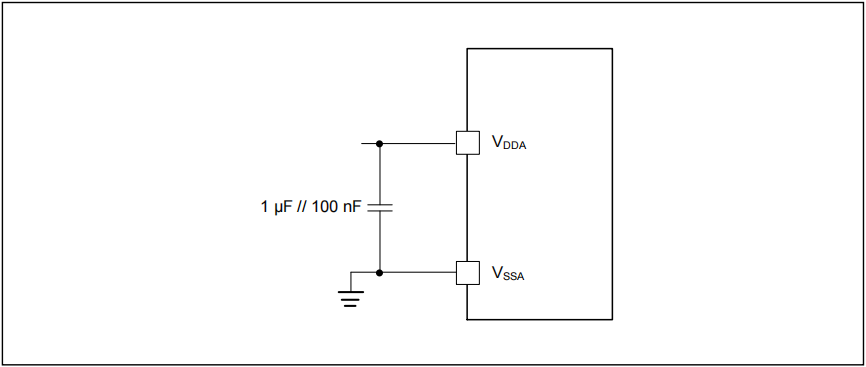

微控制器端VDD和VSS引腳的安裝位置很接近,因此可以在盡量靠近的位置通過極短的引線將電容連接到微控制器。VDDA和VREF+引腳必須連接到兩個外部去耦電容,100 nF陶瓷電容加上1 μF鉭電容或陶瓷電容。注意數字地與模擬地應相互隔離,避免噪聲串擾。

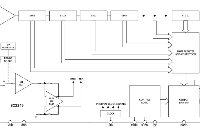

圖1. 具有VREF引腳封裝的電源和參考去耦 圖2. 無VREF引腳封裝的電源和參考去耦

圖2. 無VREF引腳封裝的電源和參考去耦 GPIO輸入電壓電平超出常規AT32F403系列、AT32F413系列、和AT32F415系列作為具有ADC輸入功能的任一GPIO引腳,輸入的電壓不能超過VDD+0.3V(VDDA與VDD須同電位),否則會由芯片內部干擾ADC輸入信號。只要是ADC輸入功能的GPIO,即使只當I/O輸入用途,如果輸入的電壓超過VDD+0.3V,也會干擾其它ADC通道轉換結果。如果存在此種高電壓,建議使用電阻分壓或減壓到小于VDD的電壓范圍。

GPIO輸入電壓電平超出常規AT32F403系列、AT32F413系列、和AT32F415系列作為具有ADC輸入功能的任一GPIO引腳,輸入的電壓不能超過VDD+0.3V(VDDA與VDD須同電位),否則會由芯片內部干擾ADC輸入信號。只要是ADC輸入功能的GPIO,即使只當I/O輸入用途,如果輸入的電壓超過VDD+0.3V,也會干擾其它ADC通道轉換結果。如果存在此種高電壓,建議使用電阻分壓或減壓到小于VDD的電壓范圍。

其它AT32型號MCU則沒有以上限制(例如:AT32F403A、AT32F407、AT32F421、AT32F435/437等系列),所有具有ADC輸入功能的GPIO引腳都是耐5V引腳。這類引腳在未使用作ADC輸入信號而作為數字輸入時,需設置為浮空輸入、輸入上拉、或輸入下拉模式,就可以輸入高于VDD的電壓而不干擾ADC的操作。但使用者仍需注意輸入電壓不可超出5.5V。但作為ADC輸入使用設置為模擬模式時,則失去耐5V特性,使用者需注意輸入電壓不可超出VDD+0.3V。

在GPIO引腳輸入負電壓也會干擾ADC的轉換。注意輸入電壓不可低于-0.3V。

模擬輸入信號噪聲在采樣時間內,小而高頻率的信號變化可導致較大轉換誤差。此噪聲由電氣設備(例如電機、發動機點火、電源線)生成。它增加了不需要的信號,因此會影響模擬輸入源信號(例如:傳感器)。這樣一來,導致ADC轉換結果不準確。

采樣平均濾波

此方法是一個簡單的技巧,即通過軟件對模擬輸入多次采樣,取所有結果的均值。當模擬電壓不頻繁變化時,此技巧有助于消除模擬輸入上的噪聲。如果被測模擬信號產生不穩定的ADC值,軟件運算時則可以通過剔除大值和小值,選擇適當數量的待平均樣本執行平均。此數量取決于需要的精度、最低轉換速度。平均濾波法的優勢是可以在無任何硬件變更的情況下提高ADC精度。它的缺點是轉換速度和頻率響應較慢,相當于降低了有效采樣頻率。平均濾波法也針對不同需求發展出各樣差別,如:限幅濾波、中位值濾波、遞推平均濾波、消抖濾波及其組合等等的算法。使用者可根據信號特性和芯片資源選擇合適的數據平均方式。

添加外部濾波器

添加外部RC濾波器以消除高頻。無需使用昂貴的濾波器來處理頻率分量高于所涉頻率范圍的信號。這種情況下,截止頻率fC剛好高于所涉頻率范圍的相對簡單的低通濾波器將足以限制噪聲和混疊。使用與所涉最高頻率相同的采樣率足以,通常為fC的2至5倍。但添加了外部RC濾波器時,ADC的采樣時間和采樣間隔都需要重新評估,否則可能造成更大的量測誤差。請詳細參考第3章內容。模擬信號源阻抗的影響在源和引腳之間的模擬信號源的阻抗或串聯電阻(RAIN),可能會因為采樣時流入或流出引腳的電流而導致其上的電壓瞬間改變,這時ADC內部采樣保持電容充滿電所需要的時間會延長。如果采樣時間短于將內部采樣電容充分充放電所需的時間,則ADC轉換的數字值會與實際值有徧差。

關于模擬信號源具有高輸入阻抗特性或加入RC濾波器時,ADC的測量設置請詳細參考第3章內容。

CPU生成的內部噪聲當CPU(以及其他外設)操作時,會產生大量內部和外部信號變化,這些變化通過電容耦合傳輸到ADC外設。此類干擾影響ADC精度。

為使CPU(以及其他外設)對ADC的影響最小化,必須使采樣和轉換期間的數字信號變化量最小化(數字靜默)。使用下列方法之一可以實現這一點(在采樣和轉換時間內實現):

內部CPU變化量最小化(CPU停止,等待模式)

溫度影響溫度對ADC精度有重要影響。它主要產生兩種重要誤差:偏移誤差漂移和增益誤差漂移。建議使用內部溫度傳感器和ADC看門狗,以在溫度變化達到給定值時重新校準ADC。I/O引腳串擾由于I/O之間的電容耦合,切換I/O可能會在ADC的模擬輸入中產生一些噪聲。彼此距離很近或交叉的PCB走線可能會產生串擾。內部切換數字信號和I/O會產生高頻噪聲。由于電流浪涌,切換高灌電流I/O可能導致電源電壓小幅下降。

PCB上與模擬輸入走線交叉的數字走線可能影響模擬信號。通過讓接地走線來屏蔽模擬信號,可以減少串擾產生的噪聲。PCB布線時,應考慮對ADC輸入信號給予屏蔽,可在信號線周圍鋪銅并就近接地,同時應盡量縮短走線距離。另外在ADC采樣和轉換時間內實現I/O引腳變化量最小化,對減小對ADC的干擾很有幫助。

EMI產生的噪聲鄰近電路產生的電磁輻射可能在模擬信號中產生高頻噪聲,此時PCB走線相當于天線接收干擾噪聲。使用者可以通過在可能的發射源和接收器之間提供物理隔離,或通過適當的接地和屏蔽措施對它們進行電氣隔離。

沿敏感模擬信號布置接地走線,在PCB上提供屏蔽。雙層PCB的另一側也應具有接地板。這樣可以防止干擾和I/O串擾影響信號。應使用屏蔽線纜將遠距離信號(例如:傳感器)連接到PCB或注意盡可能縮短PCB上信號的路徑長度。晶振、時鐘以及存在快速變化的信號線盡量遠離ADC輸入信號。

ADC輸入源阻抗對測量的影響和正確的設置方式

SAR ADC的量測要求設置足夠的采樣時間讓ADC內采樣電路充分充、放電,以獲得轉換的準確性。多通道間切換的使用也是同樣道理,足夠的采樣時間可以避免輸入通道間的交互干擾(crosstalk)。為了計算估計的采樣時間,圖3給出一個能近似ADC采樣線路的等效阻值和容值(包含:模擬多工器、模擬開關、寄生電容、采樣電容…等)的電路圖。圖3. 輸入級與ADC簡化示意圖 - 采樣和保持電路

其中模擬信號輸入源對ADC的輸入阻抗(RAIN),直接與ADC采樣時間有關,影響ADC轉換結果甚巨。未考慮輸入阻抗使得ADC輸入的外部器件與軟件設置的采樣時間不批配,往往是造成ADC使用問題的原因。以下分別針對信號源具有一般輸入阻抗或高輸入阻抗,分別探討如何正確設置ADC的軟、硬件。

一般輸入阻抗的測量設置

VC是內部CADC電容兩側的電壓(請參見圖4)。對于給定的采樣tC,可以考慮VAIN=VREF+所對應的tC需要采樣時間是最大值,因為此時CADC電容需要最多時間從0V充電到VAIN。因此,VAIN=VREF是驗證最大源電阻時要考慮的最壞情況。通過軟件設置增加采樣時間或降低ADC時鐘頻率可等效加長采樣時間,當采樣時間越長越可以獲得好的轉換結果。圖4. 模擬信號源對采樣和保持電路充電示意圖

一般我們假設允許的最大誤差等于1 LSB,照RC充放電公式:

其中V(t)帶入VREF×(1-1/212),VAIN帶入VREF;而時間常數τ=(RAIN+RADC)xCADC,采樣時間大于8.32x(RAIN+RADC)xCADC就可達到1LSB誤差之內。若使用者要求較低的準確度,可進一步增大允許的外部電阻RAIN。

高輸入阻抗的測量設置

ADC輸入信號源常有存在高阻特性。例如系統電池電壓經電阻分壓后輸入給ADC采集,因分壓電阻會形成一個直流耗電路徑,為節省耗電,分壓電阻串常使用100 kΩ到1 MΩ的阻值組合而成。又或者有些傳感器本身為弱電流輸出,通過外接一大電阻轉換為電壓后輸入給ADC。以上硬件往往都無法以上一節方法調試出適合的采樣時間,(例如軟件已設置采樣時間至最大值仍無法獲得準確的轉換值,或降低ADC時鐘又使得整體采樣間隔太長,)此時可以在ADC輸入通道前增加運算放大器,可以提高輸入驅動能力,如圖5。此方案可大大縮短ADC的采樣時間以及采樣間隔,但缺點是增加了器件成本。另外在設計前置放大器時,必須注意可能額外產生的誤差(例如額外的偏移、放大器增益穩定性或線性、頻率響應)。并且若未慎選運算放大器,這些放大器的誤差會成為另外測量誤差的來源。圖5. ADC輸入通道前增加運算放大器示意圖

若硬件電路不容許增加運算放大器,無法通過提高采樣時間滿足要求,此時還可以采用外接電容作為電荷存儲器的方法。

SAR ADC內部采樣保持電容在采樣開關接通后,在采保電容穩定時間內需要一個足夠的充放電電流,而通常實際的信號電路若具有較高的輸入阻抗,往往不能提供足夠大的電流快速為ADC內采樣電容充電。為此大部分的應用都采用在ADC輸入管腳到地接一個外部大電容作為一個電荷存儲器,即圖3中的CEXT。這個電容參與采樣時電路的充放電過程,以便向SAR ADC采樣電容提供充足的電荷,而對內部采樣電容進行快速充電,并且穩定ADC輸入點的電壓。此CEXT與RAIN組成的RC濾波器也順帶限制到達ADC輸入端的帶外噪聲,同時也幫助衰減ADC輸入端中開關電容頻繁切換和通斷的反沖噪聲影響。當然此RC濾波器也限制了VAIN信號源的截止頻率。

計算CEXT

當采樣開關接通后,會在CEXT和CADC之間有一段電荷重新分配的過程,這一段RC時間常數主要是由RADC的最大阻值和CADC的最大容值決定的。在考慮CEXT和CADC之間電荷分配時,CPAD因為相對微小且與CEXT并聯,是可以忽略的。電荷分配的算式是基于「分配前的全部電荷等于分配后的全部電荷」。假設現在CADC是完全放電的,而CEXT儲存著和VAIN一樣的電壓。VC(分配后的電壓)定規為VAIN的0.999939倍,這個意義是VC最后徧差在VAIN的1 LSB之內,以12位解析度來記算。 例如CADC=15 pF,CEXT=4095x15 pF=61.4 nF。這是CEXT的絕對最小值。在實際選擇器件值時必需確認考慮到器件誤差和老化因素,選擇大一點的值是可以的,如68 nF。如果電容值選擇再大,其實對采樣時間要再縮短并沒有實質幫助,反而限制了ADC輸入信號的頻寬。但如果一個12位的ADC配罝CEXT<4095xCADC,反而會要求相當大的采樣時間讓CADC充電足夠。所以若CEXT<4095xCADC而且使用者若沒有需要anti-aliasing濾波器的情況下,還不如不要加CEXT。若要求的精準度沒有這么高,CEXT的數值可以照前面公式減小,這時ADC輸入信號的頻寬就增大了。相反的若要求精準度,CEXT就必須提高了,就要付出ADC采樣時間間隔要拉大,ADC輸入信號的頻寬縮小的代價。

例如CADC=15 pF,CEXT=4095x15 pF=61.4 nF。這是CEXT的絕對最小值。在實際選擇器件值時必需確認考慮到器件誤差和老化因素,選擇大一點的值是可以的,如68 nF。如果電容值選擇再大,其實對采樣時間要再縮短并沒有實質幫助,反而限制了ADC輸入信號的頻寬。但如果一個12位的ADC配罝CEXT<4095xCADC,反而會要求相當大的采樣時間讓CADC充電足夠。所以若CEXT<4095xCADC而且使用者若沒有需要anti-aliasing濾波器的情況下,還不如不要加CEXT。若要求的精準度沒有這么高,CEXT的數值可以照前面公式減小,這時ADC輸入信號的頻寬就增大了。相反的若要求精準度,CEXT就必須提高了,就要付出ADC采樣時間間隔要拉大,ADC輸入信號的頻寬縮小的代價。

計算RAIN

所有對外部電容CEXT充電的阻值總合程為RAIN,也就是從CEXT看到驅動信號源的等效阻值。當RAIN變大,RAIN和CEXT所型成的截止頻率就會變低。這表示當輸入信號開始變動到CEXT電荷穩定的這段反應時間會增加。要準確度穩定達到12位解析度誤差1 LSB之內,RC線路的時間常數要求為:ln(212)=8.32倍。Cext和Rain型成的截止頻率為: 以前段CEXT=62?nF為例,若RAIN=200Ω,截止頻率可達9.7kHz;但若RAIN=20kΩ,僅可接受97Hz。源的頻率若超以上截止頻率,ADC轉換結果會不準確。注意此時程序不得將ADC設定為連續模式,而應設定為單點模式或以定時器間隔觸發轉換,軟件必 須確保兩次轉換之間的時間間隔等于或大于1/f。

以前段CEXT=62?nF為例,若RAIN=200Ω,截止頻率可達9.7kHz;但若RAIN=20kΩ,僅可接受97Hz。源的頻率若超以上截止頻率,ADC轉換結果會不準確。注意此時程序不得將ADC設定為連續模式,而應設定為單點模式或以定時器間隔觸發轉換,軟件必 須確保兩次轉換之間的時間間隔等于或大于1/f。

采樣時間不足的后果

若遵照計算CEXT的方式在ADC輸入放置足夠大的CEXT,要使CADC穩定所需要的時間就顯得非常短。另外也只有一個情況之下可以不需要CEXT就是RAIN很小的時候。一般來說RAIN很小是因為傳感器有輸出緩沖極,這是RAIN都小于100Ω。以上情況采樣時間都容易滿足。

不足的采樣時間會造成ADC通道間互相干擾。就如本文開頭所討論的,這是因為電荷從一個通道累積在CADC上并轉移到另一個通道,造成通道間互相影響。

信號源高阻的后果

通常造成以上所述通道間干擾的原因是因為信號源輸入阻抗太高了。若要達到1 LSB的準確度,就必需在各通道轉換中間加入延時,后果就是整體的轉換時間變慢。如果沒有加上CEXT或著電容值太小,而采樣時間又不足,ADC轉換出來的結果因為通道間干擾而永遠達不到1 LSB的準確度。

關于輸入阻抗匹配的其他建議

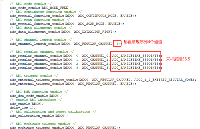

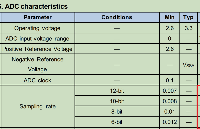

以近期ADC朝向低功耗、高采樣頻率、并復雜功能的方向進行設計,ADC的采樣行為已經不是如上文以一階簡易的RADC和CADC模型可以仿真的了,因此近期普遍ADC規格中只提供CADC的典型值,而不再提供RADC數值。取而代之的是ADC輸入信號阻抗(RAIN)與采樣時間(ts)的對應關系表,如下表所示。(下表自AT32F403A系列數據手冊截取。)表1. fADC=28MHz時的最大RAIN(1) (1) 由設計保證。在可以得知ADC信號源的輸入阻抗時,使用者不需進行計算,只要照表格指示透過軟件設置足夠的采樣時間,一般都會得到合理的ADC轉換值。但在一般情況下,使用者常常難以直接或間接得知ADC輸入信號的阻抗時,最好的方法是逐步調試軟件采樣時間。

(1) 由設計保證。在可以得知ADC信號源的輸入阻抗時,使用者不需進行計算,只要照表格指示透過軟件設置足夠的采樣時間,一般都會得到合理的ADC轉換值。但在一般情況下,使用者常常難以直接或間接得知ADC輸入信號的阻抗時,最好的方法是逐步調試軟件采樣時間。

使用者可以依照下述步驟調試ADC的采樣時間:

- 首先設置ADC時鐘頻率為最高值,并設置采樣周期為最大值;

- 嘗試ADC轉換并檢視轉換結果;

- 若轉換數值符合預期,則可逐步調試減小采樣周期并觀察ADC轉出值,以求得足夠而不過長的采樣時間;

- 若最大采樣時間所得轉換值不符合預期,使用者需要降低ADC時鐘頻率,或是照著前文計算并外加合適大小的CEXT;硬件設置完成后再修改軟件設置,逐步調試出合適的采樣時間及采樣間隔。

另外若采樣間隔時間許可時,采取一些軟件技巧也會提高ADC轉換的準確度,例如:

- 采用平均法、移動平均法、或中值濾波;

- 對同一ADC通道采樣兩次,將第一次的值丟棄而使用第二次的采樣的值。此種方式可以消除輸入源內阻過大而在不同通道切換時,上一個通道的電壓來不及從采樣電阻放電而累積的電荷,導 致影響下一個通道的轉換值;

- 若ADC輸入信號大約在0V到VREF+/2時,可交替轉換該ADC輸入通道和內部VINTRV源,也可達到讓采樣電阻有足夠時間充放電的效果,避免通道間干擾。若有內部VSSA通道,交替轉換ADC輸入通道和內部VSSA通道效果會更好且省時。因為讓ADC采樣電路放電到VSSA比起充放電到VINTRV可以以更快的采樣時間達成。

其它ADC應用指南

內部參考電壓VINTRV的設置目的與使用方式

內部參考電壓(VINTRV)為ADC提供了一個穩定的電壓輸出。VINTRV內部連接到ADC1_IN17輸入通道上,用于將VINTRV的輸出轉換為數字數值。

VINTRV是一個芯片內部的一個恒定電壓信號源,按規格為1.2V±3.3%,在所有VDDA操作電壓范圍內都維持在此穩定電壓規格內,不隨VDDA電壓變動而變化。因此,VINTRV在ADC的外部VREF+(通常與VDDA同電源)的電壓未知或VVREF+電壓會變動時(例如:使用電池電源),可用來參照推算出VREF+或VDDA電壓以及各ADC_IN輸入的準確絕對電壓值。

例如:選定VINTRV通道經ADC轉換后數值若為1650(Code_VINTRV),就可以推算出電壓滿格的VREF+或VDDA的電壓為1.2x4096/1650=2.979V。此時若另一選定的ADC_IN外部通道轉換出來的數值為800(Code_VAIN),就可采用以下兩種計算方式:1.2x800/1650或2.979x800/4096,計算出此外部信號電壓VAINx為0.582V。

以上范例使用公式如下:

VREF+或VDDA=(VINTRV)x4096/(Code_VINTRV)VAINx=(VINTRV)x(Code_VAIN)/(Code_VINTRV)VAINx=VREF+或VDDAx(Code_VAIN)/4096

使用者可以根據應用系統電源的特性,決定對VINTRV轉換次數及間隔。若電源為電壓未知但不變動,可于系統上電后并在ADC初始化并校正后,一次性對VINTRV轉換;若電源為變動電壓,就要根據電源變動速度和系統需求決定對VINTRV轉換間隔,多次對VINTRV轉換并更新此參照值,甚至需要對ADC重新校正。另外溫度變化也可能使電源情況有改變,也可參考2.2.6節內容啟動對VINTRV轉換。因VINTRV為內部弱電壓源,ADC進行采樣時需要足夠時間讓VINTRV為采樣電路正確充放電,使用者需確實遵照數據手冊中的TS_INTRV參數為VINTRV設置足夠的采樣時間,以獲得正確的轉換數值。

關于雅特力雅特力科技于2016年成立,是一家致力于推動全球市場32位微控制器(MCU)創新趨勢的芯片設計公司,專注于ARM Cortex-M4/M0+的32位微控制器研發與創新,全系列采用55nm先進工藝及ARM Cortex-M4高效能或M0+低功耗內核,締造M4業界最高主頻288MHz運算效能,并支持工業級別芯片工作溫度范圍(-40°~105°)。雅特力目前已累積相當多元的終端產品成功案例:如微型打印機、掃地機、光流無人機、熱成像儀、激光雷達、工業縫紉機、伺服驅控、電競周邊市場、斷路器、ADAS、T-BOX、數字電源、電動工具等終端設備應用,廣泛地覆蓋5G、物聯網、消費、商務及工控等領域。

-

mcu

+關注

關注

146文章

17128瀏覽量

351002

發布評論請先 登錄

相關推薦

如何校準adc以提高精度

過采樣提高12位ADC的精度

AT32講堂088 | 雅特力AT32F402/F405時鐘配置

AT32講堂087 | 雅特力AT32 IDE快速入門指南

AT32講堂085 | 雅特力AT32 MCU HICK時鐘校準

如何通過GD32 MCU內部ADC參考電壓通道提高采樣精度?

AT32講堂032 | 如何提高AT32 MCU ADC轉換精度

AT32講堂032 | 如何提高AT32 MCU ADC轉換精度

評論