來源:半導體芯科技

工程師們正在尋找從復雜模塊中有效散熱的方法。

將多個芯片并排置于同一封裝中可以緩解熱問題,但隨著公司進一步深入研究芯片堆疊和更密集的封裝,以提高性能和降低功率,他們正在與一系列與熱有關的新問題作斗爭。

先進封裝芯片不僅能滿足高性能計算、人工智能、功率密度增長等的需求,同時先進封裝的散熱問題也變得復雜。因為一個芯片上的熱點會影響到鄰近芯片的熱量分布。芯片之間的互連速度在模塊中也比在SoC中要慢。

西門子數字工業軟件公司電子和半導體行業負責人John Parry說:"在世界進入多核等領域之前,你面對的是一個芯片,其最大功率約為每平方厘米150瓦,這是一個單點熱源。你可以在所有三個方向上散熱,所以你可以達到一些相當高的功率密度。但是,當你有一個芯片,把另一個芯片放在它旁邊,然后再把另一個芯片放在它旁邊,它們會相互加熱。這意味著你不能容忍每塊芯片有相同的功率水平,這使得熱能挑戰變得更加困難"。

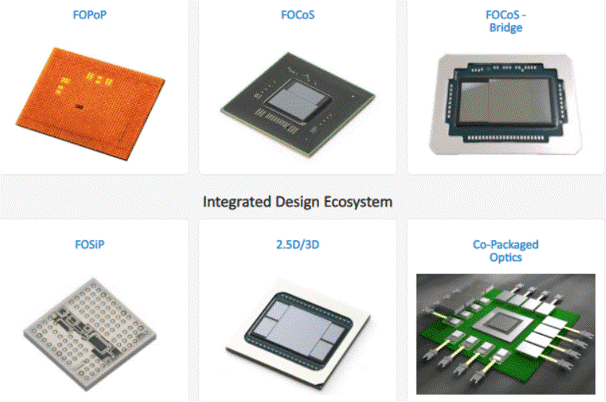

這是3D-IC堆疊在市場上進展緩慢的主要原因之一。雖然從電源效率和集成的角度來看,這個概念是有意義的——-在3D NAND和HBM中運行良好——但當邏輯被包括在內時,就是另一回事了。邏輯芯片產生熱量,邏輯越密集,處理元件的利用率越高,熱量就越大。這使得邏輯堆疊變得罕見,這解釋了2.5D倒裝芯片BGA和扇出設計的流行(見圖1)。

圖1:為了滿足功率密度、帶寬和熱耗散的要求,高密度VIPack平臺包括六種架構中基于RDL和TSV的互連。資料來源:ASE。

01選擇正確的封裝

對于芯片設計者而言,封裝方式多種多樣。但芯片集成的性能至關重要。硅、TSV、銅柱等組件都有不同的熱膨脹系數(TCE),這影響了組裝產量和長期可靠性。

若你要以更高頻率進行開啟和閉合,那么有可能遇到熱循環的問題。印刷電路板、焊球和硅都會以不同的速度膨脹和收縮。因此,在封裝的角落里看到熱循環故障是很正常的,那里的焊球可能會開裂。因此,人們可能會在那里安置額外的地線或額外的電源。

目前流行的帶有CPU和HBM的倒裝BGA封裝面積約為2500 平方毫米。Onto Innovation軟件產品管理主管Mike McIntyre說:“我們看到一個大芯片可能會變成四個或五個小芯片。所以必須擁有更多的I/O,才能使得這些芯片相互通信。因此你可以分配熱量。

最終,散熱是一個在系統層面才能處理的問題,它伴隨著一系列的權衡。

事實上,有些器件非常復雜,以至于很難輕易更換元件,以便為特定領域的應用定制這些設備。這就是為什么許多先進的封裝產品是用于非常大批量或價格彈性的元件,如服務器芯片。

02芯片模塊模擬和測試的進展

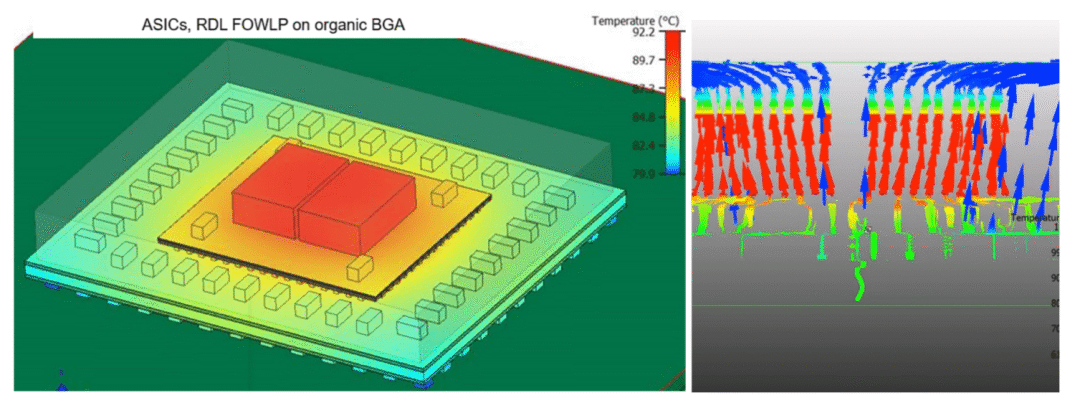

盡管如此,工程師們正在尋找新的方法,在封裝模塊制造之前進行封裝可靠性的熱分析。例如,西門子提供了一個基于雙ASIC的模塊的例子,該模塊在BGA封裝的多層有機基材上安裝了一個扇出式再分布層(RDL)。它使用了兩個模型,一個用于基于RDL的WLP,另一個用于多層有機襯底的BGA。這些封裝模型是參數化的,包括在引入EDA信息之前的襯底層堆疊和BGA,并能實現早期材料評估和芯片放置選擇。接下來,EDA數據被導入,對于每個模型,材料圖能夠對所有層中的銅分布進行詳細的熱描述。最終的熱耗散模擬(見圖2)考慮了所有的材料,除了金屬蓋、TIM和底部填充材料。

圖2:兩個ASIC的熱力模型,采用RDL扇出式WLP和有機BGA的單獨熱力模型,顯示了熱量通過基板和互連并向金屬蓋上升的頂部和橫截面圖。資料來源。西門子

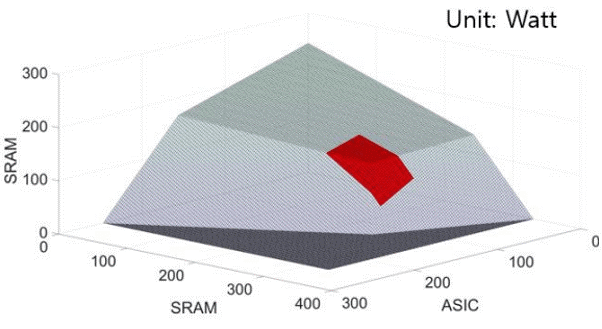

JCET技術營銷總監Eric Ouyang與JCET和Meta的工程師一起,比較了單片芯片、多芯片模塊、2.5D插板和3D堆疊芯片與一個ASIC和兩個SRAM的熱性能。蘋果對蘋果的比較使服務器環境、帶真空室的散熱器和TIM保持不變。在熱方面,2.5D和MCM比3D或單片芯片表現更好。Ouyang和JCET的同事設計了一個電阻矩陣和功率包絡圖(見圖3),可以在早期模塊設計中使用,以確定在耗時的熱模擬之前,不同芯片的輸入功率水平和設定的結溫是否可以可靠地結合。如圖所示,一個安全區域突出了每個芯片上滿足可靠性標準的功率范圍。

Ouyang解釋說,在設計過程中,電路設計師可能對放置在模塊中的各種芯片的功率水平有一個概念,但可能不知道這些功率水平是否在可靠性范圍內。該圖確定了一個小芯片模塊中最多三個芯片的安全功率區域。該團隊已經為更多的芯片開發了一個自動功率計算器。

圖3:在一個2.5D內襯布局中,紅色區域代表了一個ASIC和兩個SRAM芯片的安全功率水平,保持Tj-Ta<95℃。資料來源。JCET

03量化熱阻

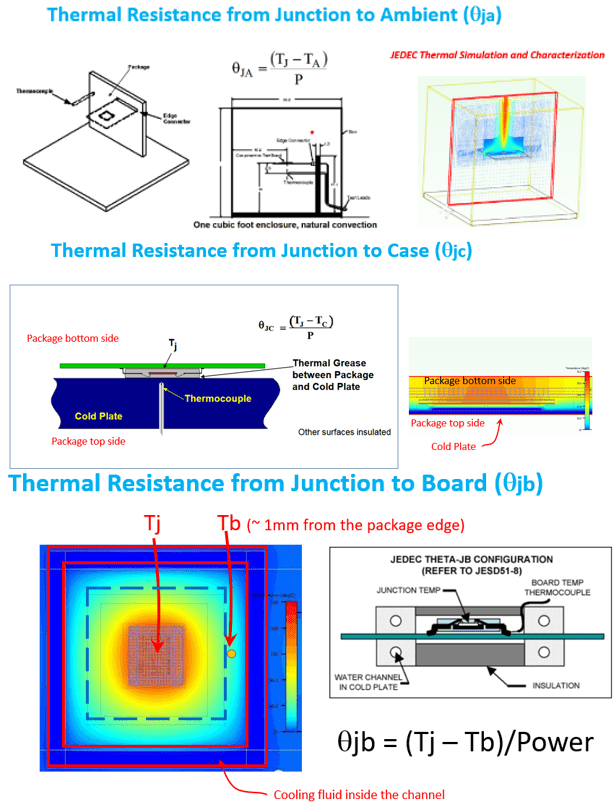

我們能夠理解熱量是如何通過硅芯片、電路板、膠水、TIM或封裝蓋進行傳導,同時采用溫差和功率函數這種標準方法,來跟蹤溫度和電阻值。

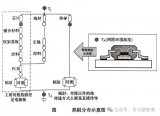

"JCET的Ouyang說:"熱路徑由三個關鍵值來量化--從器件結點到環境的熱阻,從結點到外殼[在封裝頂部]的熱阻,以及從結點到電路板的熱阻。他指出,至少,JCET的客戶需要θja、θjc和θjb,然后他們在系統設計中使用。他們可能會要求一個給定的熱阻不超過一個特定的值,并要求封裝設計提供該性能。(詳見JEDEC的JESD51-12,報告和使用封裝熱信息的指南)。

圖4:從芯片到封裝到電路板的熱阻可量化封裝的散熱能力。資料來源。JCET

熱模擬是探索選擇和搭配材料的最經濟的方法。通過對工作狀態下的芯片進行模擬,我們通常會發現一個或多個熱點,因此我們可以在熱點下方的基材中加入銅,以利散熱;或改變封裝材料,增加散熱器。系統集成商可能會指定熱阻θja、θjc和θjb不得超過某些數值。通常情況下硅結點溫度要保持在125℃以下。

在模擬完成之后,封裝廠進行實驗設計(DOE),以得出最終的封裝方案。

04選擇TIM

在封裝中,90%以上的熱量通過封裝從芯片的頂部散發到散熱器,通常是以陽極氧化鋁為基礎的垂直鰭片。具有高導熱性的熱界面材料(TIM)被放置在芯片和封裝之間,以幫助傳遞熱量。用于CPU的下一代TIM包括金屬片合金(如銦和錫),以及銀燒結錫,其傳導率分別為60W/m-K和50W/m-K。

隨著廠商將SoC向chiplet工藝過渡,所以需要有更多不同性質和厚度的TIM。

Amkor公司的高級研發總監YoungDo Kweon表示,對于高密度系統來說,芯片和封裝之間的TIM的熱阻對封裝模塊的整體熱阻影響更大。功率趨勢正在急劇增加,特別是對于邏輯,所以我們關注保持低結溫以確保半導體可靠運行。雖然TIM供應商為其材料提供熱阻值,但實際上,從芯片到封裝的熱阻(θjc),受組裝過程本身的影響,包括芯片和TIM之間的結合質量和接觸面積。他指出,在受控環境中用實際的組裝工具和粘合材料進行測試,對于了解實際的熱性能和選擇最佳的TIM供客戶鑒定至關重要。

空隙是一個特別的問題。西門子公司Parry說“封裝中的材料的運用,是一個大挑戰,我們已經知道了粘合劑或膠水的材料屬性,以及材料潤濕表面的方式,會影響材料呈現的整體熱阻,即接觸電阻。這在很大程度上取決于材料如何流入表面,而不產生缺陷。如果有遺漏的地方沒有被膠水填充,就會對熱流造成額外的阻力。”

05以不同方式處理熱問題

芯片制造商正在想方設法解決散熱問題。Keysight Technologies的內存解決方案項目經理Randy White說:“封裝方式不變,如果你將芯片尺寸面積縮小四分之一,速度就會加快。這可能會出現一些信號完整性差異。因為外部封裝的鍵合線會進入芯片,線越長電感越大,所以存在電氣性能這一部分。那么,如何在一個足夠小的空間里消耗那么多能量的?這是另一個需要研究的關鍵參數。”

這導致了對前沿的鍵合研究的大量投資,似乎關注在混合鍵合上。但是混合鍵合的成本很高,它仍然局限于高性能處理器類型的應用,臺積電是目前唯一提供這種技術的公司之一。不過,在CMOS芯片或硅基氮化鎵上結合光子的前景很廣闊。

06結論

先進封裝的初始理念是,它將像樂高積木一樣工作--在不同工藝節點上開發的芯片可以組裝在一起,熱問題將得到緩解。但這是有代價的。從性能和功率的角度來看,信號需要傳播的距離是很重要的,而電路總是開著,或者需要保持部分開著,都會影響熱性能。為了提高產量和靈活性而將芯片分成多個部分,并不像看起來那么簡單。封裝中的每一個互連必須被優化,熱點不再局限于單個芯片。

早期的建模工具可用于排除芯片的不同組合,為復雜模塊的設計者提供了很大的推動力。在這個功率密度不斷提高的時代,熱模擬和新TIM的引入仍將必不可少。

-

芯片

+關注

關注

455文章

50714瀏覽量

423159 -

封裝

+關注

關注

126文章

7873瀏覽量

142896

發布評論請先 登錄

相關推薦

ads1291 QFN封裝的散熱PAD接AVSS還是DGND?

塑封、切筋打彎及封裝散熱工藝設計

BGA封裝對散熱性能的影響

LM1876非隔離封裝,散熱片為什么為負電壓?

飛凌嵌入式-ELFBOARD 從七種芯片封裝類型,看芯片封裝發展史

如何解決芯片封裝散熱問題

如何解決芯片封裝散熱問題

評論