1 前言

Semidrive X9H 主平臺的轉接板 PCB 布線時,涉及了 LVDS 高速差分線,不僅要求信號線的正端和負端信號線寬及線間距保持一致,還需要對差分信號線進行阻抗控制。控制差分信號線的阻抗,對高速數字信號的完整性是非常重要的,因為差分阻抗直接影響信號帶寬、信號抖動和信號線上的干擾電壓,如果不進行控制,信號質量會嚴重下降。所以在制版時需要計算差分信號的阻抗匹配,從而完成制版。

本文旨在通過SI9000 軟件來計算轉接板 LVDS 阻抗匹配做一個簡單的介紹。

2 Polar Si9000 特性阻抗計算

2.1 Polar Si9000 軟件安裝

解壓并運行exe啟動安裝進程。

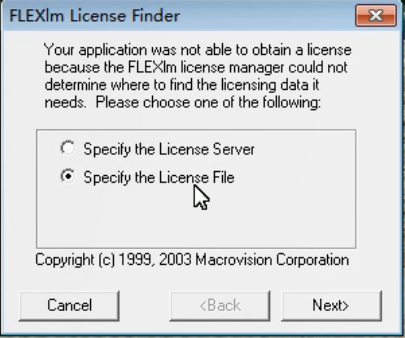

exe 完成后桌面會生成 Shortcut to Si9000 快捷鍵,雙擊快捷鍵會彈出如下窗口,選擇第二個“Specify the License File”進入下一步。

圖2-1 SI9000 指定 License 文件

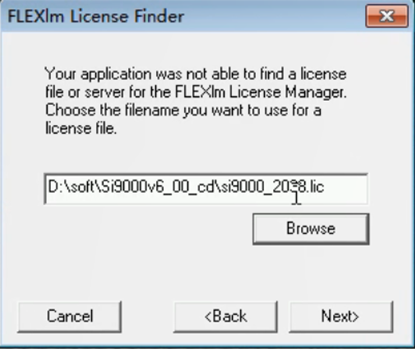

點擊“Browse”選擇安裝文件里的“lic”文件,點擊 NEXT 。

圖2-2 SI9000 添加 “si9000_2038.lic”文件

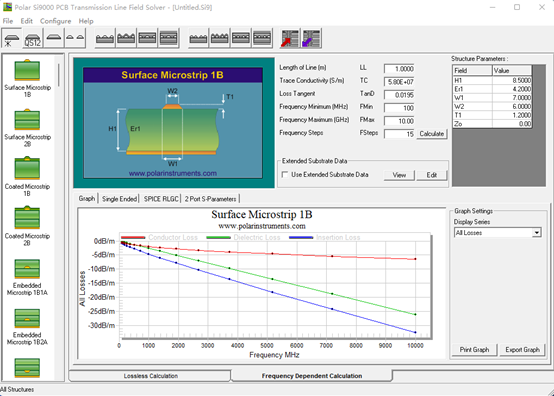

Polar SI9000 軟件安裝成功,啟動并顯示主界面

圖2-3 SI9000 添加 “si9000_2038.lic”文件

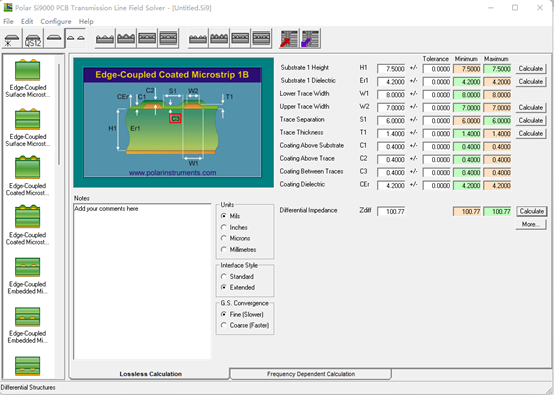

2.2 了解 Polar Si9000 軟件界面

首先對 Si9000 界面有一個初步的了解,熟悉常用的幾個模板的使用,學會了模板,也就基本了解了阻抗匹配。

圖2-4 Si9000 軟件主界面介紹

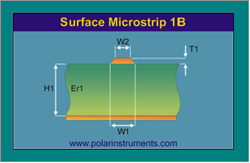

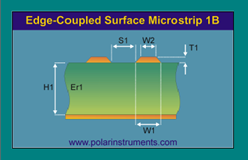

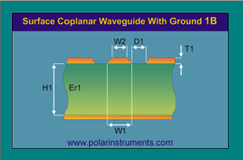

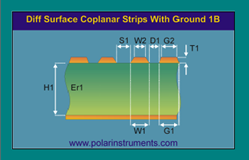

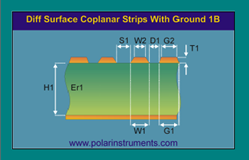

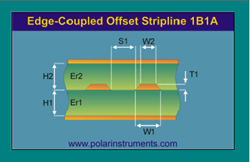

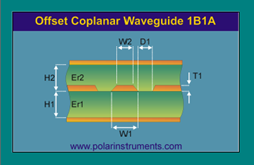

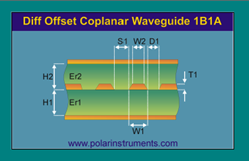

Si9000 軟件設計參數:

H1 ---- 外層到次外層之間的介質厚度。(PP 片或者板材,不包括銅厚)。

Er1 ---- 這里是PP的介電常數。(例如:板材4.5,P 片4.2)。

W1 ---- 阻抗線下線寬。成品線寬,也就是我們的畫圖設計走線寬度。

W2 ---- 阻抗線上線寬。走線頂端寬度,表示側蝕的意思,外層成品1oz的銅厚一般按1mil的側蝕量計算。

S1 ---- 阻抗線間距。

T1 ---- 阻抗線銅厚或成品銅厚=基板銅厚+電鍍銅厚。

C1 ---- 基材阻焊厚度。走線間的基材上的阻焊厚度,注意走線間隙一般比較小,容易產生溝壑效果,這里的阻焊厚度稍微厚一點。

C2 ---- 線面阻焊厚度(后加工)。

C3 ---- 基板上面的綠油厚度

CEr1 ---- 阻焊介電常數。

Zo ---- 需要的阻抗值。

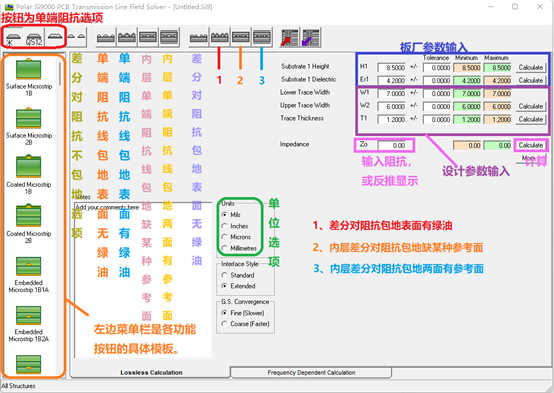

2.3 Polar Si9000 常見的阻抗模型

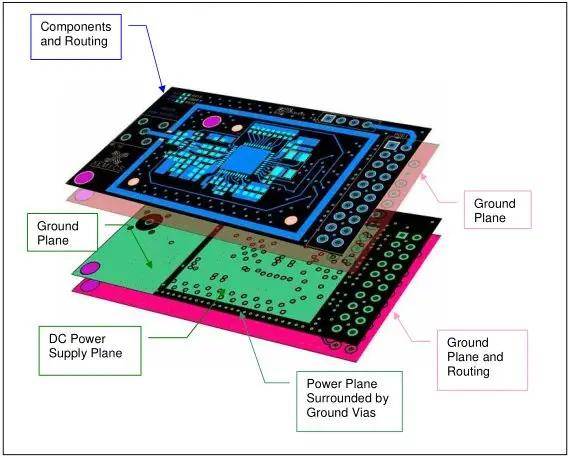

在中低端的線路板中涉及的一般少一些,主要是雙面板、四層板、以及以上的層數的多層板。多層板的一般居多。阻抗一般分為6種:單端阻抗線、差分阻抗線、單端共面地阻線、差分共面地阻抗線、層間差分阻抗線、共模阻抗。

外層單端阻抗

外層差分阻抗

外層單端共面地阻抗

外層差分共面地阻抗

內層單端阻抗 <兩面屏蔽>

內層單端阻抗 <兩面屏蔽>

內層單端共面地阻抗 <兩面屏蔽>

內層差分共面地阻抗 <兩面屏蔽>

圖 2-5 常見的阻抗模型

3 X9H 主平臺計算 LVDS 阻抗匹配介紹

3.1 確定差分線的阻抗以及 PCB 板材參數

首先,查詢到 LVDS 差分線的特征阻抗是100Ω。在設計PCB時,需要按特定的參數布線,使得阻抗匹配到 100Ω 左右,否則會有信號反射,造成信號質量下降。

其次,X9H 主平臺轉接板 LVDS 制版說明中定義了:板材 FR-4,TG150;板厚 1.6mm;銅箔厚度:內層1 oz,外層0.5 + Plating oz;最小線寬8 mil;最小線距6 mil;最小孔徑10 mil。

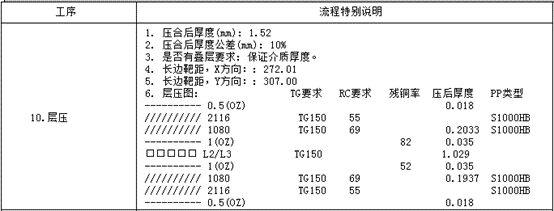

四層板1.6mm厚度的 PCB 層疊參數如下:

圖3-1 四層板1.6mm厚度的 PCB 層疊參數

從上圖中可以看出,我們轉接板 LVDS 是四層板,2116+1080疊層結構,板材的介電常數為4.2,頂層/底層和相鄰的中間層間距是0.1mm(約4mil),頂層銅厚度為0.035mm(約1.4mil),另外還有一些阻焊的參數,有了這些參數,就可以在 SI9000中計算布線的參數了。

3.2 LVDS 差分阻抗匹配參數計算

LVDS 差分阻抗匹配打開 SI9000 后,選擇差分對的微帶線模型,這個模板含義是信號線與 GND 層相鄰,并且信號上蓋有綠油。

圖3-2差分對的微帶線模型選擇

圖3-3阻抗匹配計算步驟

在計算阻抗前,我們先要了解清楚幾個參數,疊層參數,及板廠的板材,介電常數,綠油,PP 片厚度等參數。

首先常用的 PP 有:106=0.05MM=1.96mil,1080=0.07MM=2.75mil,2116=0.12MM=4.72mil,7628=0.19MM=7.4mil。根據板廠提供的板材確定介質厚度。

其次常用 FR4 芯板厚度有:2.4MIL,4mil,6mil,6.5mil,5.12mil,9.1mil,10mil,10.43mil,13miil,14.37mil等等厚度。不同的FR4芯板的介質也是不同的,常見的有4.2,4.4,4.5,這些差數只能通過板廠得知。

圖3-4 轉接板 LVDS 阻抗計算

3.3 特性阻抗的關鍵和方法:

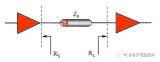

在高速電路中,如 USB、HDMI、DDR、LVDS 設計中往往要注意阻抗匹配問題,高頻信號在傳輸線中傳播時所遇到的阻力稱為特性阻抗,包括容抗,感抗,阻抗。為了保證信號在傳輸過程中不發生反射現象,信號盡量保持完整,降低傳輸損耗,要對印刷電路板進行阻抗匹配。阻抗匹配的目的主要在于傳輸線上所有高頻微波信號都能達到負載點,不會有信號反射回源頭。其中通常情況下,USB/DDR 的阻抗值保持在90Ω±10%。HDMI/LVDS 保持在100Ω±10%。

影響阻抗的關鍵因素主要有:線寬(W),線距(S),線厚(T),介質常數(Dk/Er),介質厚度(H),那么阻抗和線寬(W),線距(S),線厚(T),介質常數(Dk/Er)成反比,和介質厚度(H)成正比。

阻抗匹配的方法:1.憑經驗值;2.交給PCB廠商;3.結合SI9000進行系統的理論計算。

-

pcb

+關注

關注

4319文章

23080瀏覽量

397507 -

轉接板

+關注

關注

0文章

38瀏覽量

10473

發布評論請先 登錄

相關推薦

使用LP875230C-Q1 和 LP87565V-Q1 的 Semidrive X9H 電源設計

PCB阻抗匹配過孔的多個因素你知道哪些?

阻抗匹配有煩惱?來嘮一嘮~

高速差分信號阻抗匹配詳解

阻抗匹配的原理分析?

求助,關于STM32H750XB的RGB LCD接口阻抗匹配的疑問求解

光纖溫度傳感器測試阻抗匹配器內部溫度技術方案

無源探頭的阻抗匹配如何操作

為什么要阻抗匹配?怎么進行阻抗匹配?

學技術 | 基于 Semidrive X9H 主平臺的 轉接板 LVDS 計算阻抗匹配介紹

學技術 | 基于 Semidrive X9H 主平臺的 轉接板 LVDS 計算阻抗匹配介紹

評論