電路中或傳輸線上的阻抗失配會產生反射,回到信號源。

當信號反射時,向末端負載傳輸的功率就會減少。

阻抗匹配發揮了一種雙重作用,即通過抑制反射使功率傳輸到負載。

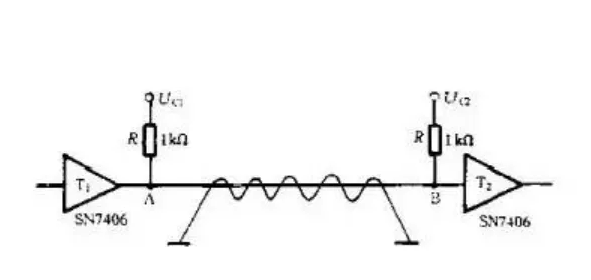

每當電磁信號沿著傳輸線傳播時,都有可能從傳輸線和負載器件之間的接口上反射回來。負載可以是任何東西:另一段傳輸線、集成電路、天線......任何有明確阻抗的東西都是負載。當阻抗失配時,就會給信號帶來災難性的影響,導致在傳輸線末端測得振蕩響應或階梯式響應。

這種效應從何而來,如何通過阻抗匹配來加以解決?雖然信號反射和阻抗失配存在關聯,但在線路上觀察到的振鈴效應往往解釋不清,也很難歸納。在本文中,我們將詳細解釋由于互連中的阻抗失配而導致的信號反射有哪些影響。

端接線路上出現信號反射的原因

根據定義,傳輸線上的阻抗失配會導致信號反射;任何支持波在線性介質中傳播的結構都會這樣。信號反射導致在傳輸線接收端讀出的電壓出現振蕩,或者表現出過長的響應,類似于不同電平之間的階梯。當反射發生時,傳輸線上負載器件輸入端的電壓和電流可能表現出過沖或下沖,具體取決于反射信號相對于輸入信號的極性。

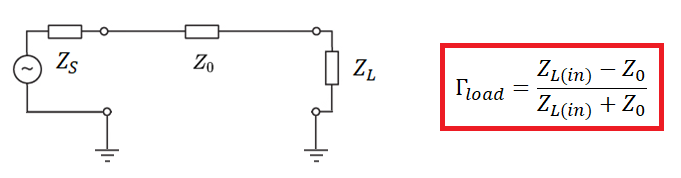

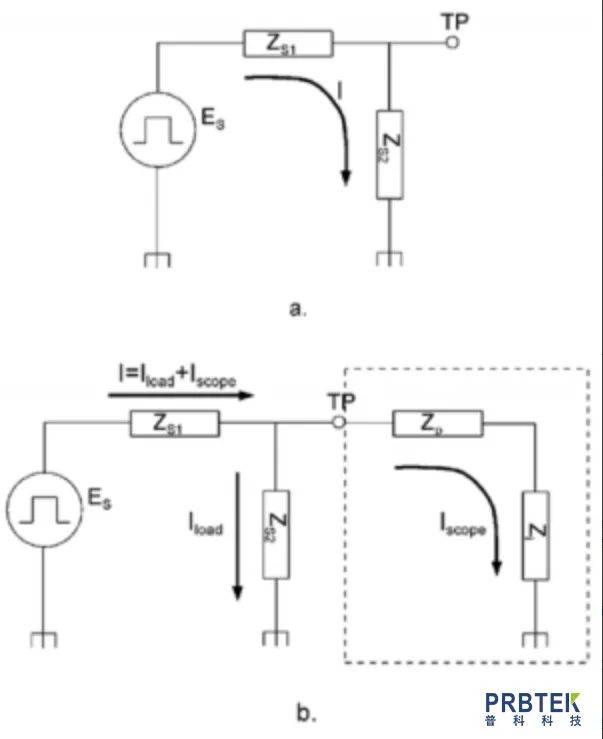

定義反射信號強度的主要方程式是反射系數方程式。對于到達負載輸入阻抗的行進信號,在負載輸入端的反射系數為:

對于這種典型的傳輸線配置,其反射系數在器件的負載端定義。對于到達傳輸線源端的波,也定義了一個類似的方程式。

從這個方程可以看出,如果負載的輸入阻抗與線路阻抗失配,在負載處就會發生反射。同樣的道理也適用于在源端觀察到的輸入阻抗。在每次反射后,由于線路兩端的連續反射,會出現相位偏移和信號電平降低。

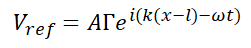

從線路負載端反射的波的方程式

在上述方程中,系數 A 是線路上信號的初始振幅。

這兩個方程的有趣之處在于,只要知道上述方程中的系數,它們就能完全描述阻抗失配的信號反射行為。傳輸線的行為仿真非常麻煩,要么需要使用 3D 電磁場求解器,要么需要等效的集總電路模型。在實踐中,可以簡單地繪制出輸入波及其相位偏移的反射圖,就可以獲得在時域中的負載輸入端測量的波形。基本上,一些 SPICE 模型就是通過這種方法來計算在負載輸入端測量的波形。

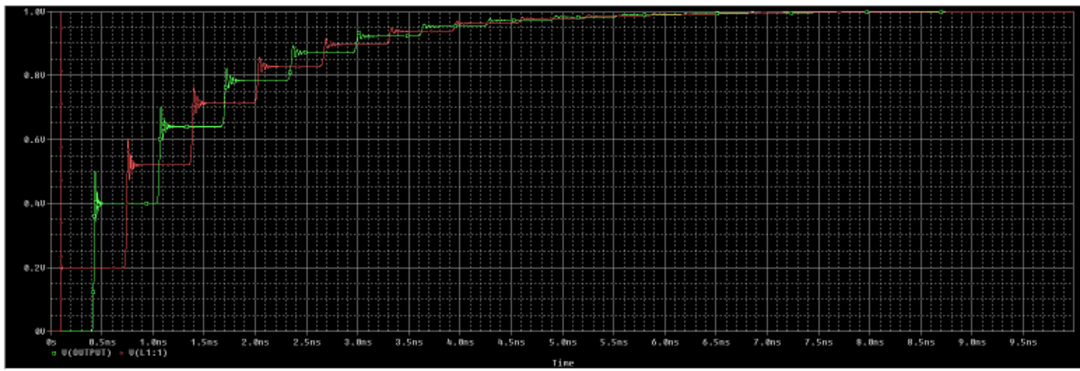

對于高負載阻抗,在負載處觀察到的輸入信號與反射信號相疊加,將產生一個波形,形狀如下圖所示:

由于高阻抗負載的信號反射而產生的明顯震蕩

為什么會出現明顯的過阻尼響應?

如果在網上搜索關于信號反射和阻抗失配的資料,絕大多數都是考慮 50 歐姆傳輸線連接到高阻抗負載的情況,特別是 CMOS 邏輯電路。由于反射系數的原因,反射的信號不會反轉。相反,功率只有在線路上來回反射之后才到達負載。然后,我們看到在傳輸線和負載之間的界面上出現了上述緩慢上升的情況。

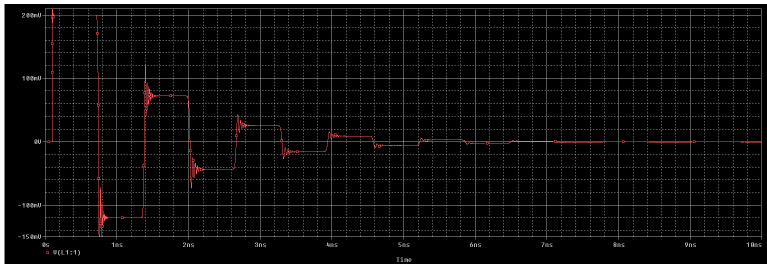

低阻抗負載的信號反射和阻抗失配

在低阻抗下,輸入波最初會反轉,因為反射系數小于零。這就產生了明顯的下沖。然后,反射波將繼續在線路上來回流通,在兩端反射和反轉,產生如下所示的波形。這看起來很像欠阻尼振蕩,但它們不完全是一回事。無損失配不會出現這種行為,這種情況下不會有任何阻尼機制。

由于低阻抗負載的信號反射而產生的明顯震蕩

與傳輸線一起使用的現代 IC 通常在驅動端(也可能在接收端)使用片內端接 (ODT)。對于線路驅動器或收發器等原件,線路的源端可能實現 50 歐姆的阻抗。負載器件可能沒有使用片內端接,這意味著需要使用一個并聯電阻、上拉電阻或 Thevenin 端接。

應用這些終端方案的目的是將信號設置在所需的電平,同時將負載的輸入阻抗設置為等于線路的特性阻抗。在線路的負載端應用外部端接,或在低阻抗驅動器的源端應用串聯端接之前,請先查閱產品手冊,看看該器件是否使用了片內端接。

Cadence Allegro PSpice Simulator 是業界一流的用于電路設計和仿真的PCB 設計和分析軟件之一。使用該軟件可以模擬到達傳輸線負載端的波形,以便在設計端接網絡時評估任何信號反射和阻抗失配。

-

電磁

+關注

關注

15文章

1133瀏覽量

51796 -

信號

+關注

關注

11文章

2790瀏覽量

76732

發布評論請先 登錄

相關推薦

高頻信號中的阻抗特性 三相電系統中的阻抗分析

技術資訊 I 如何使用 Allegro X PCB Editor 優化RF布線和阻抗

技術資訊 I 信號反射和阻抗失配的聯系

技術資訊 I 信號反射和阻抗失配的聯系

評論