在去年 12 月的國際電子器件大會 (IEDM) 上,有一節關于背面電源分配網絡(Backside Power Delivery Networks)的簡短課程。主講人是IMEC(微電子研究中心)的 Gaspard Hiblot,標題為《Process Architectures Changes to Improve Power Delivery(通過改變流程架構來改善電源分配)》;IMEC的高層人員Geert Hellings 和 Julien Ryckaert 也參與了內容創作。該演講的幻燈片多達 80 頁,因此本文不做贅述,只介紹其中的一些重點。

設計技術協同優化(DTCO)

現代工藝設計與設計將要使用的硅結構的某些方面密切相關。這與十年前的情況截然不同,當時制程技術開發團隊基本上會交給設計團隊一套 SPICE 模型和 layout 設計規則。而我們采用的新方法稱為“設計技術協同優化”,簡稱為 DTCO(Design Technology Co-Optimization)。

這個詞首次出現在 2016 年的 CDNLive (即Cadence用戶大會的舊稱,現稱為CadenceLIVE)Europe 會議上,當時 Luca Matti 展示了他在 IMEC 的工作——即將到來的 7nm 和 5nm 制程節點。在 DTCO 的早期發展階段,重點在于對半導體制程進行一些調整,如有源柵極觸點,旨在減少標準單元的軌道數量。

如今,簡單的維度縮放(即“摩爾定律”)已成為明日黃花,需要采用 DTCO 方法來保持縮放規律。其中一個巨大的挑戰是過孔的電阻。一直以來,我們使用銅材料來制造過孔,因為銅的電阻很低。但銅需要一個擴散阻擋層,如氮化鉭 (TaN),這會造成兩個問題——首先,阻擋層會占據空間,因此減少了過孔中銅的橫截面積;其次,阻擋層位于過孔底部,電流必須流過阻擋層。而阻擋層金屬的電阻高于銅,因此會增加過孔電阻。

銅線也有類似的問題,由于銅中的晶粒大小和銅線占據側壁的空間百分比增加,在 100nm 線寬以下,銅的電阻率開始增加。經常有人提議用釕來解決這個問題,因為它不需要阻擋層,在尺寸極小時電阻率也很低。但據我所知,并沒有人用釕代替銅。在最低的過孔中,甚至是 M0 互連中,有些人會使用鈷。

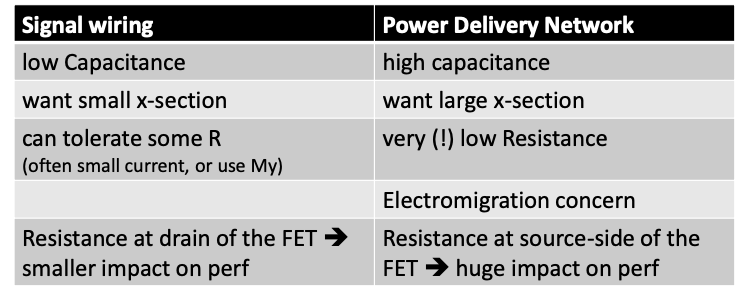

這些與互連有關的問題會影響到信號、時鐘和功耗。不過,信號布線和電源分配網絡 (PDN) 所面臨的權衡取舍是不同的。電源需要低電阻,與電容關系不大(因為電壓不變)。與普通信號不同,電源分配網絡要傳輸大電流,這讓電遷移成為了一個難題。為此,通常會采用更復雜的制程工藝,來區分電源和信號布線。

背面配電

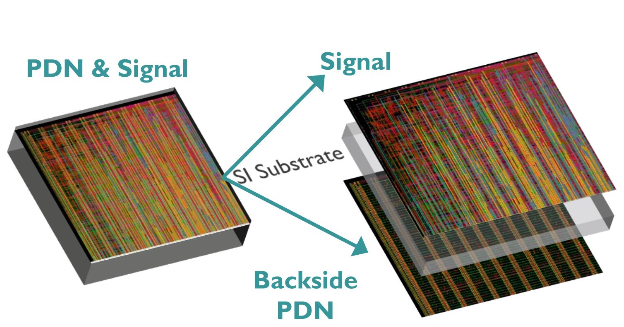

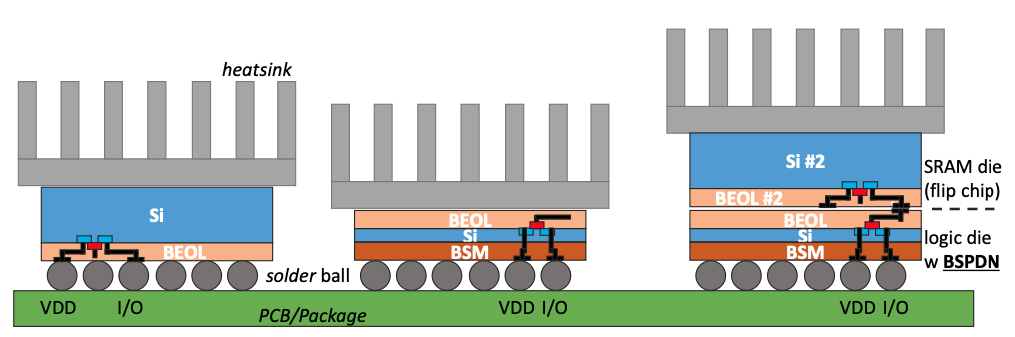

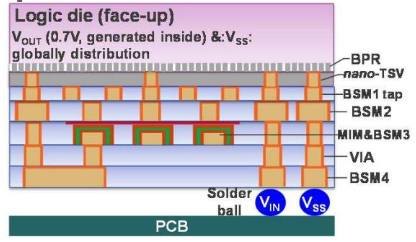

最終的區別在于將 PDN 與信號完全分開,在背面創建 PDN。PDN 位于減薄晶圓的背面,通過硅過孔 (TSV) 連接到晶體管和正面互連。

深入了解背面電源分配網絡 (Backside power delivery networks,即 BS-PDN)——

獨特優勢

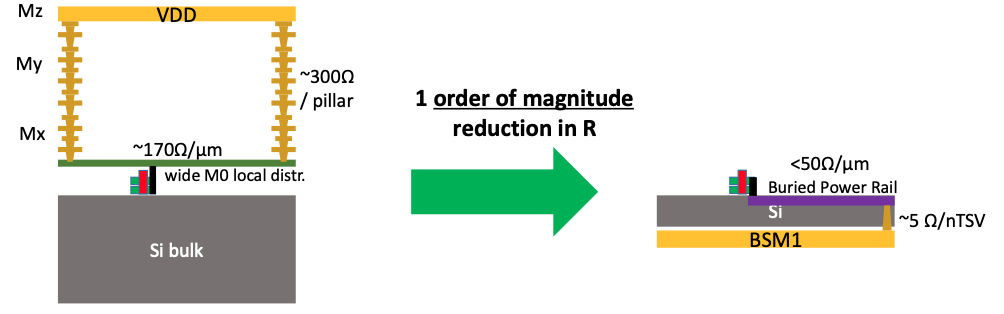

將片上壓降減少了一個數量級

如下圖所示,約 300Ω 的過孔柱減少到僅為 5Ω 的 TSV,這也大大減少了片上壓降。

擴展了芯片面積

這在很大程度上取決于制程工藝的不同方面(如 TSV 周圍禁布區的尺寸),也取決于 EDA 工具。

如Cadence Innovus 一類工具中的布線器應該可以更輕松地進行信號布線,PDN 不會在互連堆棧中造成阻礙。但具體的獲益有多大,還需要進行實驗。

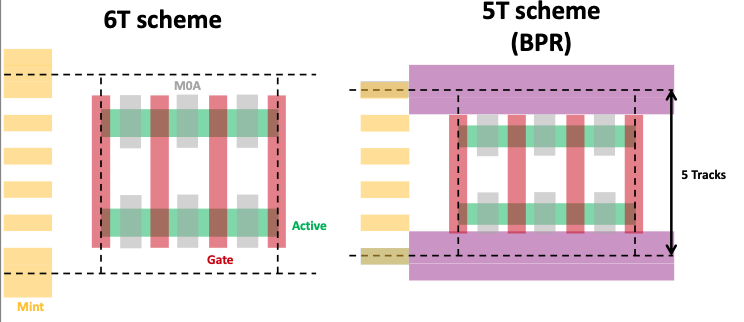

如果使用埋入式電源軌 (BPR),可以減少標準單元中的軌道數量,因此可以將芯片面積擴展大約 15-20%。

降低 BEOL 中精細金屬的復雜性

銅經常采用雙鑲嵌工藝,很難在同一層上混合寬金屬線(用于電源)和窄金屬線(用于信號)。

更易于實現晶圓對晶圓鍵合工藝,以便在邏輯上堆疊存儲器

倒裝 SRAM 裸片由邏輯裸片配電,因此可以有效地由相同的 BS-PDN 配電。

三種基本方法

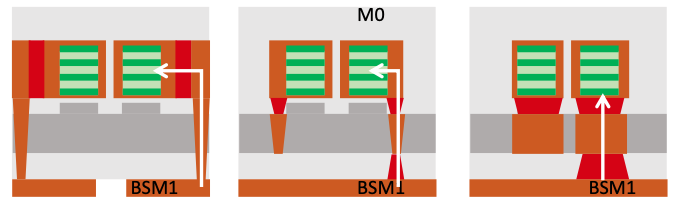

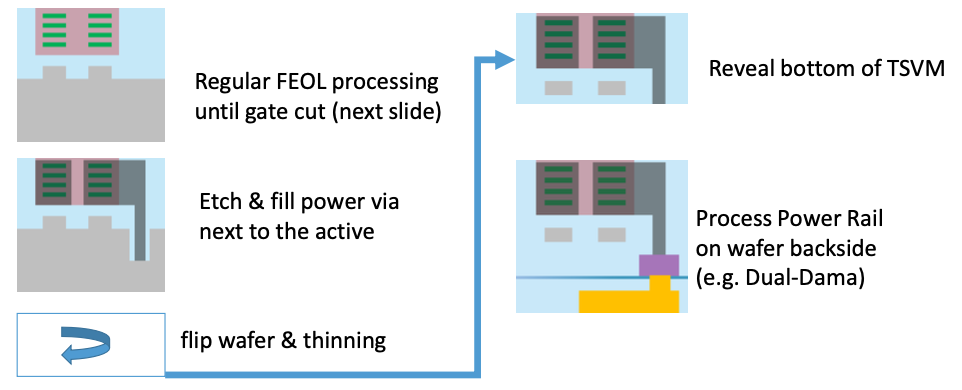

TSV-middle 電源位于有源旁邊,并在單元之間共享。BSM1(背面金屬 1)與有源對準。

埋入式電源軌 (BPR) 的電源埋在有源器件,VBPR 接入 BPR,BPR 充當 BSM1(因此,有一層“背面”配電網絡實際上移到了正面)。

背面接觸電源位于有源下方,過孔接入電源軌,BSM1 與柵極對準

這三種方法具有一些共同的挑戰——

01

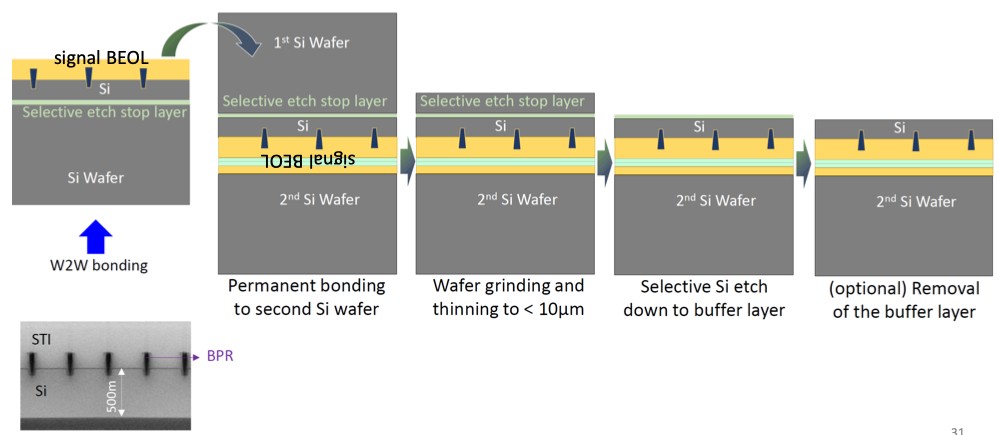

背面配電需要將硅晶圓減薄至小于 10um。

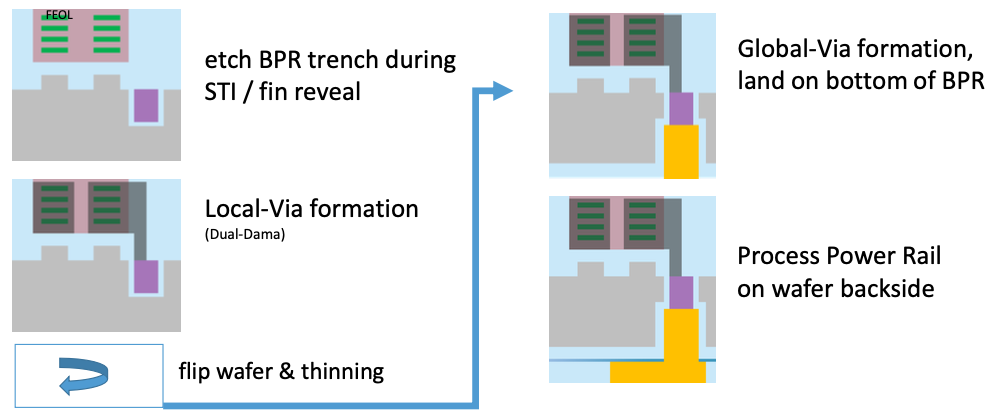

在真正的晶圓被削磨之前,需要將另一個晶圓粘合到真正的晶圓上(用于提供機械支撐和便于操作),如下圖所示:

02

將正面和背面對準。

nano-TSV (nTSV) 需要在約 10nm 內對準。

上圖是 TSV-middle 的高級流程;下圖是BPR(埋入式電源軌)的高級流程。

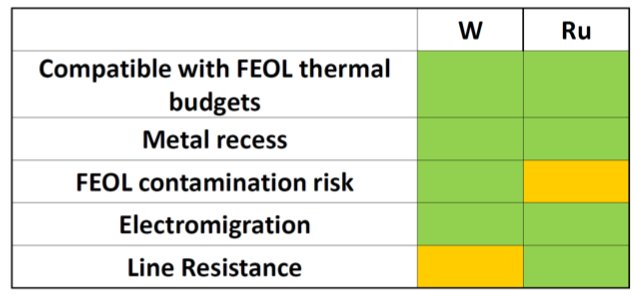

BPR 有兩種候選材料:鎢 (W) 和釕 (Ru)。鎢的污染風險較低,可達到 50Ω/um 的目標電阻;但是釕不需要使用阻擋層,過孔電阻較低。

在此本文不會過多討論背面接觸方法,因為它似乎離實用還有很長的路要走。Gaspard 對 BS-PDN 的總結如下:

超級緊湊(優點)

有許多未解決的挑戰(缺點)

背面和正面對準

Rseries

補充 FEOL 縮放

改善壓降(優點)

展望未來

演講的最后一部分對未來的技術發展進行了展望。

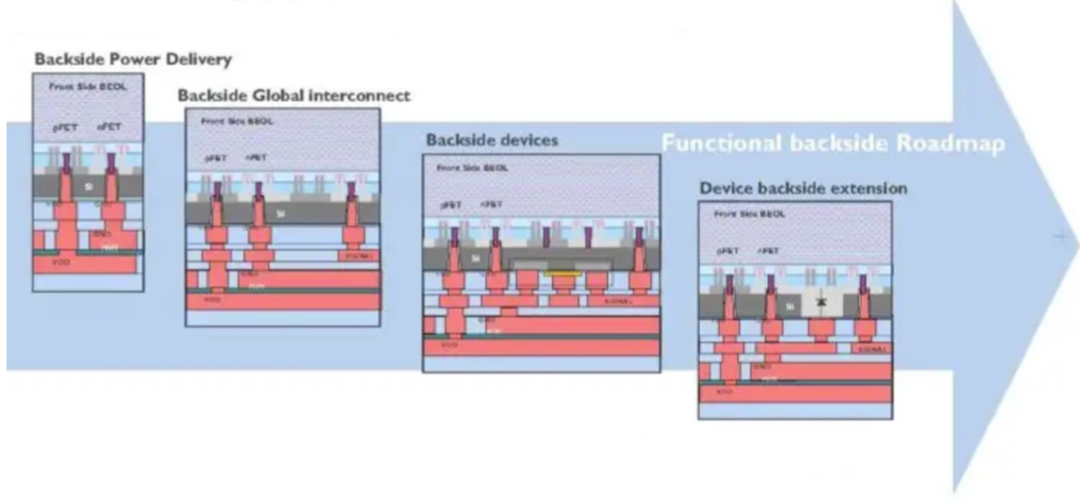

聽到“背面配電”,不由得讓人聯想是否可以再進一步,增強背面的功能,然后將一些系統功能也移到背面。首先是全局互聯(不需要在背面擺放器件)。但也有可能出現背面器件。

另一點是在背面創建金屬-絕緣體-金屬電容器 MIMCAP。鑒于可能涉及較大的功率密度 (1w/mm2),MIMCAP 有助于減少動態壓降。

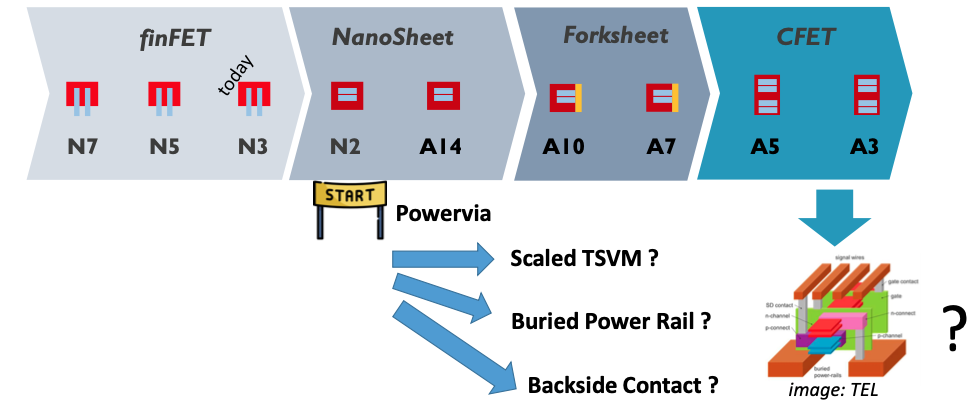

顯而易見的是,背面配電技術將繼續完善,一如下方邏輯器件路線圖。

-

器件

+關注

關注

4文章

310瀏覽量

27826 -

Layou

+關注

關注

0文章

3瀏覽量

6792

發布評論請先 登錄

相關推薦

碳化硅SiC在電子器件中的應用

功率電子器件控制電路的設計和功能

水井用安全電壓操作柱是否可行

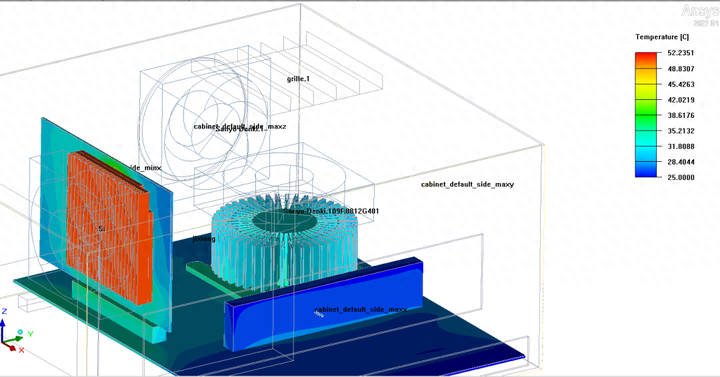

高功率電子器件的散熱方案

電壓驅動的電力電子器件的種類、工作原理及應用領域

電流驅動型電子器件的基本概念、工作原理及分類

電壓驅動型電力電子器件的優點

電壓驅動的電力電子器件有哪些

芯片電子器件焊點保護用什么膠水

行業資訊 I 國際電子器件大會:背面配電是否可行?

行業資訊 I 國際電子器件大會:背面配電是否可行?

評論