當現成的運算放大器(op amp)不能提供特定應用所需的信號擺幅范圍時,工程師面臨兩種選擇:使用高壓運算放大器或設計分立解決方案,不過這兩種選擇的成本可能都很高。

對許多應用來說,第三種選擇——自舉——可能是比較廉價的替代方案。除了動態性能要求極為苛刻的應用,自舉電源電路的設計是相當簡單的。

自舉簡介

常規運算放大器要求其輸入電壓在其電源軌范圍內。如果輸入信號可能超過電源軌,可以通過電阻衰減過大輸入,使這些輸入降至電源范圍以內的電平。這樣處理并不理想,因為它會對輸入阻抗、噪聲和漂移產生不利影響。同樣的電源軌也會限制放大器輸出,閉環增益的大小存在一個限值,以避免將輸出驅動到飽和狀態。

因此,如果要求處理輸入和/或輸出上的大信號偏離,則需要寬電源軌和能在這些電源軌上工作的放大器。ADI 的 24V 至 220V 精密運算放大器 ADHV4702-1 是適合這種情況的出色選擇,不過自舉低壓運算放大器也能滿足應用要求。是否使用自舉主要取決于動態要求和功耗限制。

自舉會創建一個自適應雙電源,其正負電壓不是以地為基準,而是以輸出信號的瞬時值為基準,有時稱之為飛軌(flying rail)配置。在這種配置中,電源隨著運算放大器的輸出電壓(VOUT)上下移動。因此,VOUT始終處于中間電源電壓,并且電源電壓能夠相對于地移動。使用自舉可以非常容易地實現這種自適應雙電源。

實際上,自舉必須符合一些準則,有些準則微不足道,但沒有一個準則是特別麻煩的。如下是最基本的準則:

輸出負載不得過大。

響應速度不得低于運算放大器的壓擺率。

必須能處理所需的電壓水平和相關的功耗。

飛軌概念是指正負電源軌連續調整,使其電壓始終關于輸出電壓對稱。這樣,輸出始終位于電源范圍內。

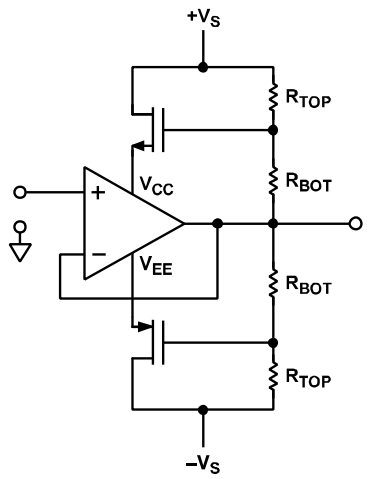

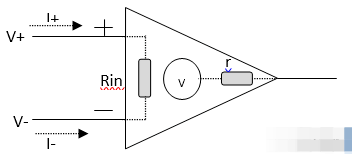

電路架構包括一對互補分立晶體管和一個阻性偏置網絡。NPN 發射極(或 N 溝道 MOSFET 的源極引腳)提供 VCC,PNP 發射極(或 P 溝道 MOSFET 的源極引腳)用作 VEE。晶體管被偏置,使得所需的電源電壓出現在放大器的+VS和–VS引腳上,這些電壓通過電阻分壓器從高壓電源獲得。圖 1 顯示了簡化高壓跟隨器原理圖。

圖 1. 簡化高壓跟隨器原理圖

理論上,自舉可以為任何運算放大器提供任意高的信號順從電壓。而在實際上,電源調整比例越大,動態性能越差,因為運算放大器的壓擺率限制了電源對動態信號的響應速度。放大器在最大額定電源電壓或接近該電壓下工作時,電源引腳為跟上動態信號而需要橫越的范圍最小。當運算放大器在接近其最高額定電源電壓下工作時,其他誤差源(如噪聲增益)也會降低。

不需要電源移動很遠(或非常快)的低頻和直流應用,是自舉的最佳候選應用。因此,高壓放大器能提供比動態特性相當的低壓放大器更好的動態性能,尤其是當二者均偏置為各自的最大工作電源電壓并且自舉到相同信號范圍時。自舉也會影響直流性能,因此在直流精度和高電壓兩方面均經過優化的運算放大器可提供自舉配置能實現的最佳直流和交流性能組合。

采用ADHV4702-1 的范圍擴展器設計

ADHV4702-1 是一款精密 220 V運算放大器。有了該器件,就不需要自舉傳統低壓運算放大器,220 V以下信號范圍的高壓設計得以簡化。如果應用需要更高電壓,那么可以應用自舉技術,輕松地將電路工作范圍增加兩倍以上。下面說明一個基于ADHV4702-1 的 500 V放大器設計示例。

電壓范圍

如上所述,擴展器電路的范圍在理論上是無限的,但存在如下一些實際限制:

電源電壓和電流額定值

電阻和場效應晶體管(FET)功耗

FET 擊穿電壓

直流偏置電平

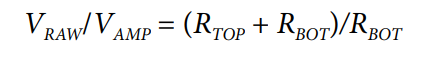

首先,考慮提供給放大器的電源電壓。任何在器件額定電源電壓范圍內的電壓都有效。然而,功耗是基于所選擇的工作電壓在放大器和 FET 之間分配。對于給定的原始電源電壓,運算放大器電源電壓越低,FET 中的漏源電壓(VDS)越高,功耗也相應地進行分配。應選擇適當的運算放大器電源電壓,從而以最有利于散熱的方式在器件之間分配功耗。其次,使用下式計算將原始電源電壓(VRAW)降低到放大器期望電源電壓(VAMP)所需的分壓比:

其中,RTOP為頂部電阻,RBOT為底部電阻。

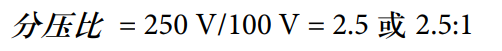

對于下例,考慮運算放大器標稱電源電壓為±100 V。對于需要±250 V 擺幅范圍的應用,通過下式計算分壓比:

然后,使用便于獲得的標準值電阻設計電阻分壓器,盡可能接近地實現此分壓比。請注意,由于涉及高電壓,電阻功耗可能比預期要高。

靜態功耗

對于所選電阻值,應選擇能夠應對相應靜態功耗的電阻尺寸。相反,如果電阻的物理尺寸受限,應選擇適當的電阻值來將散熱限制在額定范圍內。

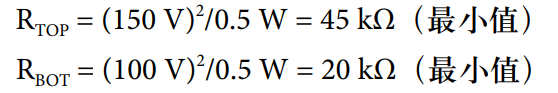

在該示例中,RTOP達到 150 V,RBOT達到 100 V。使用額定功率為 1/2瓦的 2512 電阻,設計必須將每個電阻器的功耗(V2/R)限制在 0.5 W 以下。計算每個電阻的最小值,如下所示:

將較高值電阻(45kΩ)作為功耗的限制因素,RBOT 值產生一個2.5:1 分壓器,同時觀測靜態功耗限值為

其功耗為(100 V)2/30 kΩ = 0.33 W。

瞬時功耗

考慮到電阻的瞬時電壓取決于放大器的輸出電壓以及電源電壓,本例中任何時刻每個分壓器上的電壓可能高達350 V(VCC = 250 V且 VOUT = –100 V)。正弦輸出波形在 VCC和 VEE分壓器中產生相同的平均功耗,但任何非零平均輸出都會導致一個分壓器的功耗高于另一個分壓器的功耗。對于滿量程直流輸出(或方波),瞬時功耗為最大功耗。

在此示例中,為將瞬時功耗保持在 0.5 W 以下,每個分壓器中兩個電阻之和(RSUM)不得小于以下值:

因此,電阻比為 1.5:1(對于 2.5:1 分壓器)時,各個電阻的最小值如下:

RTOP = 147 kΩ

RBOT = 98 kΩ

FET 選擇

承受最壞情況偏置條件所需的擊穿電壓主要決定 FET的選擇;當輸出飽和,使得一個 FET 處于最大 VDS,另一個 FET處于最小 VDS 時,便可明白這一點。在前面的示例中,最高絕對 VDS 約為 300 V,即總原始電源電壓(500 V)減去放大器的總電源電壓(200 V)。因此,FET 必須承受至少 300 V電壓而不被擊穿。

功耗必須針對最壞情況 VDS 和工作電流來計算,并且必須選擇指定在此功率水平下工作的 FET。

接下來考慮 FET 的柵極電容,因為它會與偏置電阻一起形成一個低通濾波器。擊穿電壓較高的 FET 往往具有較高的柵極電容,而且偏置電阻往往為 100 kΩ,因此不需要多少柵極電容就能顯著降低電路的速度。從制造商的數據手冊中獲得柵極電容值,計算 RTOP和 RBOT并聯組合所形成的極點頻率。

偏置網絡的頻率響應必須始終快于輸入和輸出信號,否則放大器的輸出可能超出其自身的電源范圍。暫時偏離到放大器電源軌之外會有損壞輸入的風險,而暫時飽和或壓擺受限會有造成輸出失真的風險。任何一種狀況都可能導致負反饋暫時丟失和不可預測的瞬態行為,甚至可能因為某些運算放大器架構中的相位反轉而閂鎖。

性能

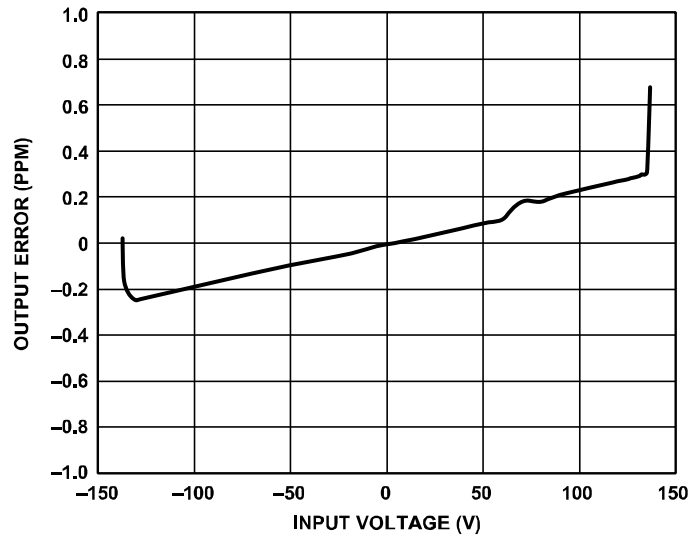

直流線性度

圖 2 顯示了增益誤差與輸入電壓的關系(直流線性度),增益為 20,電源為±140 V。

圖2. 增益誤差與輸入電壓的關系

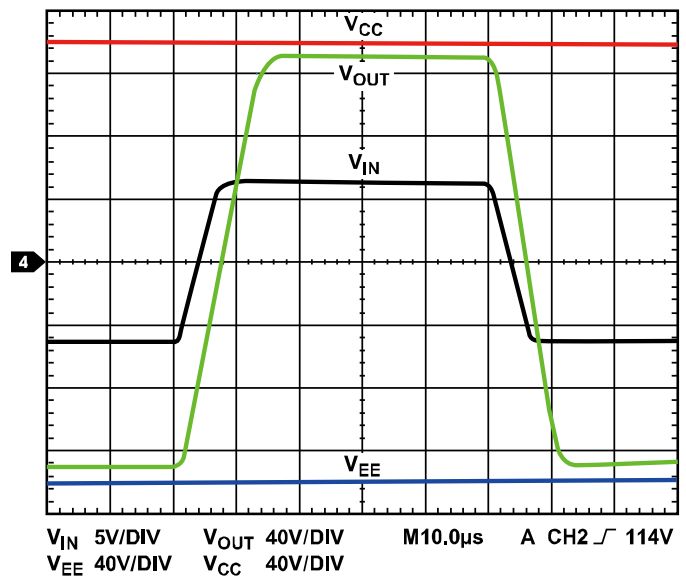

壓擺率

圖 3 顯示了壓擺率曲線,增益為 20,電源為±140 V,測量值為 20.22 V/μs。

圖 3. 壓擺率

實現更高速度的權衡

功耗

如前所述,工作電壓較高時,FET 的擊穿電壓(和相關的柵極電容)以及電阻值也必須較高。較高的電阻和電容值都會造成帶寬降低,唯一可用的調整因素是電阻值。降低電阻值會提高帶寬,但代價是功耗增加。

空間

低阻值、高功率的電阻尺寸較大,需占用較多電路板空間。以電容的形式在RBOT上增加一些引線補償可以改善電路的頻率響應。此電容與 RBOT和 RTOP電阻形成一個零點,抵消 FET柵極電容所形成的極點。極點和零點相消,因此可以選擇更高阻值的電阻,從而降低直流功耗。

結論

在需要較高電壓但使用典型高壓運算放大器不經濟的應用中,常常會讓常規運算放大器自舉。自舉有其優點和缺點。還有一個選擇,ADHV4702-1 提供一種高達 220 V的精密高性能解決方案,無需自舉。但是,當信號范圍要求超過 220 V時,該器件可以自舉以處理超過標稱信號范圍兩倍以上的電壓,同時提供比自舉低壓放大器更高的性能。

原文轉自亞德諾半導體

-

放大器

+關注

關注

143文章

13583瀏覽量

213368 -

運算放大器

+關注

關注

215文章

4929瀏覽量

172839

發布評論請先 登錄

相關推薦

線性運算放大器和非線性運算放大器的區別

運算放大器和普通放大器的區別

運算放大器的基本原理 運算放大器的應用實例

MCU中運算放大器的應用與比較

運算放大器如何放大信號

零漂移運算放大器和傳統運算放大器的區別

運算放大器和儀表放大器的區別

運算放大器的工作原理和基本電路 使用運算放大器的電路設計

運算放大器的工作原理 運算放大器的放大倍數怎么算

公式+案例 搞定同相運算放大器

【世說芯品】通過自舉擴展運算放大器工作范圍

【世說芯品】通過自舉擴展運算放大器工作范圍

評論