安路科技PH1A系列FPGA定位高性價比邏輯器件,針對高帶寬應用場景,能夠在保持低功耗的前提下,提供同類最佳的收發器和信號處理功能。

PH1A系列FPGA集成的第三代PCIe硬核控制器,帶寬最高可達8Gbit/s、可通過TD軟件的IP GEN配置。該核架構廣泛應用于通信設備、網絡接口卡、存儲系統等領域,具有高性能、低成本等特點。

PCIe SGDMA演示方案

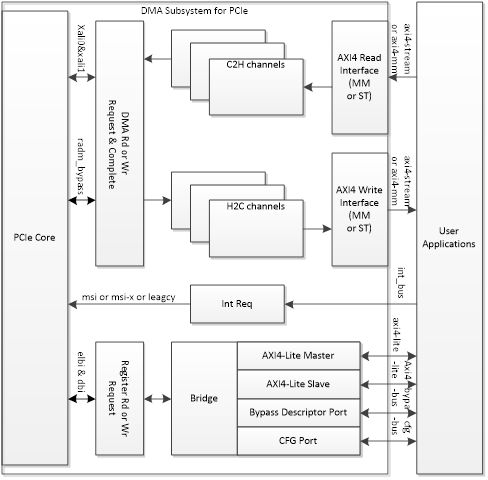

安路科技提供基于PCIe 硬核控制器開發的SGDMA IP。SGDMA可作為一個PCIe2AXI4系列接口的橋或者一個高性能DMA使用。

SGDMA支持屬性

64bit和128bit(PH1A90、PH1A180)數據位寬

32bit或64bit源地址、目的地址和描述符地址

目前支持單通道C2H以及單通道H2C

后續版本將支持N通道C2H以及N通道H2C

可選的單通道AXI4-Stream接口或AXI4-MM(memory mapped)接口

支持AXI4-Lite Master讀寫用戶和DMA寄存器

支持AXI4-Lite Slave讀DMA狀態寄存器

支持Scatter Gather描述符列表和環形描述符列表,列表大小無限制

MSI-X中斷 (后續支持)

Bypass descriptor 通道 (后續支持)

圖1.DMA框圖

SGDMA工作流程

SGDMA工作分為兩個流程,H2C(Host to Card)和C2H(Card to Host)。

DMA C2H 方向傳輸摘要:

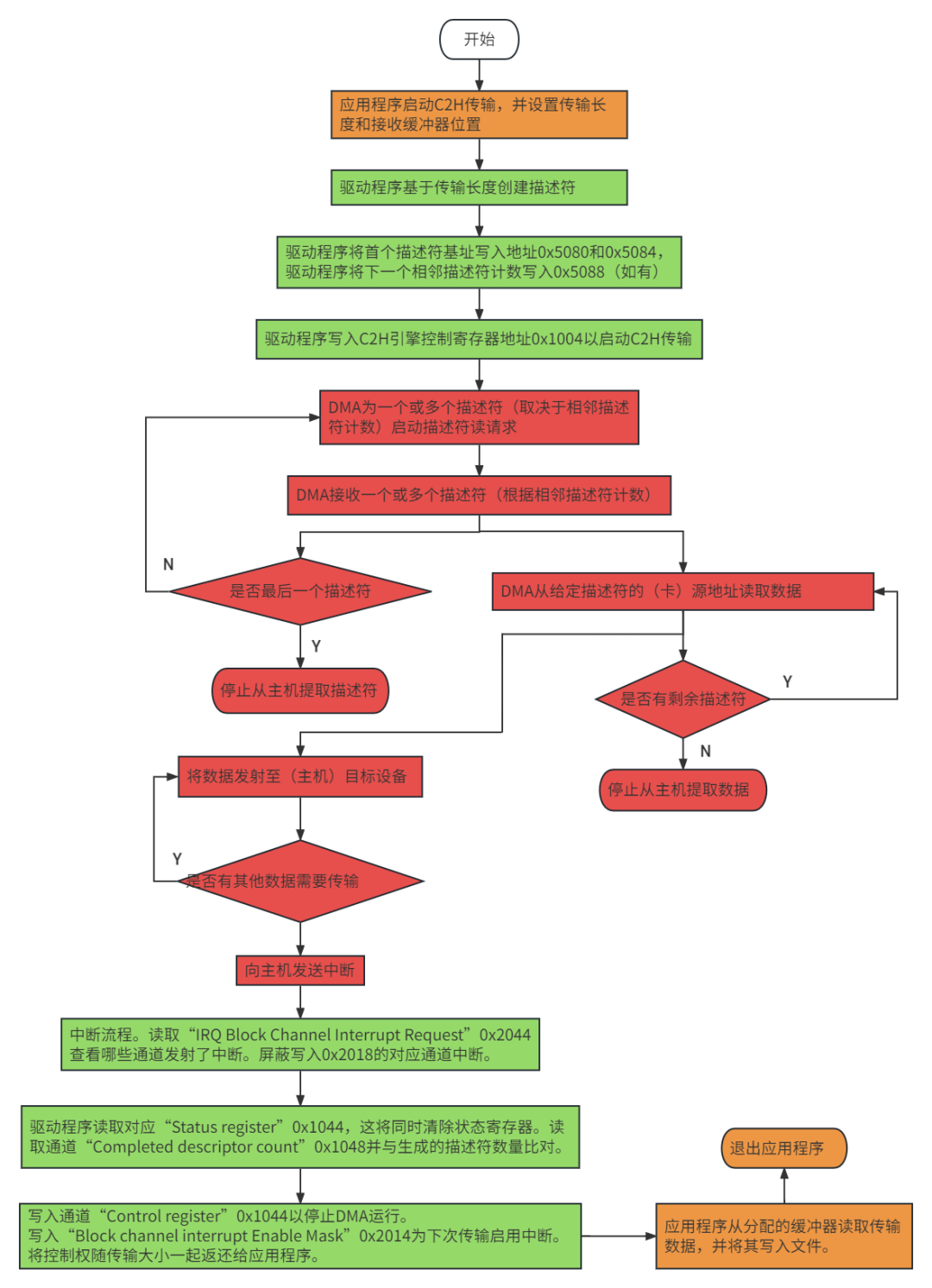

圖2.C2H傳輸框圖

首先,應用程序啟動C2H傳輸,并設置傳輸長度和用于存儲數據的緩沖器位置。然后,驅動程序會基于傳輸長度創建描述符,并將信息寫入寄存器控制傳輸啟動。DMA開始啟動描述符提取請求,之后DMA接收到描述符,判斷是否為最后一個描述符,如果是則停止,否則繼續發送描述符提取請求。DMA會根據接收的描述符向(板卡)源地址發送讀請求,讀請求會持續到沒有剩余描述符,并從板卡的AXI4(MM或者Stream)接口上接收數據,向主機發送數據,數據發送完畢以后向主機發送中斷。

驅動程序將執行中斷流程,并讀取完成描述符計數寄存器,與生成的描述符數量對比。隨后將控制權隨傳輸大小一起返還給應用程序。應用程序從分配的緩沖器讀取傳輸數據,并將其寫入文件。文件寫入完成后,退出應用程序。

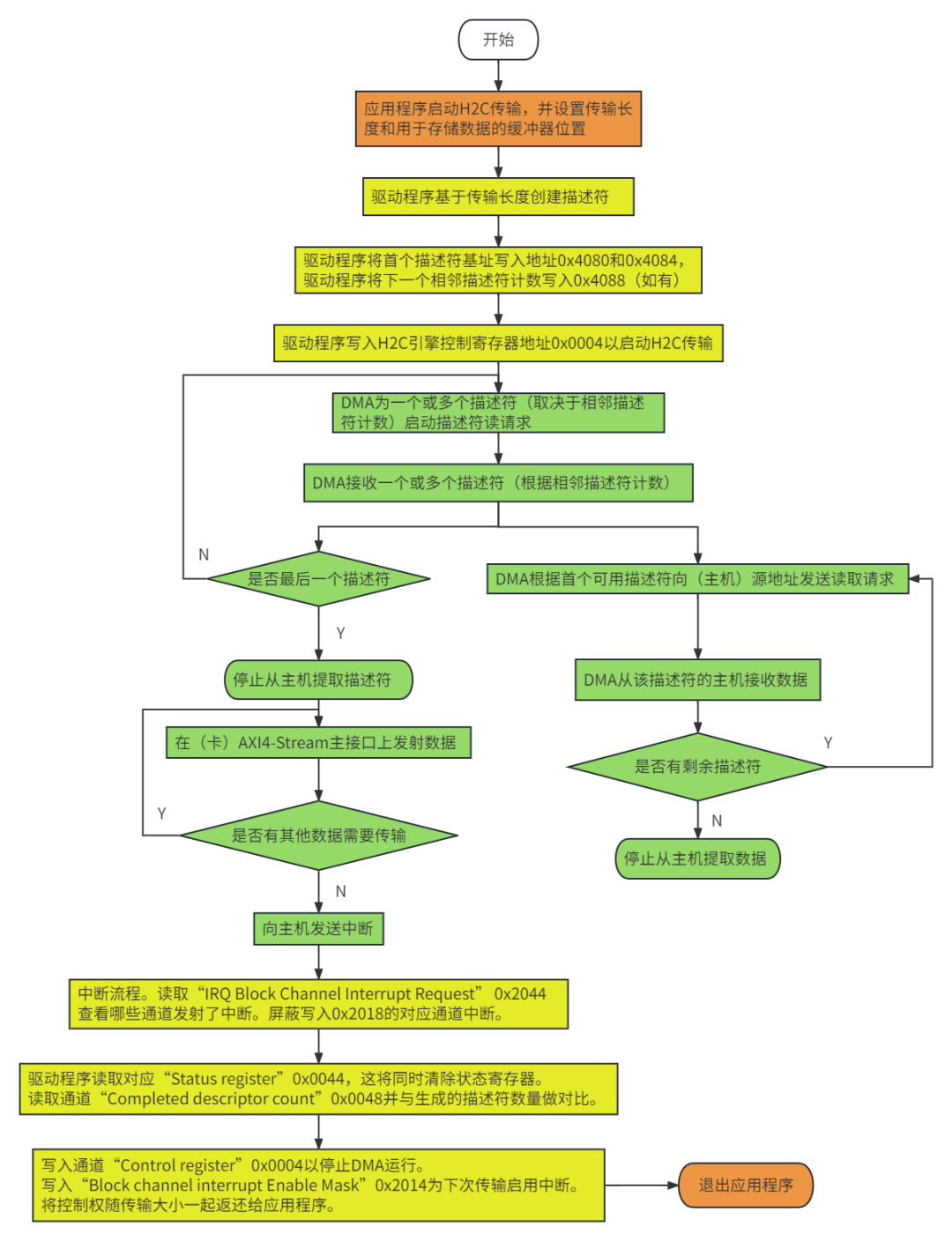

H2C的流程與C2H的類似,主要的不同點為C2H將板卡的數據發送給主機,H2C接收主機的數據。

圖3.H2C傳輸框圖

上海安路科技于2020年12月底正式成為PCI-SIG協會新會員。加入PCI-SIG協會后,安路科技將獲得更為廣泛的服務、了解最新的PCI技術動態,同時能參與PCI技術法規研討會、參與規范修訂和補充建議、PCI技術支持、獲得Vendor ID分配等系列服務與支持,這些都將助力安路研發技術和技術創新的穩步提升與發展。

原文轉自安路科技官微

-

FPGA

+關注

關注

1629文章

21734瀏覽量

603098 -

數據

+關注

關注

8文章

7010瀏覽量

88972

發布評論請先 登錄

相關推薦

4.0mm雙芯鎧裝野戰光纜:惡劣環境下的數據傳輸守護者

PCIe數據傳輸協議詳解

LORA模塊的數據傳輸速率

網絡數據傳輸速率的單位是什么

邊緣計算網關:開啟高速數據傳輸的新篇章

高速數據傳輸線纜組件 惡劣環境中的可靠選擇

智慧交通物聯網應用,5G路由器賦能高速道路監控數據傳輸

8芯M16插頭數據傳輸的準確性

【世說芯品】基于安路PCIe SGDMA 高速數據傳輸方案

【世說芯品】基于安路PCIe SGDMA 高速數據傳輸方案

評論