來源:焊接學報

摘 要

Cu-Cu 低溫鍵合技術是先進封裝的核心技術,相較于目前主流應用的 Sn 基軟釬焊工藝,其互連節距更窄、導 電導熱能力更強、可靠性更優. 文中對應用于先進封裝領域的 Cu-Cu 低溫鍵合技術進行了綜述,首先從工藝流程、 連接機理、性能表征等方面較系統地總結了熱壓工藝、混合鍵合工藝實現 Cu-Cu 低溫鍵合的研究進展與存在問題, 進一步地闡述了新型納米材料燒結工藝在實現低溫連接、降低工藝要求方面的優越性,概述了納米線、納米多孔骨 架、納米顆粒初步實現可圖形化的 Cu-Cu 低溫鍵合基本原理. 結果表明,基于納米材料燒結連接的基本原理,繼續 開發出寬工藝冗余、窄節距圖形化、優良互連性能的 Cu-Cu 低溫鍵合技術是未來先進封裝的重要發展方向之一.

0 序言

摩爾定律指出,集成電路上可容納的晶體管數 目及性能約每隔 18 ~ 24 個月便會提升一倍 . 隨 著大數據、5G、人工智能、移動互聯網的迅猛發展, 尤其是工藝節點到 7 nm 之后,物理效應、成本的限 制使得依靠光刻技術驅動的摩爾定律明顯放緩. 在“后摩爾時代”,不再一味地追求更小的光刻工藝 節點,而是依靠先進封裝互連技術的創新來滿足系 統微型化、多功能化的需求,這將是集成電路制造 行業發展的重要方向之一 .

為了滿足高性能芯片的應用需求,未來先進封 裝互連技術將不斷向高密度、高可靠的方向發展. 高密度即指焊點節距將不斷減小至 10 μm 以下,焊 點密度超過 10 000 個/mm2 ;高可靠主要指焊點在 電流密度不小于 106 A/cm2 、服役溫度不低于 100 ℃ 等工況下服役時具有良好的穩定性能,并伴隨應用 領域對電子器件要求越高則上述服役參數將不斷 提升. 目前,主流應用的先進封裝互連技術為 Sn 基 釬料軟釬焊工藝 ,主要包括回流焊和波峰焊工藝, 其具有連接溫度低 (250 ~ 300 ℃)、成本低等優勢. 對于回流焊工藝,回流過程中可發生自對中效應和 塌陷效應,降低了對設備對中精度和基板平整度 的要求. 然而,軟釬焊工藝也存在諸多局限性,比如 回流過程中易發生外溢效應,無法實現窄節距互 連;其接頭載流能力弱,易發生電遷移失效;界面 反應易生成空洞和脆性相,引起機械可靠性降低等. 這些瓶頸導致軟釬焊工藝無法滿足未來先進 封裝互連技術的發展要求. 近年來,Cu-Cu 鍵合 新方法發展迅速,無 Sn 元素的使用避免了上述問 題的出現. 具體而言,Cu-Cu 鍵合具有以下優勢:① Cu 在鍵合過程中全程保持固態,無軟釬焊的外 溢問題,可實現窄節距互連;② 具有優異的導電、 導熱性能,良好的抗電遷移能力和熱機械可靠性;③ Cu 是半導體制造中的常用金屬,工藝兼容性好 且材料成本低廉. 綜合上述因素,Cu-Cu 鍵合技術 可滿足高密度、高可靠互連,未來最有可能獲得大 規模應用. 然而,Cu-Cu 鍵合也面臨諸多新的挑戰, 如銅的熔點 (1 083 ℃) 高、自擴散速率低,難以實現 低溫鍵合. 已有研究表明,Cu-Cu 直接鍵合需要在 400 ℃ 的高溫下才能充分發生原子擴散,如此 高的溫度會導致降低對中精度、損傷器件性能、增 加設備要求等問題. 因此,如何實現 Cu-Cu 低溫 鍵合已成為學術界和產業界共同關注的焦點之一.

目前,實現 Cu-Cu 低溫鍵合的技術手段可分為 熱壓鍵合工藝、混合鍵合工藝、納米材料燒結工藝 三大類. 除了需滿足上述低溫需求外,新工藝還要 綜合考慮性能 (如強度、電阻)、可靠性、效率、成 本、工藝兼容性等因素. 文中將對這些工藝的方 法、原理進行系統歸納、總結,分析其實際應用時存 在的工藝難點,并展望了 Cu-Cu 低溫鍵合進一步研 究的方向,以期對未來技術發展提供參考.

1 熱壓鍵合工藝

熱壓鍵合工藝的基本原理與傳統擴散焊工藝 相同,即上下芯片的 Cu 凸點對中后直接接觸,其實 現原子擴散鍵合的主要影響參數是溫度、壓力、時 間. 由于電鍍后的 Cu 凸點表面粗糙并存在一定的 高度差,所以鍵合前需要對其表面進行平坦化處 理,如化學機械拋光 (chemical mechanical polishing, CMP),使得鍵合時 Cu 表面能夠充分接觸. 基于目 前研究文獻,通過熱壓鍵合工藝實現 Cu-Cu 低溫鍵 合的方法從機理上可分為兩類,即提高 Cu 原子擴 散速率和防止/減少待鍵合 Cu 表面的氧化.

1.1 提高 Cu 原子擴散速率

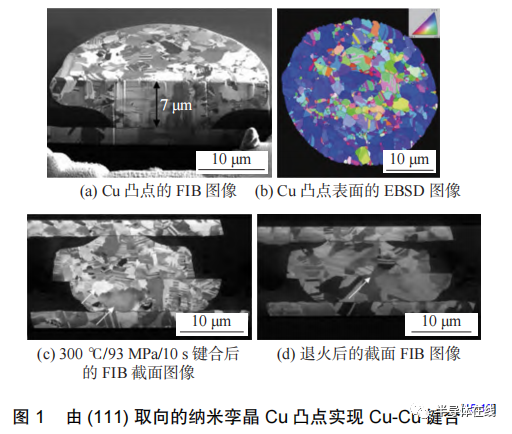

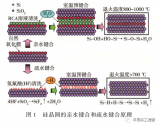

Juang ,Shie ,Ong,Liu 等人提出了 電鍍晶粒呈現高度 (111) 取向的 Cu 凸點用于 CuCu 熱壓鍵合的方法,如圖 1 所示. 已有研究表明, 在 150 ~ 300 ℃ 條件下,Cu 原子在 (111) 晶面上的 擴散速率比 (100)、(110) 晶面高 3 ~ 6 個數量級,晶 粒呈現高度 (111) 晶向的 Cu 凸點可以有效提高 Cu 原子擴散速率,降低鍵合溫度 . 利用晶粒定向 生長的方法可以在 300 ℃,90 MPa,10 s 的條件下 完成快速鍵合,但是鍵合強度和導電性能較差. 為 此研究人員進一步開發出了兩步鍵合工藝:首 先,電鍍后的 Cu 凸點進行 CMP 并使用檸檬酸清洗 去除表面氧化物,并在 300 ℃,93 MPa,10 s 的條件 下進行預鍵合;然后,在 300 ℃,47 MPa 的真空條 件下保溫 1 h 進行退火處理,退火后的剪切強度達 103 MPa,導電性能進一步改善. 圖 1d 顯示了退火 后晶粒會長大至貫穿鍵合界面,從而可提高界面的結合強度.

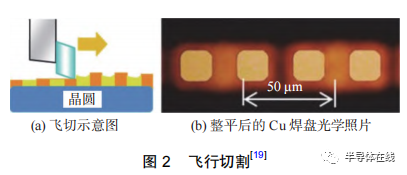

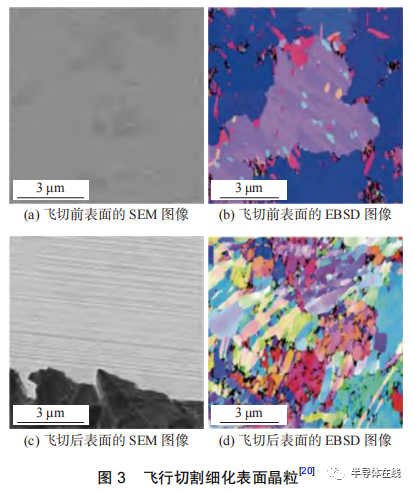

此外,Sakai等人采用金剛石刀頭飛行切割 的方法對 Cu 表面進行整平,如圖 2 所示. 發現切 割后的 Cu 表面會出現由細晶粒構成的薄層,細晶 層可提高晶界擴散通量,因而降低 Cu-Cu 鍵合的溫度. 最終鍵合在 200 ℃,30 min,300 MPa 的條件下 完成,且界面處原子相互擴散形成了新的晶粒. 研 究人員還比較了飛行切割與 CMP 處理后的 CuCu 鍵合強度,結果表明,200 ℃ 連接條件下,前者 的強度比后者高出近一倍. 此外,Al Farisi 等人將該方法用于密封,飛行切割后的 Cu 密封條可在 250 ℃ 的低溫下實現鍵合,從而減少密封過程中的 氣體解吸附,降低腔體內的氣壓. 從圖 3 可以看到, 飛行切割后的 Cu 表面晶粒發生了明顯細化.

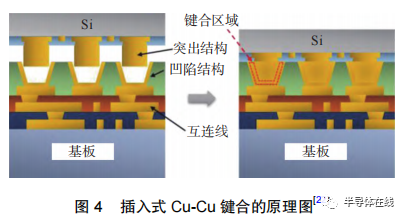

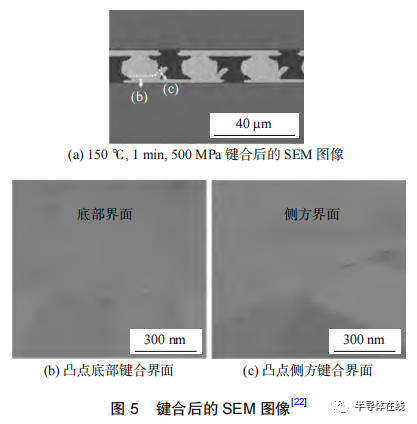

進一步地,為降低對 CMP/飛行切割整平工藝 的依賴,Yang,Chou等人提出了插入式 CuCu 鍵合工藝,其原理如圖 4 所示. 首先通過電鍍工 藝制作出異型結構的待鍵合 Cu 表面,一面直徑較 小的 Cu 為突出結構,另一面直徑較大的 Cu 為凹陷 結構,二者對中后形成插入式結構. 在加壓過程中突出結構的 Cu 和凹陷結構的 Cu 發生相對滑移和 應力集中,產生一定的熱效應,加速原子擴散. 這種 方法可以在 150 ℃ 的條件下完成鍵合,鍵合后的界 面如圖 5 所示. 可靠性測試表明,該方法經過 1 000 個 熱 循 環 測 試 (thermal cycling test, TCT, ?55 ~ 125 ℃) 和 96 h,130 ℃,85% 濕度的加速老化測試 (highly accelerated stress Test,HAST) 后,接頭電阻 無明顯變化. 這種方法無需 CMP 工藝,對待鍵合表 面的粗糙度有一定容忍度. 但是 ,為了使上下 Cu 結構發生較大塑性變形而充分接觸,需要施加 高達 500 MPa 以上的壓力.

1.2 防止/減少待鍵合表面氧化

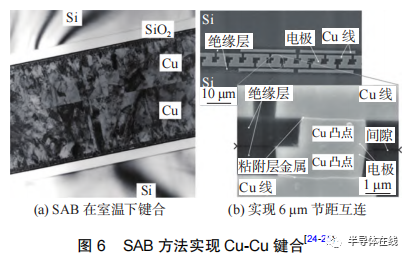

Cu 在高溫鍵合的情況下容易發生氧化,阻礙Cu 原子的擴散. Takagi,Suga,Shigetou等人 提出了表面活化鍵合 (Surface Activated Bonding, SAB) 的方法. 該方法在超高真空條件下 (10?8 torr) 采用等離子體轟擊待鍵合 Cu 表面,去除氧化物和 其他污染物,達到原子級的表面清潔度,并在室溫、 無壓力條件下進行預鍵合. 室溫條件鍵合可以保證 有更好的對中精度,報道中 SAB 可實現 6 μm 的窄 節距互連. 由圖 6 可以看到,預鍵合后仍存在明顯 界面,所以該方法往往需要 250 ~ 300 ℃ 的高溫退 火. SAB 表面處理和鍵合過程都需要在高真空條件 下完成,對設備要求非常高.

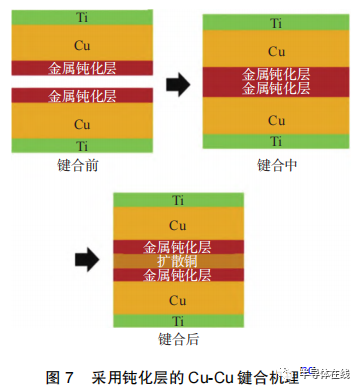

此外,研究人員提出了使用 Ti,Au,Ag, Pd等金屬在 Cu 表面制作鈍化層的方法,其鍵合原理如圖 7 所示. Cu 表面的金屬鈍化層及可有效 防止 Cu 被氧化,在鍵合過程中金屬鈍化層會向 Si 基底一側移動,而 Cu 原子會向鍵合界面遷移,最 終完成 Cu-Cu 鍵合.

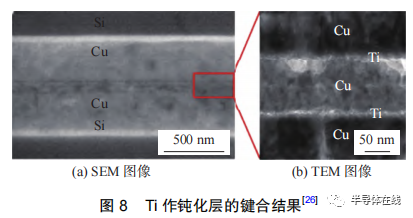

如圖 8 為 Ti 作鈍化層的鍵合結果,在 180 ℃, 1.91 MPa,30 ~ 50 min 的鍵合條件下,Ti 向 Si 基底 的方向移動了約 50 nm,鍵合界面處為 Cu. 鍵合后 經過 500 個 TCT(?55 ~ 125 ℃) 和 96 h,130 ℃,85% 濕度的 HAST 后,接頭電阻無明顯變化.

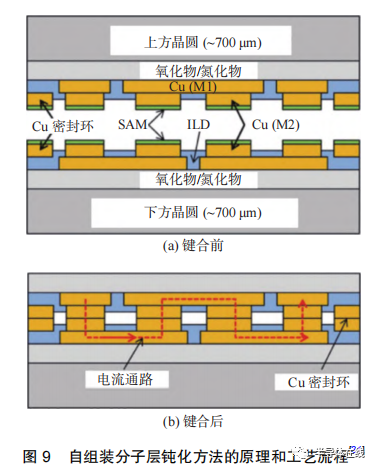

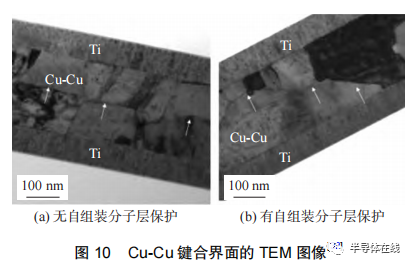

此外,Peng,Tan等人還提出了采用自組 裝 分 子 層 (self-assembled monolayer, SAM) 鈍 化 Cu 表面防止氧化的方法,如圖 9 所示. 在鍵合前, 晶圓放入烷烴硫醇溶液中進行浸泡從而在 Cu 表面 形成鈍化保護. 鍵合過程首先升溫至 250 ℃,該溫 度下有機物鈍化層會自行分解,隨后將分解產物抽 走后,Cu-Cu 鍵合過程在 300 ℃,1 h,2 500 mbar 真 空條件下進行. 圖 10 為無鈍化保護和有自組裝分 子層保護的鍵合界面對比,可以看到無鈍化保護的鍵合界面依然明顯,而鈍化保護的條件下界面基本消失.

2 混合鍵合工藝

窄節距互連尤其節距小于 10 μm 的情況下, Cu-Cu 鍵合后的片間間隙很小,難以填充下填料. 混合鍵合工藝可分別實現 Cu 和 Cu 之間的鍵合以 及 Cu 周圍介質和介質之間的鍵合,鍵合后的介質 可起到下填料的作用,減緩熱應力的同時保證更高 的鍵合強度、散熱能力和防止 Cu 凸點被腐蝕. 典 型的混合鍵合包括 Cu/SiO2和 Cu/粘結劑鍵合兩 種. Cu/SiO2混合鍵合的關鍵是得到平整度高、粗糙度小、親水性的表面,鍵合前需對 SiO2表面進行 激活;Cu/粘結劑混合鍵合基于熱壓鍵合機理,Cu/ 熱固性的粘結劑通過加熱加壓的方法鍵合在一起.

2.1 Cu/SiO2介質的混合鍵合

Cu/SiO2 鍵合后可以得到無縫隙的鍵合界面, 能有效提高熱/機械可靠性. 目前,關于 CuCu 鍵合的研究很多,如前述晶面定向生長、表面鈍 化等,然而其中相當一部分工藝無法直接移植到 Cu/SiO2混合鍵合. 這是因為 Cu/SiO2混合鍵合需 要綜合考慮 Cu-Cu 及 SiO2-SiO2鍵合 ,面臨工藝 兼容的挑戰. 目前,實現 Cu/SiO2混合鍵合的方 法包括表面激活、直接鍵合技術 (Direct Bonding Interconnect,DBI)、表面活化鍵合 (SAB) 等.

2.1.1 基于表面激活的混合鍵合

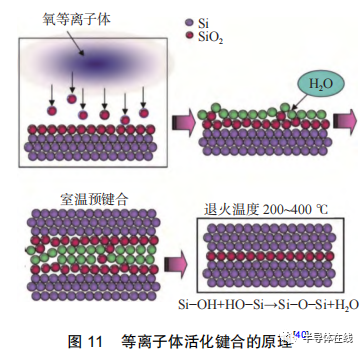

表面激活是指采用等離子體對晶圓表面進行 處理,清潔晶圓表面并使其活化,研究中采用的等 離子體包括 O2 ~ ,H2~ ,N2,NH3 ~ ,Ar等. 如 圖 11 所示,等離子體活化可以提高 SiO2~ 表面的羥 基密度,使得 SiO2 可在室溫下實現親水性預鍵合, 并在隨后 200 ~ 400 ℃ 的退火過程中脫水達成更可靠的共價鍵連接. 基于表面激活的混合鍵合的難 點之一是等離子體處理會對 Cu 表面產生不利影 響,例如使用 O2等離子體會氧化 Cu,即便是 Ar 等 離子體處理時腔體內含有的氧也會對 Cu 表面造成 氧化;使用 N2,NH3等處理會使得 Cu 表面生成 氮化物,影響 Cu-Cu 鍵合.

2.1.2 基于 DBI 的混合鍵合

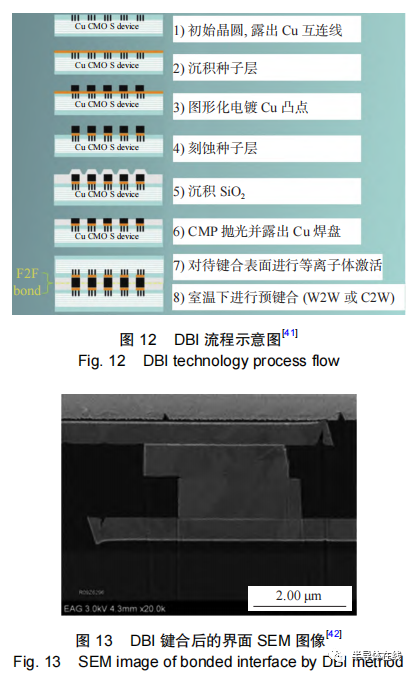

Co,Enquist等人提出了 DBI 的混合鍵合方法 ,其具體工藝流程如圖 12 所示. 首先通過濺 射、電鍍等半導體工藝在晶圓表面制作 Cu 凸點,隨 后沉積 SiO2介質層覆蓋 Cu 凸點及晶圓表面,接著使用標準 CMP 工藝露出晶圓表面的 Cu 焊盤并對 焊盤和 SiO2介質進行整平. 在 CMP 過程中,拋光 液作用于 Cu 表面使其高度略低于 SiO2表面. 在鍵 合前使用等離子體對 SiO2表面進行激活,使其 可在室溫、無壓條件下完成預鍵合.預鍵合后需 要在 300 ~ 350 ℃ 下進行退火,退火可以提高 SiO2- SiO2之間的鍵合強度,并使得 Cu 焊盤高溫膨脹相 互擠壓,完成 Cu-Cu 鍵合. 圖 13 為鍵合后的界面, Cu-Cu 及 SiO2-SiO2鍵合界面都沒有縫隙存在. DBI 由于在室溫下完成預鍵合,所以可以保證很高 的對中精度,報道稱其可實現 3 μm 的互連節距. DBI 具有良好的可靠性,鍵合后經過 2 000 個 TCT (?40 ~ 150 ℃) 和 2 000 h,275 ℃ 的高溫存儲后,接 頭電阻分別下降了 1.2% ~ 1.7% 和 1.2% ~ 1.4%, 滿足相關標準中電阻升高小于 10% 的要求.

2.1.3 基于 SAB 的混合鍵合

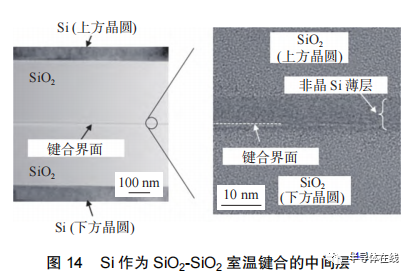

Utsumi等人提出了一種基于 Ar 等離子體 的 SAB 混合鍵合方法. 此前研究中發現,超高真空 下采用 Ar 等離子體轟擊可以實現 Cu-Cu,Si-Si 之 間的鍵合,但對 SiO2-SiO2之間的鍵合效果較差. 為 了提高 SiO2-SiO2之間的鍵合質量 ,研究人員在 SiO2表面濺射了約 12 nm 的 Si 作為中間層,隨后 經過 SAB 處理并在室溫下鍵合. TEM 觀察發現, 鍵合后的界面為厚度約 7 nm 的非晶 Si 薄層 (如 圖 14 所示),鍵合強度約為 25 MPa. 這種方法也會 在 Cu 表面引入 Si 層,在一定程度上降低 Cu 的導 電性.

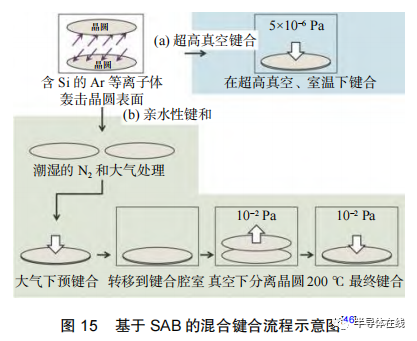

進一步地,He 等人提出了采用含 Si 的 Ar 等離子體處理待鍵合表面的工藝方法,如圖 15 所示. 含 Si 等離子體可提高 SiO2表面的 Si 點位, 促進 SiO2-SiO2鍵合. 表面處理后分兩條工藝路線 進行晶圓鍵合,一種是直接在 5 × 10^?6^ Pa 的高真空 下直接進行室溫鍵合,另一種為采用預鍵合-分離- 最終鍵合的多步路線進行親水性鍵合:(1) 將處理 后的晶圓置于真空度為 2 × 10^?2^ Pa 的腔室內,隨后 向腔室內充入潮濕的 N2至 3 kPa,接著沖入干燥氮 氣至大氣壓,晶圓取出后采用純水沖洗并甩干; (2) 在大氣 (濕度約為 40%)、常溫、無壓條件下對晶圓進行預鍵合,并在大氣下保存 10 min 以上;(3) 將 預鍵合后的晶圓轉移至鍵合腔室內,并在 10?2 Pa 的條件下分離預鍵合的晶圓;(4) 在 10?2 Pa 真空 度 ,200 ℃,2.5 MPa,30 min 的條件下進行最終 鍵合并在大氣壓下 200 ℃ 退火 2 h. 強度測試表 明,預鍵合—分離—最終鍵合的方法可實現 2.0 ~ 2.5 J/m^2^ 結合能的 SiO2-SiO2鍵合,優于高真空直接 鍵合的 0.5 J/m^2^ . 這是由于該方法可以在最終鍵合 前增加?OH 吸附及去除表面 H2O 分子,更有利于 提高鍵合強度、減少界面空洞. 此外,這種方法也可 以得到低含氧量的 Cu-Cu 鍵合界面.

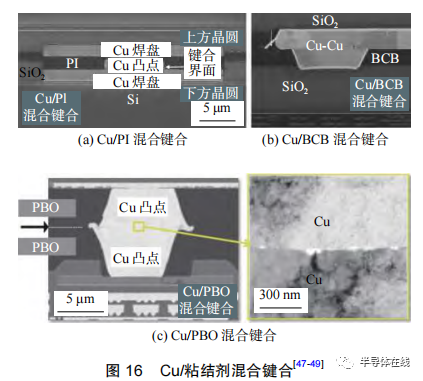

2.2 Cu/粘結劑介質的混合鍵合

Cu/粘結劑介質的混合鍵合與 Cu/SiO2混合 鍵合類似 ,只是使用粘結劑如 BCB, PBO, PI等替代了 SiO2介質 (圖 16),粘結劑具有更好 的柔性,可以一定程度上容忍介質表面的微塵顆粒物.

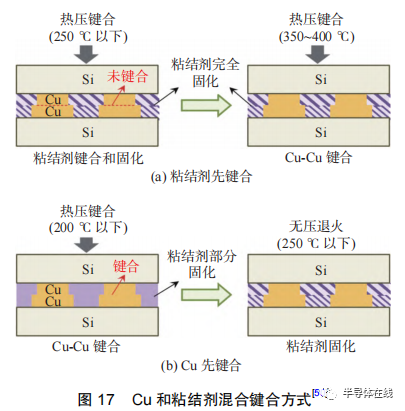

Cu/粘結劑混合鍵合主要基于熱壓的方法,實 現方式包括兩種:①粘結劑先鍵合,如圖 17a 所 示. 在較低的溫度下 (約 250 ℃,取決于粘結劑的種 類) 首先將粘結劑鍵合并固化,此時 Cu-Cu 尚未完 成鍵合,然后在更高的溫度 (350 ~ 400 ℃) 下進行 熱壓實現 Cu-Cu 鍵合,粘結劑在低溫下鍵合可以防 止更高的 Cu 鍵合溫度對未固化的粘結劑造成損 傷. 不過這種方法存在諸多不足,如需選擇耐高溫 的粘結劑材料、粘結劑需要較長的固化時間導致鍵 合效率降低等. ② Cu 先鍵合,如圖 17b 所示.

Cu 首先在低于粘結劑固化的溫度下短時鍵合 (如 ≤10 min),隨后在更高的溫度下對粘結劑進行固化 且進一步提高 Cu-Cu 鍵合的強度. 實現 Cu-Cu 低 溫鍵合的方法需要考慮到對粘結劑表面的影響,如 Ar 原子束和 Ar 等離子體處理雖然可以降低 CuCu 鍵合的溫度,但激發出來的金屬離子卻會污染 粘結劑表面,干擾粘結劑的鍵合. 為此,有研究人 員采用 Pt 催化后含 H 的甲酸對 Cu 和粘結劑表 面進行處理,可以在 200 ℃,5 min 條件下完成 Cu-Cu 鍵合,并且不會對粘結劑鍵合產生不利影響.

3 熱壓鍵合和混合鍵合的工藝難點

前述分別匯總了 Cu-Cu 熱壓鍵合、混合鍵合方 法的研究現狀. 目前大部分研究還僅僅停留在實驗 室階段,需要進一步深入對工藝和機理的探討. 與 此同時,當前這些方法也面臨著共性的工藝難點, 包括以下兩方面:

3.1 工藝要求非常苛刻

無論是熱壓鍵合還是混合鍵合方法對待鍵合表 面的質量如粗糙度、光潔度、晶圓整體翹曲程度有 很高要求. 由于制作完成的 Cu 表面為粗糙狀態且 有一定的高度差,需要經過昂貴、復雜的 CMP、飛行 切割等整平工藝對待鍵合表面進行平坦化,降低表 面粗糙度和高度差. 此外,晶圓本身還具有一定的 翹曲,尤其是面積大、厚度薄的晶圓,翹曲程度會更 加明顯,Cu-Cu 鍵合的“硬碰硬”接觸方式易在鍵 合良率方面出現問題. 在低溫互連方面,為了實現 300 ℃ 以下的低溫互連,增大界面接觸面積,往往需 要增加鍵合壓力至 100 MPa 以上,這樣大的壓力可 能會導致晶圓碎裂或介質層開裂、變形等問題,不能 滿足工藝要求. 此外,混合鍵合中 Cu-Cu鍵合和介 質-介質鍵合二者常常會相互干擾,需要兼顧兩方面 的鍵合要求,對材料、工藝都提出了很大挑戰.

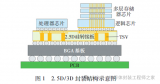

3.2 難以靈活適用于 2.5D 互連

Cu/介質混合鍵合技術近年來發展迅速,部分 混合鍵合技術已在實際制造中應用于 3D 互連的晶 圓鍵合 (Wafer to Wafer,W2W). 然而,混合鍵合 技術對待鍵合表面的微塵顆粒物很敏感. 即便如 Cu-粘結劑混合鍵合可以容忍一定的微塵顆粒物, 但如果顆粒物出現在 Cu 表面,仍會嚴重影響鍵合 質量. 在 2.5D 互連的芯片-晶圓鍵合 (Chip to Wafer, C2W) 場合中,晶圓需要切割成單個芯片再鍵合到 載板晶圓表面,切割過程中不可避免地會引入微顆 粒物等,混合鍵合技術難以適用. 此外,2.5D 互連 主要是為了實現芯片功能整合,需要貼裝的芯片種 類非常多樣化,往往來自不同晶圓制造廠商,下游 的封裝廠很難說服上游晶圓廠改變制程來適應混 合鍵合的工藝需求.

4 Cu納米材料燒結連接

近年來,基于 Cu 納米材料燒結連接實現 CuCu 鍵合逐漸獲得關注. 與熱壓鍵合和混合鍵合相 比,納米材料燒結對待鍵合表面的粗糙度、平整度 等有更高的適應性,能夠大幅降低工藝要求.

4.1 納米材料燒結連接的基本原理

納米材料相對于宏觀塊體材料,表面原子占比增多,具有更高的表面能 ,更易發生原子擴散,非 常有利于在低溫下進行燒結連接.

以金屬納米顆粒為例,其燒結過程可以用經典 粉末燒結理論進行描述. 根據粉末燒結理論,由粉 末材料構成的顆粒系統在燒結時傾向于降低其表 面的自由能,這是推進燒結進程的主要動力,燒結頸的長大是燒結過程進行的具體表現. 在燒結過程 中,首先分散/疏松的納米顆粒在壓力作用下相互接 觸,然后隨著溫度的升高發生表面擴散、晶界擴散、 晶內擴散,燒結頸逐漸長大,組織趨于致密化. 燒結后的組織為多孔結構,與塊體材料相比具有更小的模量,更容易發生塑性變形,對粗糙、不平整表面有 優異的“填補”效應 ,具有更寬的工藝窗口.

根據納米材料燒結前的形態進行劃分,研究中 的 Cu 納米材料主要包括三類:納米線、納米多孔骨 架和納米顆粒. 下面分別對這三方面的研究現狀進行簡要介紹.

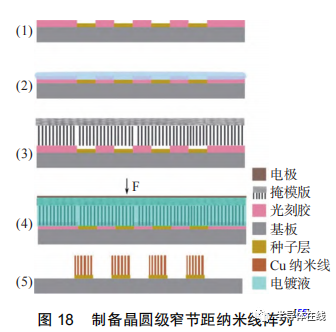

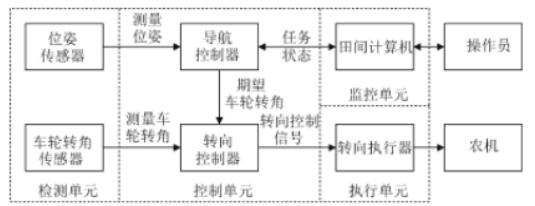

4.2 Cu 納米線燒結

Roustaie,Strahringer,Yu等人提出了 一種基于 Cu 納米線燒結的工藝,該工藝的優勢主 要體現在其 Cu 納米線陣列的圖形化方式與成熟半 導體工藝良好兼容,可實現高密度 Cu 納米線凸點 的制備. 具體工藝流程如圖 18 所示:①在對晶圓進 行厚膠光刻漏出 Cu 焊盤,Cu 焊盤作為納米線生長 的基底,光刻膠作為納米線定向生長的掩膜;②通 過氧等離子體轟擊去除 Cu 焊盤表面的有機物殘 留;③將帶有直孔陣列的特制掩模板壓覆在晶圓表 面,并與 Cu 焊盤接觸,整體浸沒到 Cu 電鍍液中;④隨后進行電鍍工藝,電鍍過程中 Cu 納米線以 Cu 焊盤為基底,沿著掩模版孔陣列的方向向上生 長;(5) 最后去除掩模版,獲得由 Cu 納米線構成的 凸點陣列.

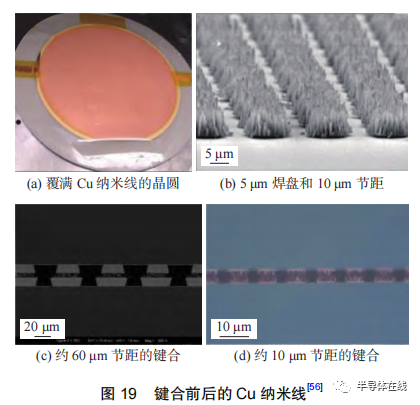

這種方法可以實現凸點陣列的晶圓級制備,如 圖 19a,b 所示. 所獲得的 Cu 納米線陣列可以在 230 ℃,60 MPa 的溫度、壓力條件下實現 57.4 MPa 的剪切強度,且經過 1 000 個熱循環測試 (?40 ~ 150 ℃) 和 4 000 h 的 HAST 測試 (85 ℃, 85% 濕 度) 后剪切強度無明顯下降.

**4.3 Cu 納米多孔骨架燒結 **

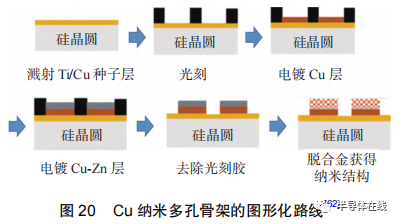

Shahane,Sosa,Mohan等人提出了 一種可圖形化的脫合金法制備 Cu 納米多孔骨架凸點,其具體工藝流程如圖 20 所示. 首先在晶圓 表面濺射一層 Ti/Cu 作為后續電鍍工藝的種子層, 隨后旋涂光刻膠并進行光刻得到所需的孔陣列圖案 ,接著在光刻膠孔內分別電鍍 4 ~ 8 μm 厚的 Cu 凸點和 5 ~ 10 μm 厚的 Cu-Zn 合金,光刻膠去除 后即可得到上方為 Cu-Zn 合金、下方為 Cu 的復合 凸點結構,最后使用 1% 質量分數的 HCl 在室溫下 腐蝕 4 h 使得 Cu-Zn 合金中的 Zn 被腐蝕并獲得 Cu 納米多孔骨架凸點.

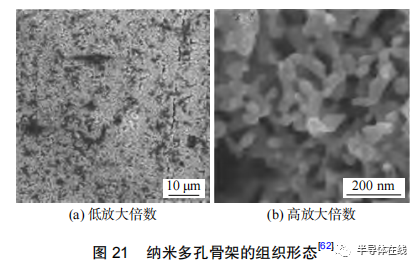

在 Cu 納米多孔骨架制備方面,研究人員主要 研究了電流密度、Cu-Zn 合金中 Zn 的含量、退火工 藝對 Cu 納米多孔骨架組織的影響,結果表明在電 流密度為 2.75 mA/cm^2^ 、Zn 含量為 85%、200 ℃/ 30 min/N2 退火的工藝條件下,可以獲得較理想的 納米多孔結構,如圖 21 所示,特征尺寸在 60 nm 以下,其中約有 10% 的 Zn 殘留.

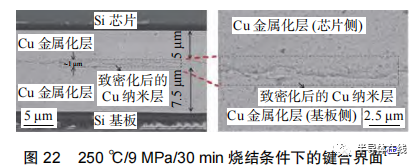

在 250 ℃,9 MPa,30 min,5% 甲酸氣氛的鍵合 條件下,剪切強度可達 47 MPa. 如圖 22 所示,鍵合 前約 3 ~ 4 μm 厚的多孔納米結構被壓縮到了 1 μm 以內,這表明該方法可以在一定程度上通過塑性變 形彌補基板翹曲以及 Cu 柱高度差帶來的不平整 度. 不過,該工藝制備獲得的 Cu 多孔結構中存在 一定的 Zn 殘余,活潑金屬對長期服役可靠性的影 響需要進一步研究.

4.4 Cu 納米顆粒燒結

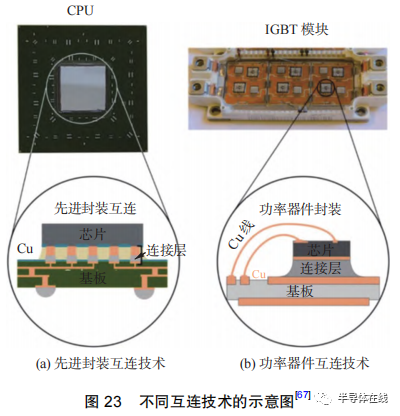

目前,Cu 納米顆粒用于燒結連接主要是通過 配置成銅納米焊膏并應用于功率器件封裝. 如 圖 23 所示,功率器件封裝的芯片與基板間一般只 有一個互連層,而先進封裝互連的焊點數量成千上 萬. Cu 納米焊膏應用于先進封裝互連的難點之一 是圖形化,即如何制作出大規模焊點陣列.

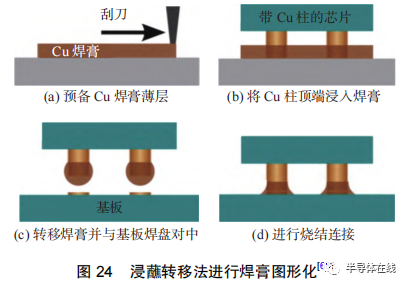

Del Carro,Zürcher等人提出了一種浸 蘸轉移的方法實現焊膏圖形化 ,其具體流程如 圖 24 所示. 首先將微納米顆粒混合的 Cu 焊膏通過刮刀刮平獲得約 20 μm厚度的薄層 ,將電鍍有 Cu 凸點的芯片在焊膏中浸蘸使得 Cu 凸點頂端黏附有 8 ~ 12 μm 厚度的 Cu 焊膏,接著將芯片與基板進行 對中并在甲酸氣氛下 160 ~ 200 ℃ 燒結鍵合.

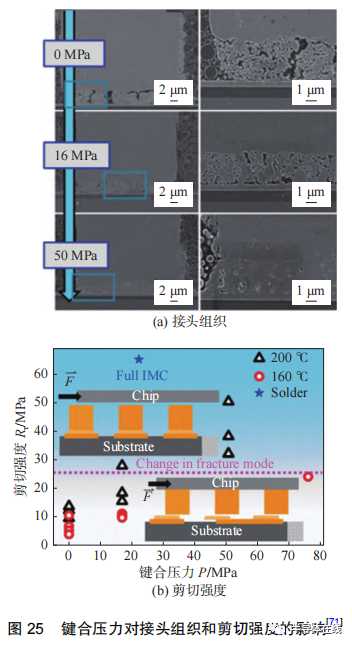

研究人員首先研究了 Cu 凸點的輪廓形態、浸 蘸轉移的速度、焊膏粘度等對圖形化的影響,結果 表明該方法具有良好的穩定性,可以適應一定的工 藝波動. 并重點分析了鍵合壓力對界面燒結組織 和性能的影響,結果如圖 25 所示. 從圖中可以看 到,鍵合壓力對燒結組織的孔隙率有明顯影響,無 壓燒結情況下燒結組織出現明顯的聚集性孔洞,可 靠性存在隱患,且剪切強度只有約 10 MPa;隨著壓 力增大到 50 MPa,界面組織趨于致密,剪切強度提 升至 40 MPa 左右. 該方法率先將 Cu 納米焊膏應 用到先進封裝互連領域,并表現出良好的適用性, 具有良好的應用前景,但相關可靠性測試數據還比較少,需要進一步研究. 此外,由于 Cu 納米焊膏具 有一定的流動性,易在壓力作用下發生擠出從而導 致相鄰焊點“橋接”,所以該方法在實現窄節距互連 上面臨一定局限性.

此外,Mimatsu 等人基于 Cu 納米顆粒粉末 提出了類似的轉移方法進行圖形化. 研究人員將通 過化學法合成的 Au 納米顆粒粉末鋪勻到裸硅片 上,再將帶金凸點的芯片與裸硅片壓到一起并加熱 到 100 ℃,使得 Au 納米顆粒與金凸點表面發生一 定程度的預燒結,最后將芯片與基板對中鍵合到一 起.這種方法最大的問題是納米顆粒粉末與凸點間 的結合很弱,部分凸點上沒有或只有很少的納米顆 粒附著.

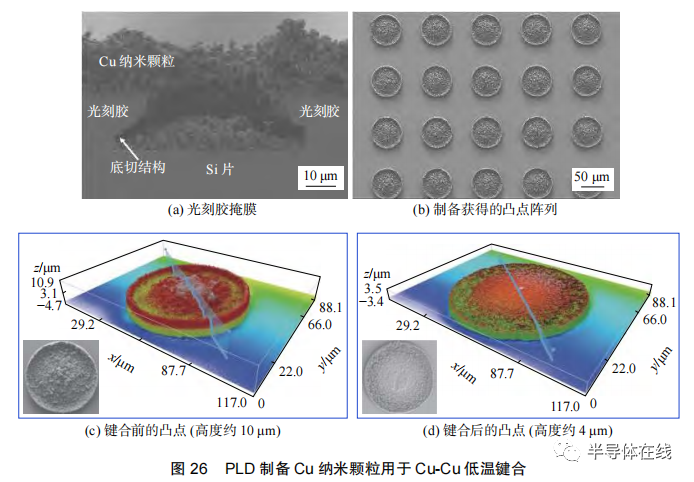

清華大學鄒貴生團隊最新提出了基于脈沖激 光沉積 (Pulsed Laser Deposition,PLD) 技術圖形化 制備 Cu 納米顆粒并用于 Cu-Cu 低溫鍵合的方法. 如圖 26 所示,該方法通過 PLD 沉積工藝制備出 Cu 納米顆粒,并以光刻膠作沉積掩膜,隨后剝離去 除光刻膠即可獲得由納米顆粒構成的凸點陣列 (直 徑 60 μm、節距 120 μm). 在 250 ℃,9 MPa,10 min, 甲酸氣氛鍵合條件下,剪切強度達 52.2 MPa,鍵合 前高度約 10 μm 的凸點被壓縮至約 4 μm. 與具有 流動性的納米焊膏相比,PLD 制備出的納米顆粒為全固態結構,因此加壓過程中不易出現溢出導致焊 點短路的問題. 此外,該方法制備出的凸點具有良 好的塑性變形能力和低溫互連性能.未來可繼續深 入對該方法的電學性能、服役可靠性等方面的研究.

5 結論

(1) 隨著主流 Sn 基軟釬焊工藝逐漸無法滿足 未來先進封裝互連的要求,Cu-Cu 鍵合技術憑借其 可實現窄節距、高性能互連且與半導體制造工藝兼 容性好等優勢脫穎而出,成為先進封裝互連的重要 發展方向.

(2) 為了降低 Cu-Cu 鍵合溫度,研究人員提出 了通過晶粒定向生長、飛行切割、插入式互連結構 等方法來提高 Cu 原子擴散速率以及采用等離子體 轟擊、金屬或有機物作鈍化層來減少/防止 Cu 表面 氧化的方法.

(3) 混合鍵合在窄節距互連時將 Cu-Cu 及介 質-介質分別鍵合起來,鍵合后的介質起到下填料的 作用,具有更優的熱/機械可靠性. 混合鍵合包括 Cu/SiO2、Cu/粘結劑鍵合兩類,鍵合時工藝要綜合 考慮 Cu-Cu 鍵合及介質-介質鍵合兩方面.

(4) 熱壓鍵合和混合鍵合對待鍵合表面的粗糙 度、光潔度、晶圓翹曲程度等有嚴格要求,往往需要 昂貴、復雜的平坦化工藝及較高的鍵合壓力來保證 鍵合表面充分接觸. 此外,混合鍵合技術在應用于 2.5D 互連時也面臨一定挑戰.

(5) 近年來,基于納米材料燒結實現 Cu-Cu 低 溫鍵合逐步獲得關注. 納米材料具有低溫連接、界 面填縫等優勢,可降低工藝要求. 研究人員采用定 向生長納米線、脫合金制備納米多孔骨架、浸蘸轉 移納米焊膏、PLD 沉積納米顆粒等方法分別實現了 焊點圖形化和 Cu-Cu 低溫鍵合,并在降低鍵合溫 度、壓力、適應基板翹曲等方面表現出一定潛力,但 仍需要更多的性能、可靠性測試作支撐. 目前納米 材料燒結連接應用于 Cu-Cu 鍵合的研究還處于起 步階段,未來繼續開發出寬工藝冗余、窄節距圖形 化、優良互連性能的納米材料互連方式仍大有可為.

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361637 -

封裝

+關注

關注

126文章

7873瀏覽量

142894 -

晶體管

+關注

關注

77文章

9682瀏覽量

138082 -

焊接

+關注

關注

38文章

3114瀏覽量

59700 -

鍵合

+關注

關注

0文章

60瀏覽量

7865 -

先進封裝

+關注

關注

2文章

400瀏覽量

241

原文標題:先進封裝中銅-銅低溫鍵合技術研究進展

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

新型銅互連方法—電化學機械拋光技術研究進展

太赫茲量子級聯激光器等THz源的工作原理及其研究進展

銅電車線材料的研究進展

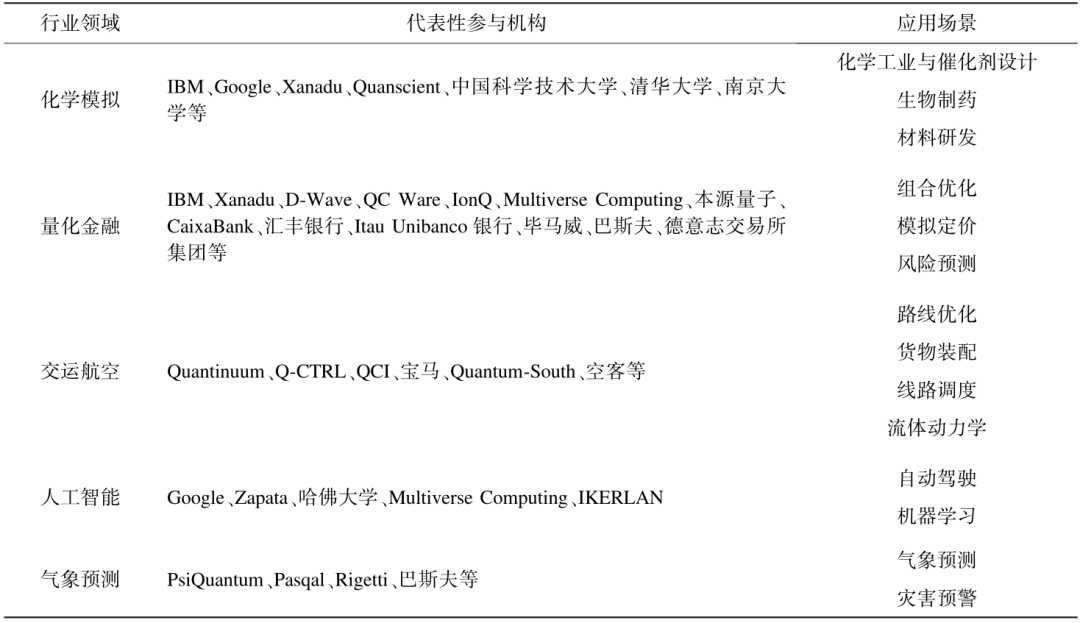

量子計算關鍵技術研究進展

從發展歷史、研究進展和前景預測三個方面對混合鍵合(HB)技術進行分析

先進封裝中銅-銅低溫鍵合技術研究進展

先進封裝中銅-銅低溫鍵合技術研究進展

評論