隨著不斷迫近摩爾定律的極限,元件的連接越發(fā)復(fù)雜。

隨著不斷迫近摩爾定律的極限,互連,也就是連接集成電路上晶體管的超薄金屬線,正在成為行業(yè)的一大瓶頸。

“大約20到25年來(lái),銅一直是互連的首選金屬。然而,我們正在接近銅縮放尺度放慢的臨界點(diǎn)。”IBM的高級(jí)互連縮放尺度首席工程師克里斯?彭尼(Chris Penny)在2022年12月的IEEE國(guó)際電子器件大會(huì)(IEDM)上說(shuō),“這為替代導(dǎo)體提供了機(jī)會(huì)。”

釕是一種領(lǐng)先的候選者,因?yàn)椋鳛闄M截面最小的互連,它可以提供比銅更好的導(dǎo)電性。但將一種金屬換成另一種金屬并不簡(jiǎn)單,這些新的互連需要不同的形狀和更高的密度,還需要更好的絕緣,以免信號(hào)削弱電容帶走所有優(yōu)勢(shì);甚至是互連的走向也會(huì)發(fā)生變化。

用于構(gòu)建銅互連的舊規(guī)則不適用于釕。銅互連使用的是所謂鑲嵌工藝。首先,芯片制造商使用光刻技術(shù)將互連的形狀刻蝕到晶體管上方的絕緣層中。然后,沉積一個(gè)襯墊和一種防潮材料,防止銅原子漂移到芯片的其他部分,避免損毀整個(gè)芯片。然后,用電鍍到晶圓上的銅填充溝槽。實(shí)際上,可能會(huì)填充太滿,因此必須擦去多余的銅。

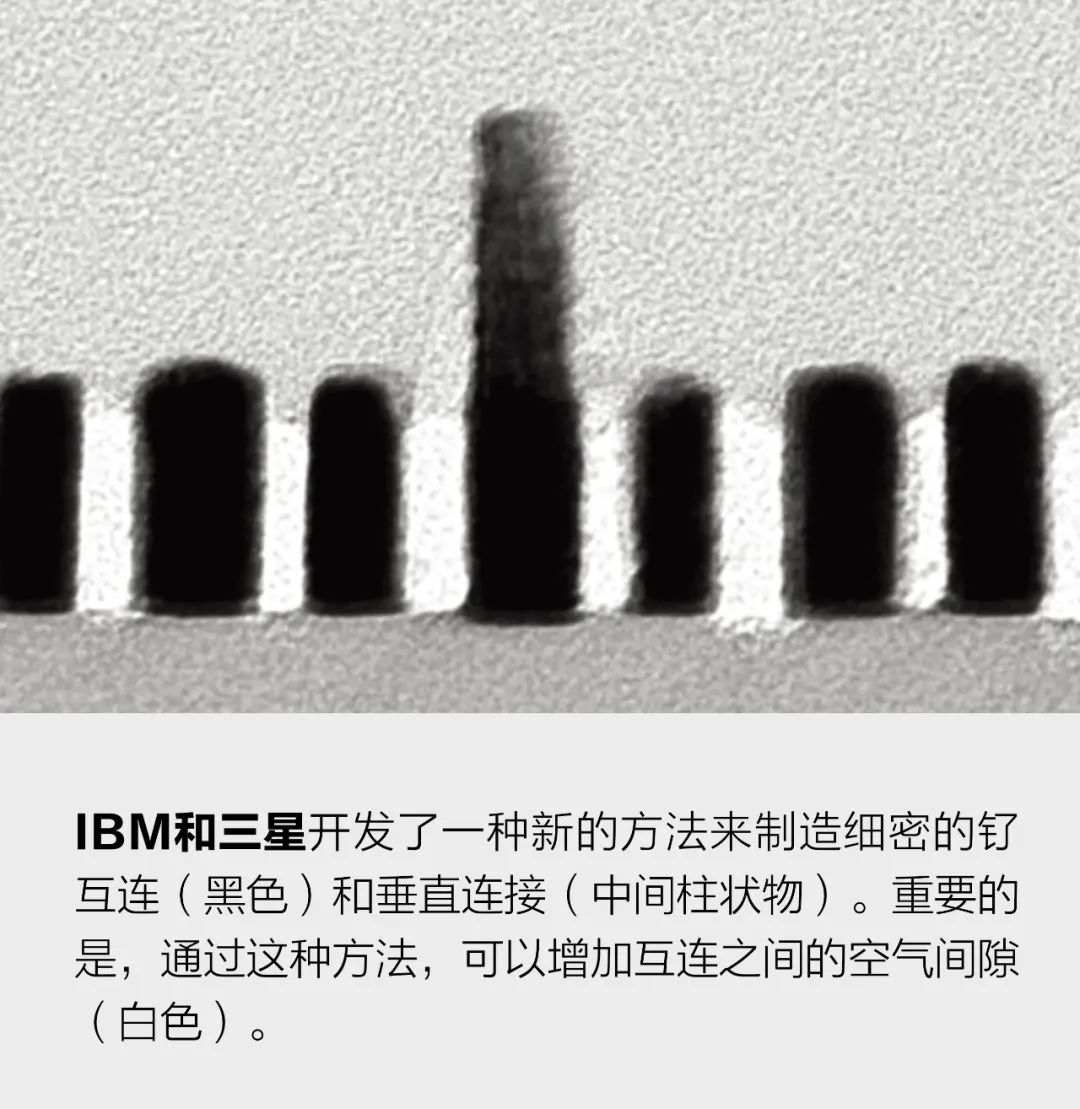

彭尼說(shuō),所有額外的材料,包括襯墊和防潮材料,占據(jù)了高達(dá)50%的互連體積。因此如果導(dǎo)電部分變窄,電阻會(huì)增加。不過(guò),IBM和三星的研究人員已經(jīng)找到了一種方法,構(gòu)建緊密間隔、低電阻釕互連,這種互連不需要襯墊或防潮材料。這種工藝被稱為間隔輔助雙重光刻(SALELE),顧名思義,它依賴于極紫外的雙重光刻。它不是填充電介質(zhì)中的溝槽,而是在金屬層上刻蝕出釕互連,然后用電介質(zhì)填充縫隙。

研究人員采用高而薄的水平互連實(shí)現(xiàn)了最佳電阻。不過(guò),由此增加了太多的電容。幸運(yùn)的是,由于SALELE在水平互連的頂部而非下面構(gòu)建過(guò)孔垂直互連,因此細(xì)長(zhǎng)的釕線縫隙空間很容易被空氣填充,而空氣是最好的絕緣體。對(duì)于這些又高又窄的互連而言,“增加氣隙的潛在益處是巨大的……可以減少30%的線路電容。”彭尼說(shuō)。

SALELE工藝“為實(shí)現(xiàn)1納米及以下的工藝提供了路線圖”,他說(shuō)。

英特爾計(jì)劃最早于2024年將電源互連從硅表面轉(zhuǎn)移到硅底面,從下面接入晶體管。這種背面電源輸入有兩個(gè)主要優(yōu)點(diǎn)。首先,它讓電流通過(guò)更寬、電阻更小的互連,可減少功率損耗。此外,它在晶體管上方為傳送信號(hào)互連騰出了空間,這意味著邏輯單元可以更小。(詳情請(qǐng)參閱《來(lái)自下方的電源》)。

在2022年的IEEE國(guó)際電子器件大會(huì)上,微電子研究中心(Imec)的研究人員宣布了一些方法,可以將電源網(wǎng)絡(luò)的端點(diǎn)更靠近晶體管,而且不會(huì)破壞這些晶體管的電子特性。不過(guò)他們也報(bào)告了一個(gè)有點(diǎn)麻煩的問(wèn)題,即用在3D芯片堆疊時(shí),背面電源可能會(huì)導(dǎo)致熱量聚集。

首先是好消息,微電子研究中心的研究人員發(fā)現(xiàn),即使在晶體管溝道區(qū)域右側(cè)(盡管仍在其下方幾十納米)構(gòu)建了功率傳輸軌道,晶體管也能正常工作。這可能意味著能實(shí)現(xiàn)更小的邏輯單元。

而壞消息是,在另一項(xiàng)研究中,微電子研究中心的工程師模擬了同一款未來(lái)CPU的幾個(gè)版本,發(fā)現(xiàn)了一些令人不安的問(wèn)題。有些模擬采用了目前的正面電源網(wǎng)絡(luò),其中數(shù)據(jù)和電源的互連都建立在硅上方的層面中。有一些則采用了背面電源網(wǎng)絡(luò)。其中一個(gè)是由兩個(gè)CPU面對(duì)面粘合而成的3D堆疊,底部是背面電源,頂部是正面電源。

2D CPU模擬證實(shí)了背面電源的優(yōu)勢(shì)。與正面電源相比,它能夠?qū)㈦娫垂β实膿p失減少一半。瞬態(tài)電壓下降也不明顯。更重要的是,CPU面積縮小了8%。然而,背面芯片最熱部分與其邊緣的溫差比正面芯片最熱部分與其邊緣的溫差增加了約45%。可能的原因是,為了保持穩(wěn)定,背面電源要求將芯片削薄到需要與單獨(dú)硅片粘合。這種粘合起到了絕緣體的作用,從而將熱量困在了芯片內(nèi)部。

真正的問(wèn)題出現(xiàn)在3D集成電路上。頂部CPU必須從底部CPU獲得電源,但到達(dá)頂部的長(zhǎng)連線產(chǎn)生了不良的后果。雖然底部CPU的電壓仍比正面芯片穩(wěn)定,但頂部CPU的表現(xiàn)要差得多。而且3D集成電路的電源網(wǎng)絡(luò)消耗的功率超過(guò)了單個(gè)正面芯片的電源網(wǎng)絡(luò)所消耗功率的2倍。更糟糕的是,熱量無(wú)法很好地從3D堆疊中排出,底部最熱部分的溫度幾乎是單個(gè)正面CPU的2.5倍。雖然頂部CPU的溫度低一些,但也沒(méi)有低很多。

微電子研究中心的背面電源網(wǎng)絡(luò)項(xiàng)目負(fù)責(zé)人兼高級(jí)研究科學(xué)家陳榮梅在IEEE國(guó)際電子器件大會(huì)上告訴工程師,應(yīng)當(dāng)承認(rèn)3D集成電路模擬有些不切實(shí)際。將兩個(gè)完全相同的CPU堆疊在一起的情形不太可能發(fā)生。(更常見(jiàn)的是將內(nèi)存與CPU堆疊在一起。)“這并不是一種很公平的比較。”他說(shuō),但卻指出了一些潛在的問(wèn)題。

作者:Samuel K. Moore

編輯:黃飛

-

英特爾

+關(guān)注

關(guān)注

61文章

9978瀏覽量

171883 -

摩爾定律

+關(guān)注

關(guān)注

4文章

634瀏覽量

79077 -

晶體管

+關(guān)注

關(guān)注

77文章

9701瀏覽量

138373 -

芯片制造

+關(guān)注

關(guān)注

10文章

624瀏覽量

28837

原文標(biāo)題:小連接中的大難題

文章出處:【微信號(hào):WW_CGQJS,微信公眾號(hào):傳感器技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

電路中的主動(dòng)元件,被動(dòng)元件,有源器件,無(wú)源器件,分立元件,集成電路怎么區(qū)分?

OTDR測(cè)試中常遇到的問(wèn)題及解決

VSS遇到的常見(jiàn)錯(cuò)誤及解決方法

NTC溫度傳感器解決儲(chǔ)能領(lǐng)域難題

工業(yè)連接器的“選擇難題”:焊接款VS鎖線款,誰(shuí)更便捷?

pmu電源管理單元設(shè)計(jì)遇到的問(wèn)題

壓電元件的并聯(lián)與串聯(lián)的特點(diǎn)

元件的連接會(huì)遇到哪些難題?

元件的連接會(huì)遇到哪些難題?

評(píng)論