1.什么是控制交互信號(hào)?

答:控制交互信號(hào)用于作為控制指示信號(hào),比如當(dāng)某個(gè)電路模塊有數(shù)據(jù)輸入端口data,但是電路不可能每個(gè)時(shí)鐘周期都對(duì)端口輸入的數(shù)據(jù)做處理,那一般上一級(jí)電路會(huì)同時(shí)給出一個(gè)指示信號(hào),比如in_valid,用于表示當(dāng)前端口data輸入的數(shù)據(jù)是有效的,電路需要對(duì)其進(jìn)行采集或做運(yùn)算處理。同樣的對(duì)于電路模塊輸出數(shù)據(jù)時(shí),也需要給出類(lèi)似的信號(hào),表明當(dāng)前輸出端口的數(shù)據(jù)是否有效,例如o_valid信號(hào)等。

還有就是比如像FIFO,RAM的讀寫(xiě)使能信號(hào),用于控制FIFO,RAM是否需要正常進(jìn)行工作;讀寫(xiě)控制信號(hào)用于指示是讀還是寫(xiě)操作行為。以及總線的一系列控制信號(hào)等,CPU的指令等等,都可以說(shuō)是控制信號(hào)。常用于作為控制模塊產(chǎn)生控制信號(hào)的就是狀態(tài)機(jī)。

總結(jié)一下,就是沒(méi)有控制信號(hào)只有運(yùn)算電路,電路就是塊板磚,我行我素,無(wú)任何意義,當(dāng)我們?cè)O(shè)計(jì)電路模塊的時(shí)候,往往最先需要搞明白的就是本電路模塊的交互控制接口的時(shí)序。

2.跨時(shí)鐘域時(shí),控制信號(hào)從慢時(shí)鐘域(時(shí)鐘頻率較小)到快時(shí)鐘域(時(shí)鐘頻率較大)快遞時(shí)會(huì)存在什么問(wèn)題呢?

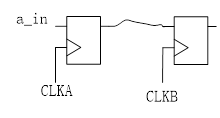

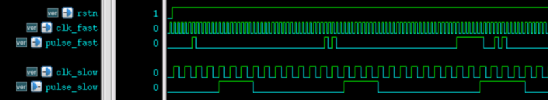

答:如下圖所示,CLK1為慢時(shí)鐘域的時(shí)鐘,IN_VALID信號(hào)由慢時(shí)鐘域電路生成,比如用于指示DATA(由CLK1時(shí)鐘域電路生成)的有效,或者指示完成一次運(yùn)算。原本IN_VALID在CLK1時(shí)鐘域下只有一個(gè)脈沖寬度,表示完成一次運(yùn)算。但是跨時(shí)鐘域傳遞到CLK2(快時(shí)鐘域下),CLK2由于頻率較快,多個(gè)上升沿都采集到IN_VALID為高,在CLK1時(shí)鐘域下就會(huì)誤以為完成了多次運(yùn)算(或者連續(xù)多個(gè)DATA為有效的)。

3.上述問(wèn)題怎么解決呢?

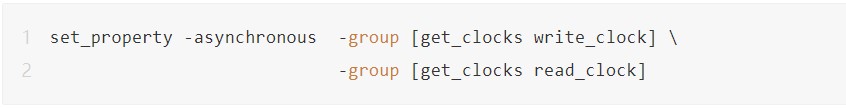

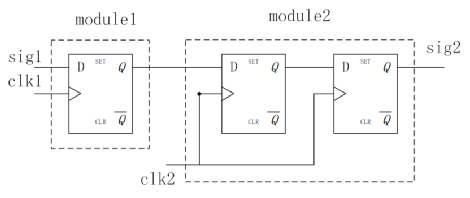

答:如果需要跨時(shí)鐘域的控制信號(hào)不會(huì)出現(xiàn)多個(gè)脈沖連續(xù)為高的情況的話,則可以在快時(shí)鐘域通過(guò)邊沿檢測(cè)電路解決。電路如下。將最后的IN_VALID_CLK2作為最后的控制信號(hào)。

其波形如下:

4.如果IN_VALID有多個(gè)連續(xù)的為高電平的情況怎么辦?

答:如果IN_VALID是用來(lái)傳遞數(shù)據(jù)的,用來(lái)指示DATA有效的,則可以采用一個(gè)異步FIFO將數(shù)據(jù)進(jìn)行緩存,將IN_VALID作為FIFO的寫(xiě)使能信號(hào)。如若是其他的這種情況則需要按情況來(lái)定制電路。

拓展問(wèn)題

1.脈沖上升沿檢測(cè)電路(被檢測(cè)的脈沖寬度不小于一個(gè)時(shí)鐘周期)。

2.脈沖下降沿檢測(cè)電路(被檢測(cè)的脈沖寬度不小于一個(gè)時(shí)鐘周期)

3.脈沖邊沿(IN_VALID的下降沿、上升沿時(shí)電路都會(huì)輸出一個(gè)高脈沖)檢測(cè)電路(被檢測(cè)的脈沖寬度不小于一個(gè)時(shí)鐘周期)。

下面給出邊沿檢測(cè)電路的示例Verilog代碼:

向上滑動(dòng)閱覽

module EDGE_DEC(

input clk2,

input rst_n,

input in_valid,

output in_valid_edge

);

reg in_valid_d;

reg in_valid_dd;

always @( posedge clk2 or negedge rst_n ) begin

if( !rst_n )

in_valid_d <= 1'b0;

else

in_valid_d <= in_valid;

end

always @( posedge clk2 or negedge rst_n ) begin

if( !rst_n )

in_valid_dd <= 1'b0;

else

in_valid_dd <= in_valid_d;

end

assign in_valid_edge = in_valid_d ^ in_valid_dd;

endmodule

-

RAM

+關(guān)注

關(guān)注

8文章

1369瀏覽量

114759 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

492瀏覽量

27561 -

FIFO存儲(chǔ)

+關(guān)注

關(guān)注

0文章

103瀏覽量

6014 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17183 -

控制器

+關(guān)注

關(guān)注

0文章

24瀏覽量

3274

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

跨時(shí)鐘域控制信號(hào)傳輸設(shè)計(jì)方案

關(guān)于跨時(shí)鐘域信號(hào)的處理方法

怎么將信號(hào)從一個(gè)時(shí)鐘域傳遞到另一個(gè)時(shí)鐘域

同步從一個(gè)時(shí)鐘域到另一個(gè)時(shí)鐘域的多位信號(hào)怎么實(shí)現(xiàn)?

多時(shí)鐘域的設(shè)計(jì)和綜合技巧系列

跨時(shí)鐘域信號(hào)同步的IP解決方案

CDC跨時(shí)鐘域的基礎(chǔ)概念

跨時(shí)鐘域電路設(shè)計(jì):多位寬數(shù)據(jù)通過(guò)FIFO跨時(shí)鐘域

跨時(shí)鐘域信號(hào)該如何處理呢?

控制信號(hào)從慢時(shí)鐘域到快時(shí)鐘域快遞時(shí)會(huì)存在什么問(wèn)題呢?

控制信號(hào)從慢時(shí)鐘域到快時(shí)鐘域快遞時(shí)會(huì)存在什么問(wèn)題呢?

評(píng)論