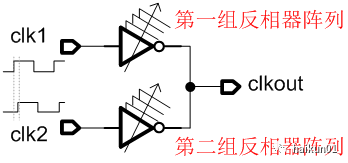

下圖給出了反相器相位插指器的基本結構。結構很簡單,兩個反相器陣列輸入分別接兩個時鐘,輸出直接短接在一起,數字信號控制反相器陣列選通的數目。

兩個反相器陣列輸出短接,輸入接不同相位的時鐘,即構成了相位插值器

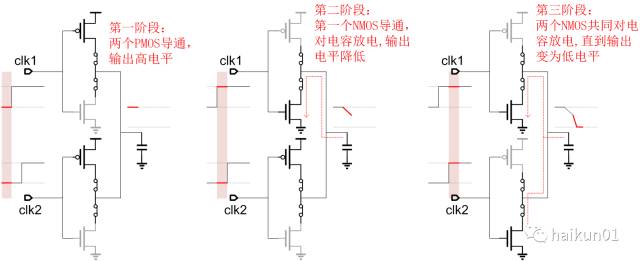

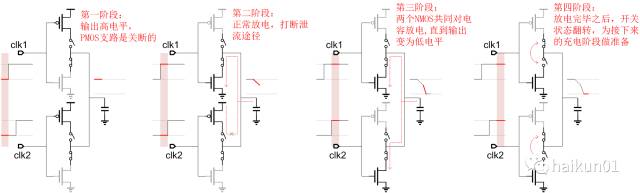

下面我們來看輸入時鐘上升沿來臨時的情況(下降沿的情況類似)。在時鐘上升沿來臨之前,所有的PMOS導通,NMOS關斷,輸出為高電平(下圖第一階段)。接下來,第一個時鐘clk1的上升沿先來臨,第一組反相器陣列的NMOS導通,開始對輸出節點的電容放電,輸出電平逐步將小(下圖第二階段)。一直到第二個時鐘clk2的上升沿到來,第二組反相器陣列的NMOS也導通,一起對輸出節點的電容放電,直到輸出電平變為低電平(下圖第三階段)。最終得到的輸出電壓波形可以使用分段直線來近似。

相位插值器工作原理,利用兩個階段不同的充放電速度來實現相位插值

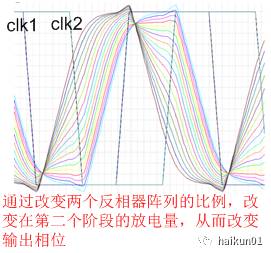

那么我們怎么改變輸出的相位呢?

很簡單, 改變兩組反相器陣列使能的數目即可改變輸出相位 。當第一組反相器陣列數目多,那么在第一個放電階段放掉的電荷多,最終輸出波形的相位靠前;當第一組反相器陣列數目少,則第一個放電階段放掉的電荷少,輸出波形的相位靠后。最終得到的不同輸出波形如下圖所示。

從上面對反相器相位插值器工作原理的描述,很容易得知設計反相器相位插值器的幾個關鍵點:

1)相位插值器輸出相位的調節范圍等于兩個輸入時鐘的相位差;

2)相位插指器的輸出波形上升/下降沿不能太陡峭。

設想這一種情況,在第二個時鐘上升沿到來之前,第一組反相器陣列的NMOS已經把輸出電壓放電放到低電平,第二組反相器陣列的NMOS無電可放,輸出的相位與第二個時鐘無關,那也就不能相位插值了。

3)當兩個輸入時鐘間隔越近,相位插值器的性能越好。

一般而言,我們要求反相器陣列輸出的上升時間和下降時間大于兩個輸入時鐘的間隔。較小的間隔意味著可以取較短的上升時間/下降時間,也意味著jitter和功耗表現好。這也是為什么這篇論文在多模分頻器MMD之后,又插入了一級可調延時器,產生22.5度的時鐘間隔。

4) 還有一點比較隱晦,不太容易得出:對于反相器相位插值器,輸入時鐘的邊沿越陡峭越好。

存在的問題

基于反相器的相位插值器主要有兩點問題:

1)工作頻率范圍有限。 前面已經講到,反相器陣列的輸出上升下降時間需要大于輸入時鐘的間隔。對于一定的角度,頻率變低時,相應的時間間隔變大,本來合適的上升下降時間變得相對較快,導致線性度變差。 若想要在各個頻率下都保證較好的線性度,則需要針對頻率對反相器的速度進行校準。 這又是件麻煩事。

不同工作頻率下的線性度

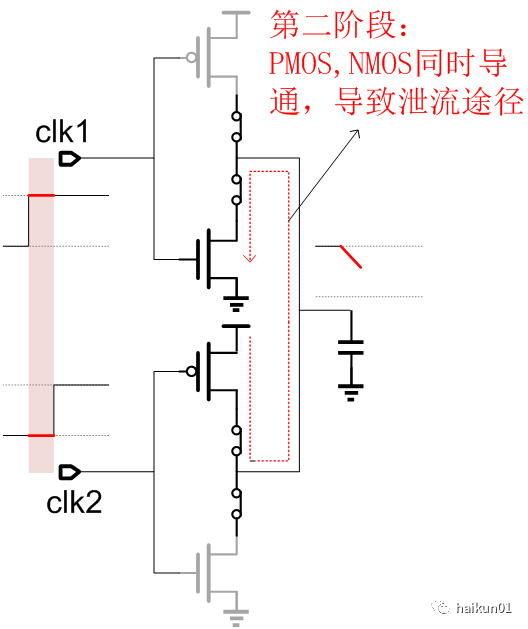

2)從之前的圖可以看出, 在兩個時鐘上升沿之間的這一段時間,第一個反相器陣列的NMOS打開,第二個反相器陣列的PMOS打開,這樣實際上形成了一條從電源到地的通路。 這是我們不想要的,這會消耗不必要的電流,同時也使線性度變差。下一部分我們會看到這篇論文是怎么解決這個問題的,以及付出的代價。

論文中改進的相位插值器

上面講到,PMOS的導通導致了電流泄露。既然這樣, 那么最直接的解決思路:我把PMOS這個通路關斷不就行了么? 這篇論文的確是這樣做的。一般反相器的使能開關同時導通或關斷PMOS和NMOS支路,在這里被分開了。在放電過程中,只導通NMOS支路,從而掐斷了泄流路徑(下圖第二階段)。

現在放電階段沒問題了,那充電階段呢? 如果使能開關保持不變,那PMOS通路一直被關斷,等時鐘下降沿到來之后也沒有辦法充電。 因此,這篇論文在這里加了一個反饋: 檢測輸出電平,當放電完畢后,通過反饋使得兩路的使能信號翻轉,把NMOS支路關斷,PMOS支路打開 (下圖第四階段)。預先為充電階段做好準備,待時鐘下降沿一到就可以開始充電了。

在放電時,只打開NMOS支路,充電完成后通過反饋翻轉開關狀態。通過精細控制開關,在不影響插值功能的情況下掐斷了泄流通路

從上面的圖可以看出, 在第二個上升沿到第一個下降沿這一段時間內,輸出節點是懸空的。這樣有兩個問題,一是晶體管的漏電會導致輸出節點電平變化,二是懸空的節點更容易受到噪聲的影響。 因此,這篇論文里又加入了一些電平保持單元,在放電和充電之間使能,用于保持輸出電平。

總結起來,這篇論文的解題方法是: 精細控制反相器的NMOS和PMOS支路,而不是傳統反相器相位插值器里的同開同關。 具體實施上,將一個時鐘周期分成了四份,在充電時,只打開PMOS支路,充電完成后通過反饋翻轉開關狀態;放電情況類似。

付出的代價

下面來講講這種解決方案付出的代價。

首先,開關的控制變得很復雜,不合適高頻。 從上面的原理描述我們可以知道, 在一個時鐘周期內,開關的狀態要翻轉數次,反饋環路需要快速穩定下來,這對速度提出了很高的要求。 而在傳統設計中,開關本身的速度可以遠慢于時鐘速度的。此論文工作頻率為2GHz,相對于它使用的28nm工藝相對較低,因此它使用這種方法還能得到一些好處。如果工作在14GHz或者28GHz,我猜好處會變得極其有限,甚至得不償失。

其次,版圖會變得比較復雜。 開關有速度要求,因此開關的控制邏輯和反相器本身不能分隔太遠,否則寄生電容大,開關無法在半個時鐘周期內翻轉并穩定。整個開關和反相器陣列耦合在一起,將會導致版圖變得復雜。在2GHz處額外的寄生效應不明顯,到了更高頻時,寄生效應會變得很關鍵。

原論文中的版圖布局較復雜

-

反相器

+關注

關注

6文章

311瀏覽量

43294 -

分頻器

+關注

關注

43文章

447瀏覽量

49887 -

電容放電

+關注

關注

0文章

29瀏覽量

8189 -

PLL電路

+關注

關注

0文章

92瀏覽量

6403 -

NMOS管

+關注

關注

2文章

121瀏覽量

5407

發布評論請先 登錄

相關推薦

AD6649BCPZ&a/d converter

Analog-to-Digital Converter(模數轉換器)的使用

Digital Control Concepts For P

Analog-to-Digital Converter Gr

Time-to-Digital-Converter應用指南

什么是ADC (Analog to Digital Conv

MAX1425 10-bit, analog-to-digital converter

Configuring the MAX35101 Time-to-Digital Converter as an Ultrasonic Water Meter

TMS320x281x_DSP_Analog-to-Digital_Converter(ADC)Reference_Guide

AD9286: 8-Bit, 500 MSPS, 1.8 V Analog-to-Digital Converter (ADC) Data Sheet

AD9265: 16-Bit, 125 MSPS/105 MSPS/80 MSPS, 1.8 V Analog-to-Digital Converter Data Sheet

AD9254: 14-Bit, 150 MSPS, 1.8 V Analog-to-Digital Converter Data Sheet

AD9255: 14-Bit, 125 MSPS/105 MSPS/80 MSPS, 1.8 V Analog-to-Digital Converter Data Sheet

UG-1630: Evaluating the AD9146 Dual, 16-Bit, 1230 MSPS, TxDAC+? Digital-to-Analog Converter

被ISSCC接收的Digital to Time Converter是如何設計的?

被ISSCC接收的Digital to Time Converter是如何設計的?

評論