來源:《半導體芯科技》雜志

是德科技(Keysight Technologies, Inc.)發布一個全新的通用信號處理構架(USPA)建模平臺,助力半導體公司能夠在實時開發環境中,利用完全兼容的、基于標準的數字孿生信號進行完整的芯片原型設計、驗證和預流片。

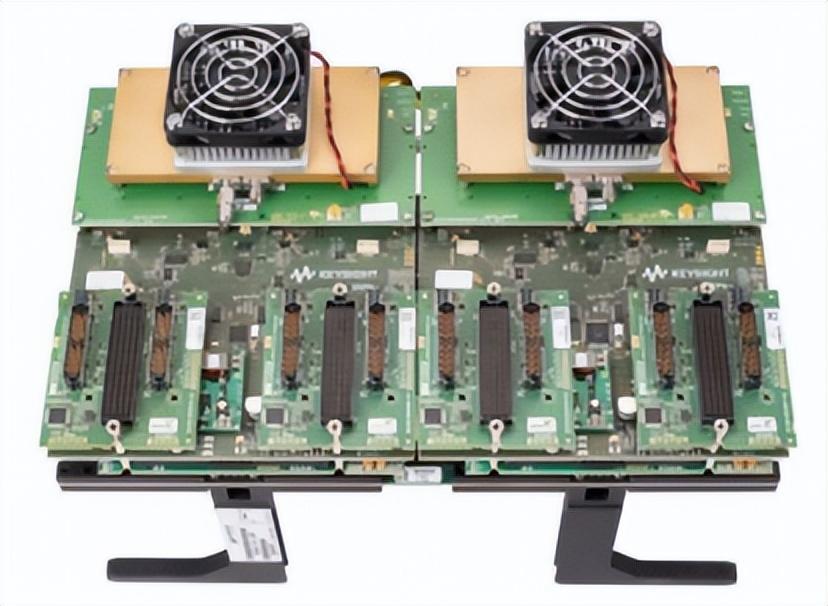

△圖:是德科技M8135A—預配置的USPA系統,適用于單通道收發信機相關應用

流片是芯片設計過程的最后一步,也是一個成本越來越昂貴的過程,幾乎沒有給設計失敗留下任何空間。如果初始設計在流片后被證明是失敗的,則芯片制造商必須重新開始新的“重新設計”,這可能需要12個月或更長時間才能完成。除了占用寶貴的研發資源外,這些芯片重新設計還可能導致芯片制造商錯過一個狹窄的上市時間窗口。

為降低設計失敗和代價高昂的重新設計的風險,是德科技USPA平臺為芯片設計人員和工程師提供了完整的數字孿生信令,以便在他們投入流片之前驗證設計。USPA平臺通過將超快信號轉換器與高性能、完全模塊化的現場可編程門陣列(FPGA)原型系統集成,為設計人員提供了一種針對原來專有定制原型建模系統的替代方案。

獨特的USPA原型設計平臺具有以下優勢:

?通過速率高達68GS/s的ADC模數接口和72GS/s的DAC數模接口進行高速數字仿真,可支持最高性能的光電開發項目。

?提供范圍廣泛的輸入/輸出接口,適用于包括6G無線開發、數字射頻存儲器、高級物理研究和高速數據采集應用在內的應用,例如雷達和射電天文。

?提供兩種靈活的配置,一種是適用于單通道收發信機應用的預配置系統和另外一種完全可配置的模塊化組件,這些組件可以靈活組合以支持廣泛的單通道和多通道應用。此外,預配置的系統可以使用額外的組件進行擴展,這些組件利用了平臺架構的模塊化、可擴展性和經濟高效的可重用性。

Avance Semi, Inc.首席執行官Hong Jiang表示:“當我們開始為相干光纖通信市場開發我們的第一個ASIC時,我們明白我們可能只有一次機會把它做對,而且第二次流片將非常昂貴并且耗時,以至于我們可能會錯過狹窄的上市時間窗口。借助是德科技的USPA平臺和我們的系統集成工作,我們可以在設計過程中實時優化和驗證我們的設計。這就像一個‘免費的預流片’,我們可以根據需要多次運行。這種方法節省了開發時間和成本,同時顯著提高了我們對設計和產品發布時間表的信心。”

是德科技副總裁及網絡和數據中心解決方案總經理Joachim Peerlings博士說:“通過加速芯片開發和降低相關風險,是德科技USPA提供了一種新的端到端解決方案,可以在高成本的設計環境中應對開發前沿技術的挑戰。這個強大的平臺為芯片開發人員的未來芯片產品提供了一個數字孿生,使他們能夠在承擔流片費用和風險之前充分驗證他們的設計和算法。”

審核編輯黃宇

-

半導體

+關注

關注

334文章

27290瀏覽量

218093 -

流片

+關注

關注

0文章

27瀏覽量

9758 -

數字孿生

+關注

關注

4文章

1319瀏覽量

12243

發布評論請先 登錄

相關推薦

如何實現數字孿生?分為以下四步驟

數字孿生對工業4.0的影響

如何實現數字孿生?看這篇就夠了

基于數字孿生的智慧城市

數字孿生關鍵技術及體系架構

半導體先進封裝技術

是德科技使用數字孿生信令實現先進的半導體流片原型設計

是德科技使用數字孿生信令實現先進的半導體流片原型設計

評論