一,LVDS邏輯電平

LVDS :低電壓差分信號(Low-Voltage Differential Signaling)是美國國家半導體(National Semiconductor, NS)于1994年提出的一種信號傳輸模式的電平標準,它采用極低的電壓擺幅高速差動傳輸數據(采用CMOS 工藝的低電壓差分信號器件),實現點對點(或則點對多:M-LVDS)的連接,具有低功耗、低誤碼率、低串擾和低輻射等優點,已經被廣泛應用于串行高速數據通訊場合當,如高速背板、電纜和板到板數據傳輸與時鐘分配,以及PCB內的通信鏈路。

LVDS 器件的傳輸機制是把 TTL 邏輯電平轉換成低電壓差分信號,以便于高速傳輸。與傳統的 ECL邏輯相比,它采用 CMOS 工藝,其電壓擺幅更低(LVDS只有 400mV,ECL 為 800mv),動態功耗更小(輸出電流 35mA,只有 ECL 電路的 1/7),低 EMI,價格更低,因而在中等頻率(幾百M幾GHz)差分信號應用上具有較大的優勢。

——LVDS技術規范有兩個標準,即TIA(電訊工業聯盟)/EIA(電子工業聯盟)的ANSI/TIA/EIA-644標準(LVDS也稱為RS-644接口)與IEEE 1596.3標準。

1,LVDS基本電路結構

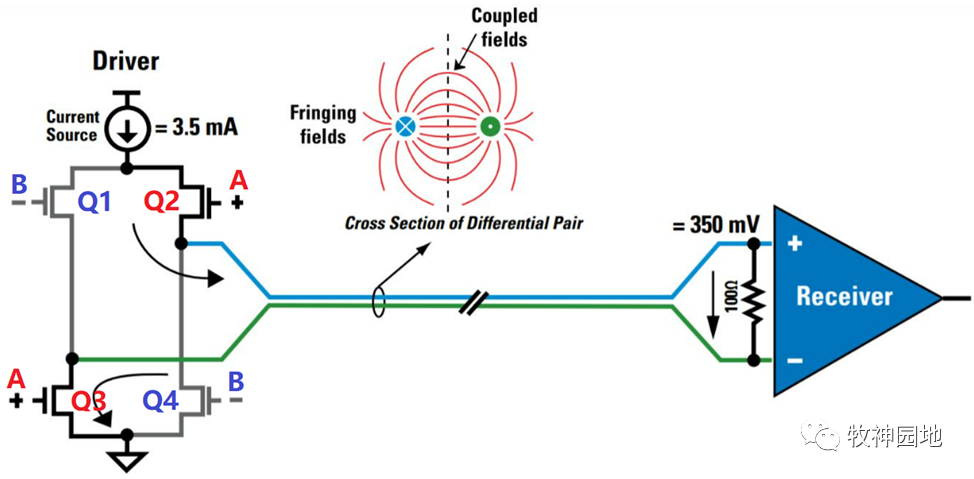

如下圖所示為典型的基本LVDS電路,采用一對差分信號線傳輸數據;通過驅動3.5mA的穩定電流源,以350mV低振幅(100Ω終端匹配)的差動信號來高速傳送數據。其數據傳輸速度在規格內限定最大為655Mbit/秒,但這并不是極限值。通過各半導體廠商改進,可以實現3Gbit/秒左右的高速傳輸速度。

- LVDS的輸出端驅動是一個3.5mA的電流源,并由兩組MOS管(4個)組成一對發送輸出;

- 當A+導通,B-斷開時:

1, 電流從右上角Q2(A+ MOS管)驅動出到藍色傳輸線,即右上A+ MOS管電流方向是:電流源(Driver)à右上A+ MOS管à藍色傳輸線à100Ω終端電阻;

2, 左下角Q3(A+ MOS管)驅動接至GND,所以此時電流從綠色傳輸線通過左下角Q3流出到GND;左下A+ MOS管電流方向是:GNDà左下A+ MOS管à綠色傳輸線à100Ω終端電阻;

3, 整個電流通路最終電流在100Ω終端電阻側導通,并形成輸出電壓:3.5mA *100Ω = 350mV。

——因為傳輸線提供的100Ω阻抗是交流阻抗(只在信號邊沿有用的阻抗,忘記的胖友們務必復習《從電感、電容到理想傳輸線》相關章節),對于直流來說是傳輸線是高阻抗,所以終端必須有100Ω端接電阻來提供信號固定電平狀態下的回流,以保證輸出電壓;

——需要再次強調的是:3.5mA****電流從電源源流出到藍色傳輸線,和綠色傳輸線3.5mA 電流流入GND ,這兩者同時發生的,才能保證信號邊沿的同步 ;驅動電流的路徑 并非是 :電流源àQ2à藍色傳輸線à100Ω終端電阻à綠色傳輸線àQ3àGND(有點違反直覺哈,胖友們務必回顧“傳輸線”相關理論)。

- 當B-導通,A+斷開時:

1, 此時3.5mA驅動電流從左上角Q1(B- MOS管)流出,并流入綠色傳輸線;

2, 同時藍色傳輸線電流流入右下角Q4(B- MOS管);

——具體電流傳輸的方向,如上。

3, 電流通路最終電流還是在100Ω終端電阻側導通,但是電流方向與“A+導通,B-斷開”相反,并形成反向的輸出電壓:-3.5mA *100Ω = -350mV。

- 最終在輸出端形成 +350mV和-350mV信號擺幅的差分輸出。

——在一本非常優秀的“信號完整性”相關書籍中,作者認為LVDS是偽差分線,因為從LVDS驅動機制來說,它只需要驅動3.5mA電流流過終端100Ω電阻形成的壓差來實現,似乎并不需要一定是對耦差分線;但通過上述兩條傳輸線的電流路徑分析,我覺得LVDS應該是真正的對耦差分線。

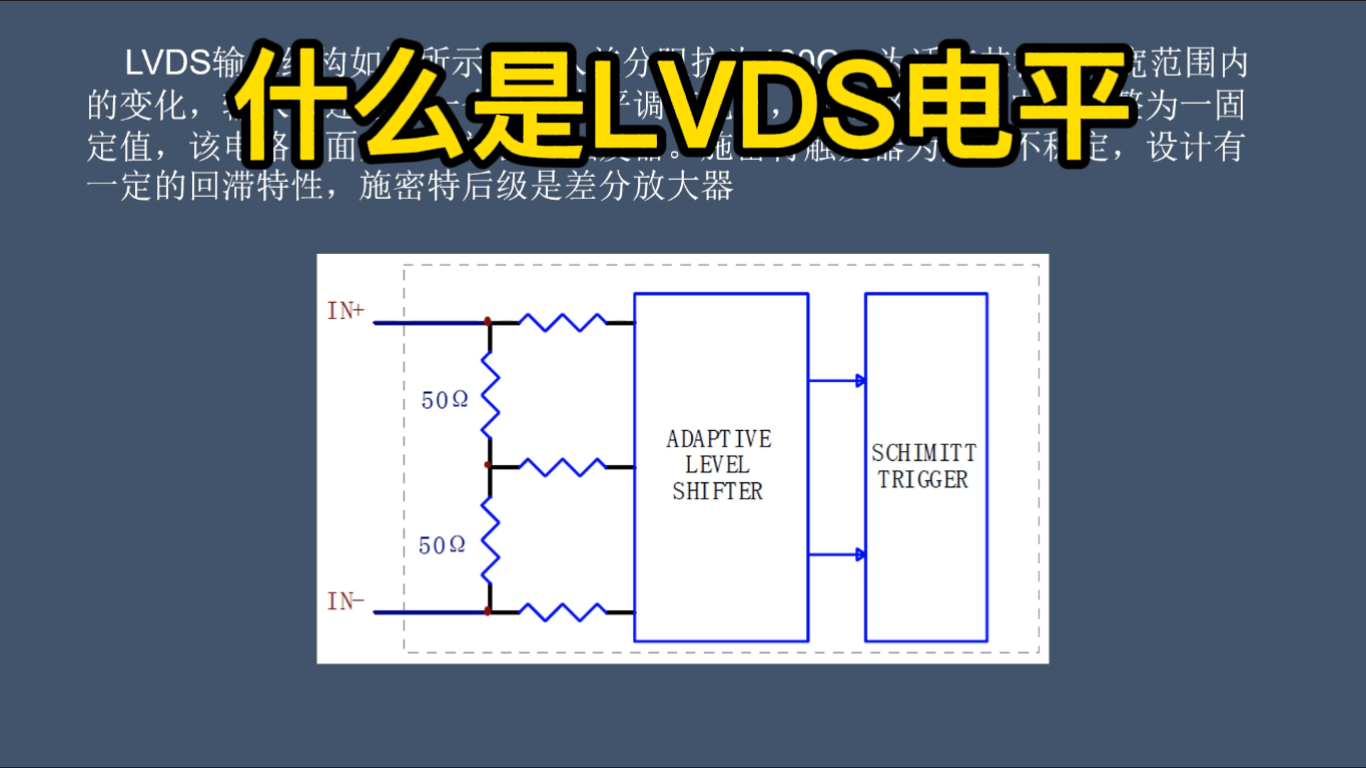

2,LVDS電平分析

LVDS的差分信號的兩根差分信號線:正電極信號(A+)和負電極信號(B?);共模偏置電壓為:1.2V,差模電壓擺幅是:350mV。如果我們用示波器來測試信號波形,并對兩個信號電壓值取差:(A+)?(B?);那么我們可以得到差分擺幅為:-350mV和+350mV。具體波形如下圖所示。

上述波形是理想的情況,如下所示為器件資料(Intel? Stratix? 10 Device)中關于LVDS相關參數的描述;其輸出共模電壓(VOCM)和差模電壓(VOD)的具體規格如下藍色框內所示;如果要正確接收其它器件發送過來的信號,必須滿足紅色框內關于輸入共模電壓(VICM(DC))和差模電壓(VID)的參數要求。

3,LVDS電平特點

LVDS 的特點是電流驅動模式,低電壓擺幅 350mV 可以提供更高的信號傳輸速率,使用差分傳輸的方式可以減小信號和噪聲的EMI輻射:

- 輸出電平切換不需要設計類似TTL/CMOS的“死區時間”,可以支持更高速率;

——由于是電流驅動,所以不需要防備電壓源直接接地的風險。

- 低輸出電壓擺幅(350mV)):

1, 可以支持更高速率(1Gbps以上),具體支持速率對比如左下圖所示;

2, 功耗消耗更低(如右下圖所示),內部散熱更小,有助于提供芯片集成度。

- 低EMI電磁輻射:

1, 低的信號邊緣變化率:dV/dt = 0.350V/0.5ns = 0.7V/ns;

——如下圖所示,雖然速率高(ps級別),但是由于擺渡小所以邊沿變化率要求不高。

2, 耦合差分信號線的電磁干擾相互抵銷,對外輻射小;

3, 耦合差分信號線抗電磁干擾性強。

- 允許輸入的共模電壓范圍大,支持1V的共模偏置電壓差(如上圖所示);

- 傳輸線匹配簡單。

——無論是使用電纜還是PCB走線,LVDS的高速信號傳輸都必須考慮阻抗匹配問題:阻抗不連續或終端不匹配會影響傳輸信號;所以需要控制傳輸線阻抗,并保證合適的端接。

1, 對于點到點的鏈路(LVDS),如下圖所示,只需要使用100Ω端接在距離驅動器最遠處;

——如果輸出端和輸入端共模偏置電壓不匹配(或考慮上電時序的漏電影響),則需串接100nF電容器進行AC耦合,AC耦合電容器對信號傳輸影響不大(相當于短路,胖友們可以動手算一算:100nF電容器在100MHz頻率時的阻抗是多少~)。

2, 對于多分支總線(M-LVDS),如果驅動器在總線的一端,則可采用相同的端接方法(即,在距離驅動器最遠端端接100Ω電阻,如下圖所示);否則需要端接總線的兩端。

——M-LVDS可以實現點對多,而且長距離的傳輸(如下左圖所示),與RS-485總線的應用有明顯重疊;兩者參數對比如下右圖所示,有興趣的胖友可以自行學習;本章不對M-LVDS和RS-485展開分析。

3, 如下圖所示,還有一種多點拓撲是:“半雙工”拓撲;它由兩個驅動/接收對組成,在單個互連上傳輸和接收兩個點之間的信號。

4,LVDS電路設計

對于LVDS PCB的設計來說,不論LVDS信號對數量是多少,都建議使用多層板,最少四層設置: LVDS、GROUND、POWER、TTL。

- 對 LVDS 信號和其它信號(舉個栗子,TTL 信號;避免受到干擾),最好能使用不同的走線層,如果因為設計限制必須使用同一層走線,LVDS 和 TTL 的距離應該足夠遠,至少應該大于 3~5 倍差分線間距;

- 保證收發器到接插件的距離足夠短,防止由于 Stub 線過長引起信號的崎變,一般要求距離小于 10mm;

- 對收發器的電源使用濾波電容,濾波電容的位置應該盡量靠近電源和地管腳,濾波電容其的容值參照器件手冊;

——如果沒有推薦濾波電容器值,那么可以按照1個uF級電容(舉個栗子:10uF)+每個管腳1個100nF電容的經驗值進行設計。

- 對電源和地管腳與參考平面的連接應該使用短和粗的連線連接,同時使用多點連接;

——參考《電源完整性》相關章節,主要為了減小寄生電感。

- 對走線的阻抗要求進行控制,一般差分阻抗控制在 100 歐姆;

——匹配電阻的阻值可以進行調整,根據差分線阻抗和輸出差模電壓范圍來決定。

- 對走線方式的選擇沒有限制,微帶線和帶狀線均可,但是必須注意有良好的參考平面。對不同差分線之間的間距要求間隔不能太小,至少應該大于 3~5 倍差分線間距;

- 對接收端的匹配電阻到接收管腳的距離要盡量的靠近(一般小于 7mm,最大不能超過 12mm); 未使用的輸入管腳可以懸空,如下圖所示;

- LVDS 在電纜中的使用同在 PCB 中的使用方式并無大的差別,需要注意在不同電纜中 LVDS 差分信號需要不同的排布方式,如下圖所示;

——電纜本身的插損需要滿足支持該頻率高速信號傳輸,舉個栗子:屏蔽雙絞線比較適合作為 LVDS 傳輸的介質,CAT3 電纜可以傳輸 5m,CAT5 電纜可以傳輸更遠距離的 LVDS 信號。

二,CML邏輯電平

CML:電流模式邏輯(即Current Mode Logic),電路主要靠電流驅動,也是所有高速數據接口形式中最簡單的一種,它的輸入與輸出的匹配集成在芯片內部,基本不需要外部端接,從而使單板硬件設計更簡單、更簡潔。由于CML電路內部三極管同ECL一樣工作在非飽和狀態,邏輯翻轉速率極高,相比于LVDS要快很多;所以CML電平一般被用于高速SerDes鏈路(舉個栗子:光模塊接口SerDes總線)。

從標準規范來說,CML電平也沒有統一的國際標準。

——ECL,CML都沒有統一的國際標準,只有LVDS有國際標準,所以電平互連上需要特別注意檢查是否匹配。

1,CML基本電路結構

CML電路如下圖所示分為:本級輸入和本級輸出兩部分;

- 輸入電路是一對射極跟隨器后跟一個差分放大器:射極跟隨器起到隔離,增加驅動能力的作用,上拉的50Ω電阻是為了保證與前級輸出電路形成阻抗匹配;

- 當輸入為高電平時,即T3管為N端,T4管為P端,當P大于N時即輸入為高電平:當接收為高電平時T5導通、T6截止,16mA電流均從T5流過,此時CML輸出為低電平;

——當輸入為低時情況類似,所以CML輸入輸出存在倒相的關系。

- 輸出電路是一個差分對,如上圖“本級輸出”所示:該差分對的集電極電阻為50Ω,輸出信號的高低電平切換是通過共發射極差分對的開關控制的,差分對的發射極到地的恒流源典型值為16mA;

1, 當CML輸出直流耦合至50Ω上拉電阻負載時(如下左圖R1、R3和R2、R4同時上拉50Ω),所以輸出端差分對中的三極管T1和T2同時只能導通一個;

(1)首先進行靜態分析:由于T1、T2參數對稱,故16mA電流平均流過T1、T2,每個管流過8mA的電流,分到R1~R4四個電阻上,每個電阻流過的電流為4mA,所以直流耦合時的共模電壓為:Vc = Vcc – 4mA*50Ω = Vcc -0.2V;

(2)當有差模電壓輸入時:T1、T2只會導通一個(以T1導通為例),16mA電流由R1、R3一起提供,每個電阻提供8mA電流,因此單端擺幅為:Vswing = 8mA * 50Ω = 0.4V;

——當負載為50Ω上拉電阻時,輸出信號線上總共上拉電阻為50Ω//50Ω = 25Ω,所以計算導通三極管的集電極電阻上的壓降為:16mA*25Ω = 0.4V。

(3)如上可知共模電壓為:Vcc-0.2V,而差模電壓為:0.4V,所以CML單端輸出信號為以Vcc-0.2V為中心,擺幅為0.4V的信號,即單端信號擺幅為:Vcc~(Vcc-0.4V),其輸出波形如下左圖所示;

——在這種情況下差分輸出信號擺幅為800mV:差分電壓分別為-400mV和+400mV,擺幅為它們之和。

2, 當CML輸出交流耦合至50Ω上拉電阻負載時(如下左圖R1、R3和R2、R4同時上拉50Ω),所以同樣輸出端差分對中的三極管T1和T2同時只能導通一個;

(1)首先進行靜態分析:由于電容器的隔直作用,R3和R4不能向T1、T2提供直流電流,因此16mA電流平均流過R1、R2,每個電阻流過8mA的電流,所以交流耦合時的共模電壓為:Vc = Vcc – 8mA*50Ω = Vcc -0.4V;

(2)當有差模電壓輸入時(同直流耦合一樣):T1、T2只會導通一個(以T1導通為例),16mA電流由R1、R3一起提供,每個電阻提供8mA電流,因此單端擺幅為:Vswing = 8mA * 50Ω = 0.4V;

(3)如上可知共模電壓為:Vcc-0.4V,而差模電壓為:0.4V,所以CML單端輸出信號為以Vcc-0.4V為中心,擺幅為0.4V的信號,即單端信號擺幅為:(Vcc-0.2)~(Vcc-0.6V),其輸出波形如下右圖所示。

——在這種情況下差分輸出信號擺幅同樣是800mV:差分電壓分別為-400mV和+400mV,擺幅為它們之和。

2,CML電平分析和匹配

上一節我們已經從理論層面了解了CML電平的理想電壓值,如下圖所示為Maxim MAX3831器件的CML電平規格;除了有對單端、差分信號的具體定義之外,還有對阻抗進行了定義(精度15%),CML邏輯電路無需外部提供電路阻抗匹配(只需直連或AC耦合直連),這是因為CML輸入端內部電路已經做了終端并聯匹配:單端輸入50Ω上拉至Vcc;那么我們就知道差分信號線之間的阻抗為100Ω。所以在傳輸線設計時需保證:單端50Ω,差分100Ω的傳輸線阻抗設計(松耦合差分線)。

——終端并聯匹配是否必須要接至GND?單端50Ω時差分就必然是100Ω么(單端阻抗與差分阻抗是否有關系)?或則說什么情況下單端50Ω,差分會小于100Ω?關于這些問題,忘記的胖友們請繼續復習《從電感、電容到理想傳輸線》和《特殊的串擾-差分信號》相關章節,相信能給你個滿意的答案。

由于CML電平沒有任何標準,從而出現了很多供應商自行制定的規范,因此胖友們在使用CML電平時一定要仔細查閱芯片手冊(后續在《硬件開發流程基礎:詳細設計》相關專題中會介紹,如何保證單板上各器件之間的電平匹配)。

說到這里,突然想起一個事情來:我最早接觸高速串行鏈路時會將SerDes和CML/LVPECL/LVDS邏輯電平的概念搞混掉。我們在使用串行鏈路時,經常會用SerDes指代高速串行鏈路,但SerDes卻并非是邏輯電平的概念,比邏輯電平(純物理接口)的層次更高一些,因為它包含了物理層的部分協議。舉個栗子:你可以說這條SerDes鏈路是基于CML邏輯電平的。

4,CML電平特點

- CML電路輸出晶體管工作在放大區域(同ECL一樣),所以CML信號比采用飽和狀態操作的CMOS、LVDS信號擁有更快的開關速度;

- CML輸出電路中的恒流源具有較小的開關噪聲,信號的上升時間和下降時間小,因此CML理論極限速度可達10Gbit/s以上;如下圖所示為:LVPECL、LVDS和CML三種邏輯電路功耗及速度比較示意圖;

- 低功耗(差分輸出信號擺幅約為800mV,略低于LVPECL);

- 電路簡單,幾乎不需要外圍器件。

5,CML電路設計

CML電路設計規則,參考LVDS電路設計要求。如上很多針對高速鏈路的設計要求是通用的。

寫在最后

本章又介紹了兩個重量級的電平標準:LVDS和CML;加上之前的TTL/CMOS和LVPECL,這是本人接觸最多的邏輯電平;這些電平在數字電路中使用相對比較多。我記得很久之前,還接觸過HSTL,HCSL等等一些高速邏輯電平,還有用于DDR的SSTL。下一章我們做簡單的介紹。

-

CMOS

+關注

關注

58文章

5724瀏覽量

235697 -

MOS管

+關注

關注

108文章

2425瀏覽量

67087 -

電壓源

+關注

關注

1文章

410瀏覽量

32871 -

CML

+關注

關注

0文章

32瀏覽量

19353 -

LVDS電平

+關注

關注

0文章

3瀏覽量

1650

發布評論請先 登錄

相關推薦

LVDS、CML、LVPECL不同邏輯電平之間的互連(二)

淺談LVDS、CML、LVPECL三種差分邏輯電平之間的互連

LVDS用戶手冊-包含高速CML和信號調理內容

傳感器基礎知識:Sensors & Testing Technology 緒論

差分邏輯電平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等

如何在LVPECL、VML、CML、LVDS和子LVDS接口之間轉換

LVDS|PECL|CML

LVDS和CML與LVPECL的同種差分邏輯電平之間的互連教程

詳解信號邏輯電平標準:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML資料下載

獲得連接:LVPECL、VML、CML、LVDS 與子 LVDS 之間的接口連接

如何區分Java中的&amp;和&amp;&amp;

LVDS&CML電平設計基礎知識

LVDS&CML電平設計基礎知識

評論