公眾號:高速先生

作者:黃剛

大家可能已經習慣了高速先生善于解決各種高速信號和電源信號的疑難雜癥,讓很多從事EMC行業的粉絲們感覺格格不入。別急,今天就show一下我們在EMC方面的積累案例哈!

高速先生真的不只是專注于高速信號哈,其實我們也持續在研究EMC方面的理論,同時也積累了很多debug的案例和PCB設計經驗,最近也收到很多粉絲要求,讓我們分享一些EMC的設計案例,就今天,高速先生就給大家分享這么一個簡單但是卻很隱蔽的EMC設計問題。

案例來自一家和我們深度合作很多年的戰略客戶,我們在高速上合作比較的多,其實這個項目本身也是一個高速的項目,板上最高速的是25G的光模塊信號鏈路。這個項目由我們的PCB工程師設計并進行仿真,當然仿真的是25G信號本身的通道性能,在確定仿真pass之后,設計工程師按照我們給出的建議去修改并制板加工和焊接,客戶拿到完成的板卡之后首先進行25G光模塊誤碼率的測試,測試發現沒有問題,雖然我們的仿真是pass的,但是每一次客戶真正調試成功我們才能放心。

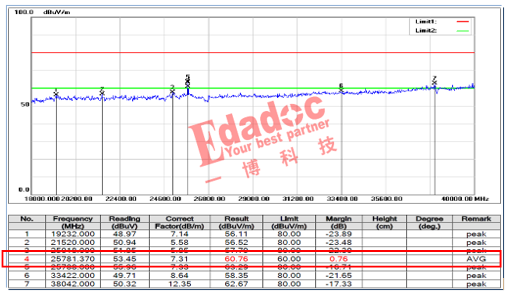

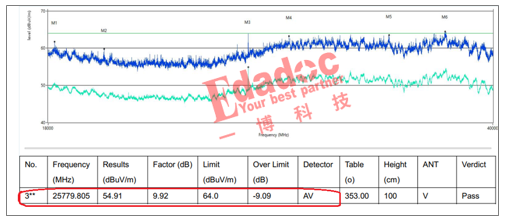

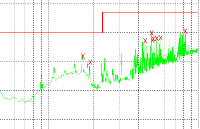

當我們認為又是一個對于高速先生很常規的仿真設計項目時,客戶居然拿這塊板去做了一個之前不需要做的測試,那就是EMC的輻射測試!而且更打擊的是,在進行3M的遠場測試時,發現在25G的頻點輻射還稍有超標,要求是60dBuV/m,我們測試多了一丟丟,測試項為FCC part15 Class A,測試結果是下面這樣的:

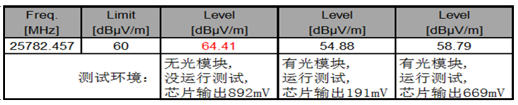

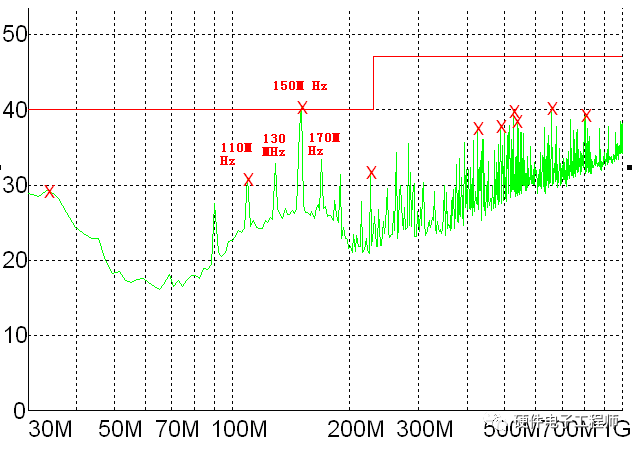

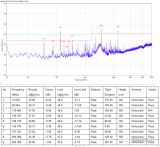

在25G的頻點輻射超標,目標肯定直接指向了光模塊的設計上,我們知道輻射的能量正相關于光模塊的輸出幅度,因此我們為了更好的判斷光模塊輸出對輻射指標的影響,我們建議客戶調節下FPGA的輸出幅度(當前結果是輸出幅度為892mV情況下測試),看看光模塊的接收幅度變化對輻射的影響,按照我們的建議,客戶進行了測試,列表如下:

通過測試結果傳遞給我們兩個重要的信息:

1、的確是光模塊鏈路導致的輻射影響;

2、降低FPGA輸出幅度會減小輻射噪聲,并成功通過EMC測試指標;

3、但是降低FPGA幅度可能會對信號質量產生影響。

當我們明確了光模塊導致的影響后,那我們就看看PCB設計上還有什么可以優化的點,我們打開PCB文件,聚焦到該光模塊區域的設計里面,發現了很重要的一個點:

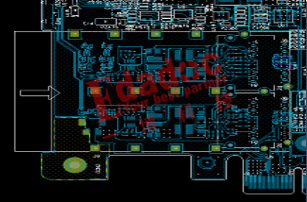

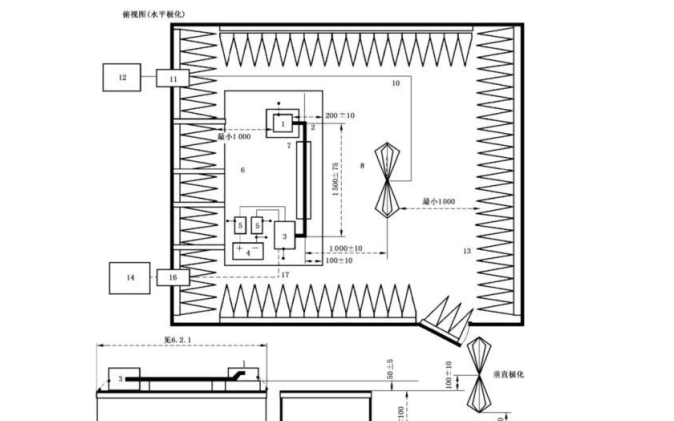

在TOP層,也就是光模塊的焊接層,我們的機殼地是很好的連接起來的,如下所示:

于是我們再看看針腳那邊的BOTTOM層,發現機殼地并沒有接上,而是鋪的是常規的數字地,高速先生咨詢了設計工程師,他表示鋪數字地可以更好的屏蔽板內的光模塊信號,提供隔絕串擾和回流的作用,沒有往EMC輻射這方面進行更多的權衡。高速先生評估之后,認為這個地方的鋪數字地對信號的串擾和回流本身其實幫助不大,因為走線沒有參考到這一層,相反接上機殼地的話,是更有可能對輻射的屏蔽產生正面的作用,因為光模塊的外殼和針腳都連接到BOTTOM層的位置去了。

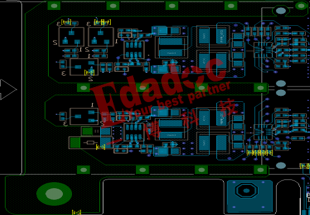

于是我們和客戶商量之后,決定快速的再加工一版驗證下,包括高速信號本身的大部分設計都不做改動,只是把BOTTOM這個機殼地像TOP層這樣連接起來,如下所示:

很快板子重新完成了,客戶再進行測試后給出了大家都滿意的答案,在原有的FPGA輸出幅度的情況下再進行EMC測試,成功將這個頻點的輻射壓低了, 滿足了輻射的指標,而高速信號通道本身的測試也并沒有問題,這下客戶終于可以安心的結項了!

最后客戶也很感慨的表示,在沒測試輻射這個指標之前,還一直覺得機殼地的設計不會有那么重要的影響,通過這個案例后,看能不能對重視EMC輻射影響的粉絲們提供一些有意義的PCB設計思路哈!

審核編輯:湯梓紅

-

輻射

+關注

關注

1文章

598瀏覽量

36335 -

emc

+關注

關注

170文章

3914瀏覽量

183123 -

光模塊

+關注

關注

77文章

1261瀏覽量

58990 -

機殼地

+關注

關注

0文章

3瀏覽量

7530

發布評論請先 登錄

相關推薦

某產品EMC輻射騷擾測試超標案例分析

HDMI輻射超標如何整改

【EMC家園】產品EMC輻射發射超標原因有哪些?

EMC輻射超標,內部時鐘頻率超標怎么解決?

造成EMC輻射超標原因有哪些(精彩案例分析)

3225貼片晶振EMC輻射超標工作建議和分析

某單板TVS接地不當造成輻射騷擾超標問題分析

時鐘輻射超標怎么解決?

EMC整改如何解決時鐘輻射超標問題

EMC輻射超標案例分析

EMC輻射超標案例分析

評論