摘要:在后摩爾時(shí)代,集成電路設(shè)計(jì)理念正向Chiplet架構(gòu)轉(zhuǎn)變。本文從D2D接口IP設(shè)計(jì),D2D封裝和D2D測試三個方面介紹了Chiplet D2D的解決方案,并給出了采用此解決方案的XSR 112G D2D的測試結(jié)果。

1.后摩爾時(shí)代向Chiplet的戰(zhàn)略轉(zhuǎn)變

當(dāng)前摩爾定律逐步趨向物理極限,半導(dǎo)體行業(yè)正在發(fā)生重大的戰(zhàn)略轉(zhuǎn)變。基于Chiplet架構(gòu)的芯片設(shè)計(jì)理念逐漸成為行業(yè)主流。這一戰(zhàn)略轉(zhuǎn)變的驅(qū)動因素主要有以下幾種:

1)單芯片的尺寸變得太大,無法制造;

2)充分利用已有KGD(Known Good Die)芯片實(shí)現(xiàn)復(fù)雜功能芯片,可以減少設(shè)計(jì)周期和成本,并提高良率。

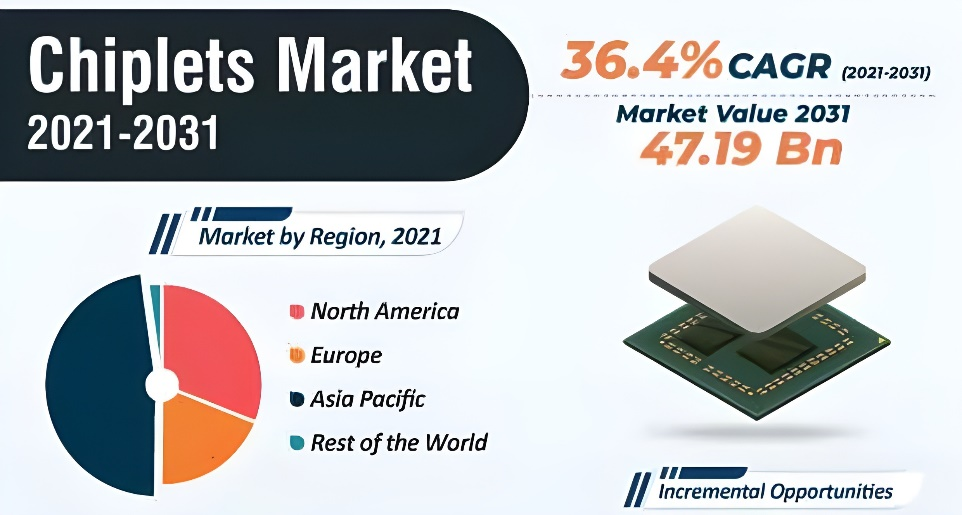

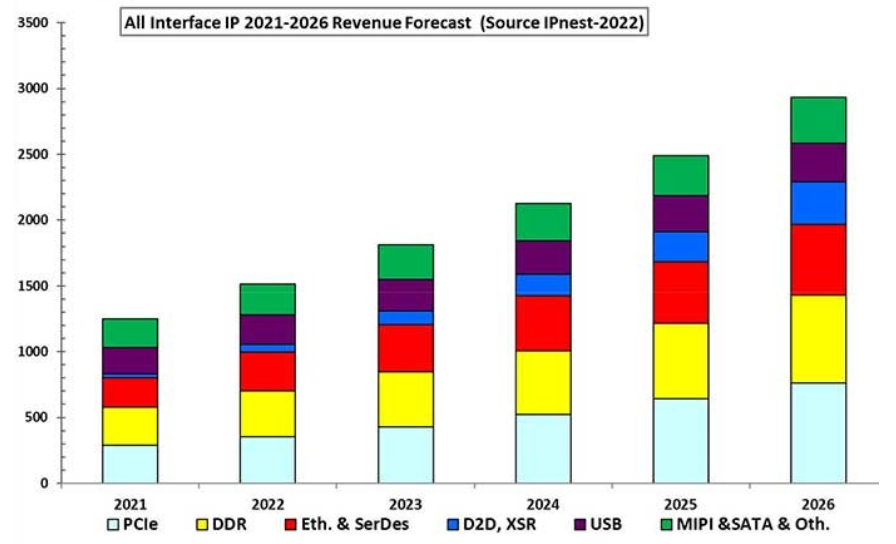

在這些驅(qū)動因素下,整個Chiplet行業(yè)在2031年有望達(dá)到471.9億美元[1],如圖1所示,Chiplet市場在2021~2031十年期年復(fù)合增長率保持36.4%;其中實(shí)現(xiàn)Die to Die(D2D)互連的接口IP市場在2026達(dá)到3.24億美元[2],D2D IP市場在2021~2026五年期年復(fù)合增長率高達(dá)50%,如下圖2所示。

圖1 Chiplet市場

圖2 D2D IP市場趨勢

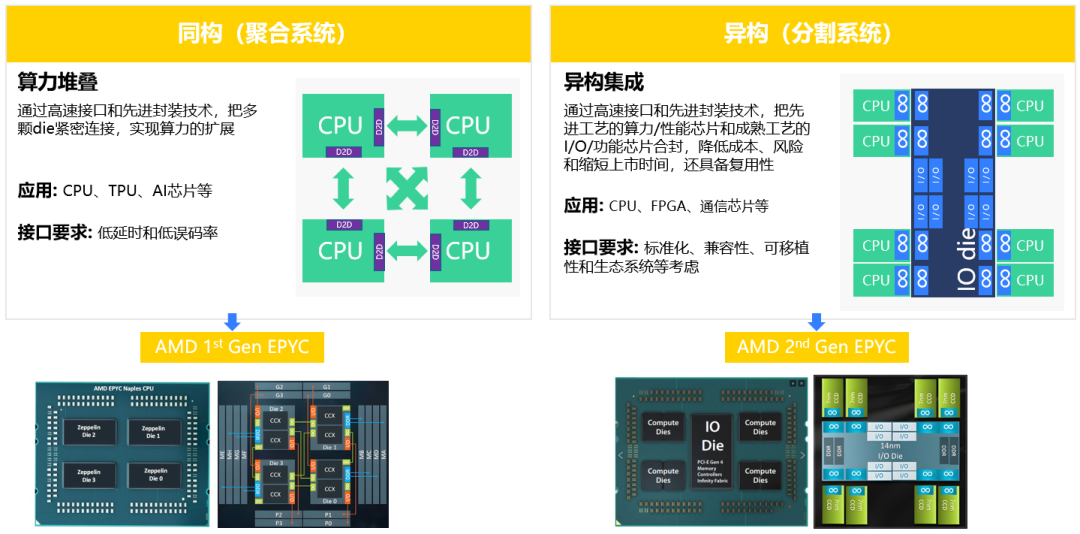

Chiplet應(yīng)用場景主要分兩種,第一種是將同工藝大芯片分割成多個小芯片,然后通過接口IP互連在一起實(shí)現(xiàn)算力堆疊;第二種是將不同工藝不同功能的芯片通過接口IP互連并封裝在一起實(shí)現(xiàn)異構(gòu)集成,如圖3所示。算力堆疊主要應(yīng)用于CPU、TPU和AI芯片等,對接口IP的要求是低延遲和低誤碼率,通常采用并行接口IP。異構(gòu)集成,主要應(yīng)用于CPU、FPGA和通信芯片等,對接口IP的要求是標(biāo)準(zhǔn)化,兼容性,可移植性和生態(tài)系統(tǒng)等,通常采用串行接口IP。

圖3 典型應(yīng)用場景

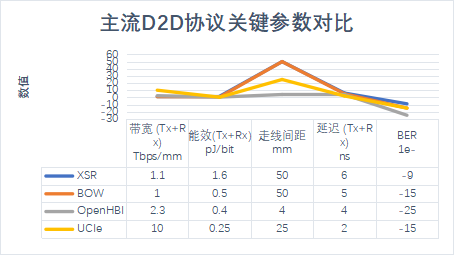

為了便于組裝不同供應(yīng)商開發(fā)的芯粒,需要標(biāo)準(zhǔn)化的芯粒間互連標(biāo)準(zhǔn),行業(yè)聯(lián)盟已共同定義出多種芯粒互連標(biāo)準(zhǔn),如XSR,BoW,OpenHBI,UCIe等。它們的主要性能指標(biāo)如圖4所示。其中,XSR采用差分串行結(jié)構(gòu),目前最高速率達(dá)112Gbps,可用于異構(gòu)集成連接IO die;后3種采用單端并行結(jié)構(gòu),目前最高速率是UCIe的32Gbps, 同時(shí)它還定義了完整的協(xié)議層,繼承了CXL和PCIe的生態(tài)優(yōu)勢,可用于算力堆疊中計(jì)算IP間的互連。

圖4 主流D2D的關(guān)鍵指標(biāo)

完整的D2D解決方案包括:D2D接口IP設(shè)計(jì)、D2D封裝設(shè)計(jì)和D2D測試,下面分別做詳細(xì)介紹。

2.D2D接口IP設(shè)計(jì)解決方案

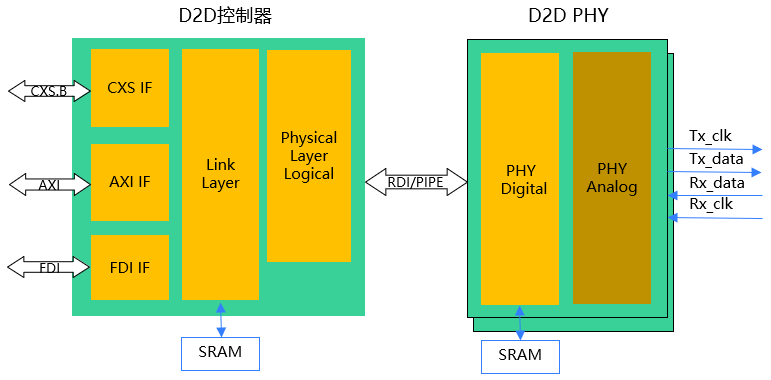

D2D接口IP由物理層(PHY)和控制器組成,如下圖5所示。物理層PHY是封裝介質(zhì)的電氣接口。從分層結(jié)構(gòu)上分為模擬PHY和數(shù)字PHY,模擬PHY包括電氣AFE(發(fā)射器、接收器)以及邊帶信道,可實(shí)現(xiàn)兩個晶粒之間的參數(shù)交換和協(xié)商。數(shù)字PHY包括鏈路初始化、訓(xùn)練和校準(zhǔn)算法以及測試和修復(fù)功能。從接口類型上分并行接口和串行接口。

控制器由鏈路層(Link layer)和邏輯物理層(Physical Layer Logical)。鏈路層負(fù)責(zé)上層協(xié)議接口適配,協(xié)議仲裁和協(xié)商,以及基于 CRC,可選的FEC(Forward Error Correction)和重傳機(jī)制來確保鏈路可靠地傳輸數(shù)據(jù);邏輯物理層負(fù)責(zé)鏈路訓(xùn)練和管理功能以及具體的PHY適配(比如加擾,解擾,塊對齊,OS插入和提取等)。在鏈路初始化時(shí),邏輯物理層會等待 PHY 完成鏈路初始化,通過鏈路狀態(tài)機(jī)進(jìn)入工作模式。鏈路層會通過協(xié)商確定使用哪個協(xié)議(如果實(shí)施了多個協(xié)議)。控制器向上支持CXS、AXI、FDI(Filt aware D2D interface)接口來支持PCIe、CXL、UCIe以及SOC和RAW協(xié)議層;向下兼容RDI(Raw D2D interface)和PIPE接口來適配不同的物理電氣層[3][4][5]。

下面分別介紹一下并口和串口的D2D PHY架構(gòu)。

圖5 D2D分層架構(gòu)

2.1 并口D2D PHY架構(gòu)

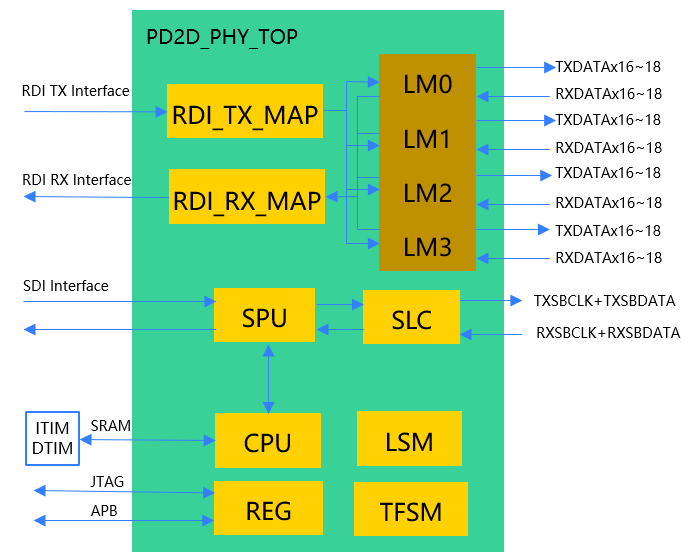

為了滿足低延遲,高能效,低誤碼率要求,物理層接口采用單端并口傳輸,使用2.5D封裝形式。并口D2D物理層結(jié)構(gòu)如圖6所示:

圖6 并口D2D PHY系統(tǒng)框架

并口物理層模擬部分包括4個LM(Lane module),每個LM數(shù)據(jù)位寬為單向16bit,共64bit。可以根據(jù)所需帶寬靈活配置LM數(shù)目。每個LM還可以配置1~2個Slicer用于Filt Header或CRC校驗(yàn)。每Lane具備高精度和高解析度自校準(zhǔn)延遲線,RX線性連續(xù)時(shí)間均衡器(CTLE)和DFE均衡器以實(shí)現(xiàn)高速性能,并根據(jù)走線長度可關(guān)閉DFE均衡器,以降低功耗。

并口物理層數(shù)字部分包括的功能塊有RDI_TX/RX_MAP實(shí)現(xiàn)RDI接口到LM的映射;SPU(Sideband Process Unit)/TFSM(Train FSM)/LSM(Link SM)實(shí)現(xiàn)PHY啟動,Lane修復(fù)/反轉(zhuǎn),TX/RX訓(xùn)練,VREF訓(xùn)練,眼圖訓(xùn)練,自適應(yīng),鏈路狀態(tài)管理,鏈路雙方配置等功能。

芯耀輝實(shí)現(xiàn)的并口物理層采用DDR模式傳輸數(shù)據(jù),數(shù)據(jù)率為16Gbps,符合UCIe和CCITA發(fā)布的《小芯片接口總線技術(shù)要求》標(biāo)準(zhǔn);使用Forward clock模式簡化接收端設(shè)計(jì),可以減小延遲,降低功耗;延遲時(shí)間從本端FDI到對端FDI小于2ns;能效0.5~1pJ/bit。

2.2串口D2D PHY架構(gòu)

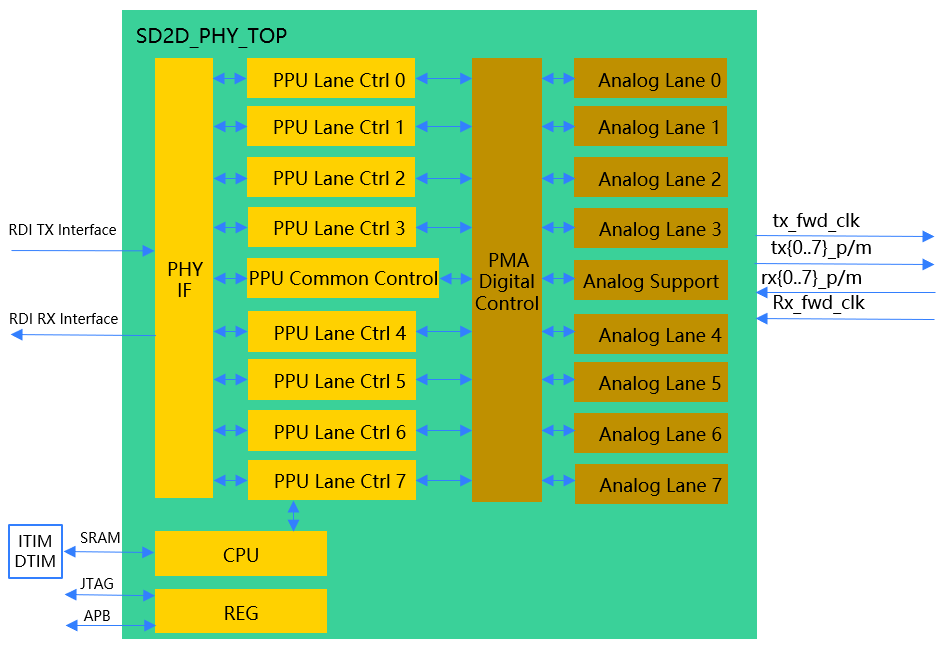

為了滿足高帶寬,較長距傳輸,較低封裝成本的要求,物理層接口采用差分串口傳輸,使用2D substrate封裝形式。串口D2D物理層結(jié)構(gòu)如下圖7所示:

圖7 串口D2D PHY架構(gòu)

串口物理層模擬部分包括8通道Analog Lane,每通道由TX和RX組成,可實(shí)現(xiàn)雙向8通道全雙工差分信號傳輸,兼容NRZ和PAM4信令,數(shù)據(jù)率覆蓋2.5~112Gbps[6]。為適應(yīng)較差的信道,TX采用3 Taps FFE均衡器,RX采用線性均衡器。為了優(yōu)化延遲,時(shí)鐘架構(gòu)可采用Forward clock架構(gòu)。為了優(yōu)化功耗,每個通道可獨(dú)立開關(guān),獨(dú)立運(yùn)行。

串口物理層數(shù)字部分包括PMA Digital Control和PHY處理單元(PPU)。主要實(shí)現(xiàn)PHY上下電時(shí)序控制;上電時(shí)TX/RX校準(zhǔn)、自適應(yīng)算法及順序控制;正常運(yùn)行時(shí),實(shí)時(shí)自適應(yīng)校準(zhǔn);內(nèi)建測試邏輯控制等功能。

芯耀輝實(shí)現(xiàn)的串口物理層兼容CEI-112G-XSR協(xié)議,最高速率達(dá)112Gbps,可均衡通道損耗達(dá)-10dB,帶寬線密度約1Tbps/mm,能效1.5pJ/bit,延遲時(shí)間小于6ns,誤碼率小于1e-15。

3.D2D封裝方案

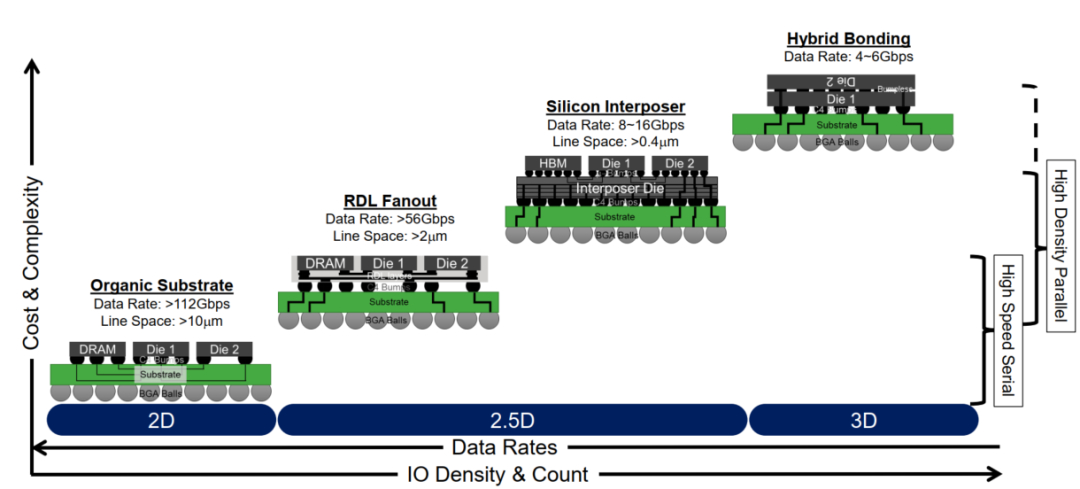

適合D2D的封裝類型包括傳統(tǒng)的2D有機(jī)基板(Substrate),先進(jìn)2.5D封裝(RDL Fanout和Silicon Interposer)及3D封裝(Hybrid Bonding)。具體選用那種封裝類型,需綜合考慮IO數(shù)量,IO密度,數(shù)據(jù)率,成本,復(fù)雜度和接口類型等因素,如圖8所示[7]。通常對于高速串行接口,數(shù)據(jù)率越高,IO數(shù)量越少,IO密度越低,復(fù)雜度和成本也越低,建議采用2D或者RDL Fanout 2.5D封裝類型。對于高密度并行接口,數(shù)據(jù)率越低,IO數(shù)量越多,IO密度越高,復(fù)雜度和成本也越高,建議采用2.5D或者3D封裝類型。

圖8 D2D封裝類型選擇

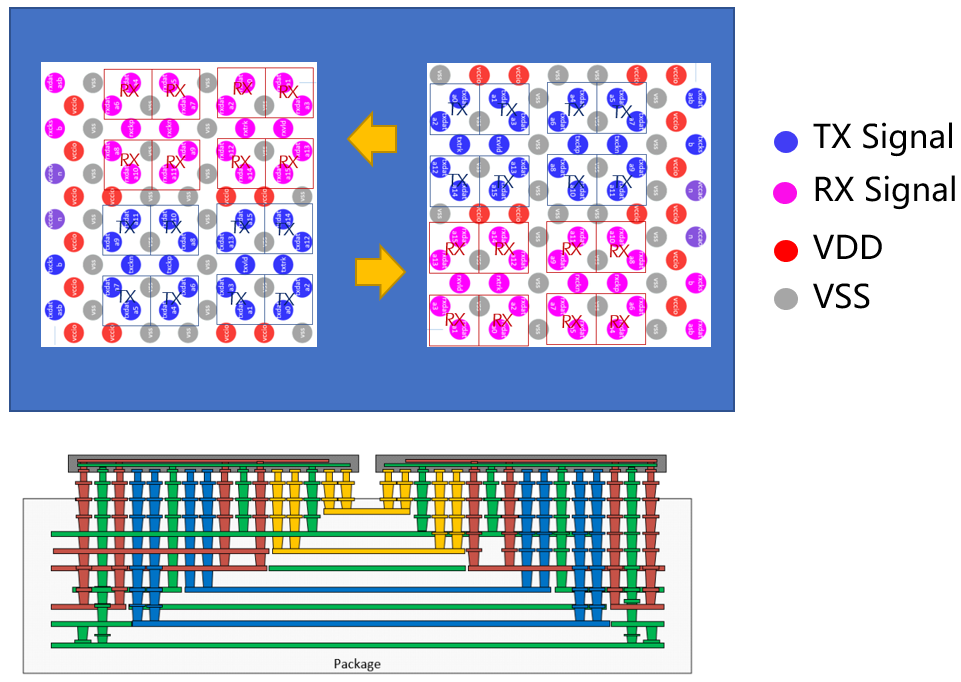

考慮到出Pin密度,電源Drop,信號完整性,減小基板層數(shù),降低成本等因素。Bump map和互連走線采用如圖9所示結(jié)構(gòu)[2]。圖中TX信號bump和RX信號bump分開單獨(dú)放一起,可以方便對端Die的互連,減小走線間Cross talk;兩個Die之間bump采用相隔近的與相隔近的互連,相隔遠(yuǎn)的與相隔遠(yuǎn)的互連,可以減少基板疊層,減小信號走線間交疊,從而減少成本,提高信號完整性。但這樣會造成線與線間延遲時(shí)間的輕微差別,可以通過Die內(nèi)Deskew功能去除。從信號完整性角度來看,還需要考慮Bump阻抗不連續(xù),Via阻抗不連續(xù),走線阻抗不連續(xù)和噪聲耦合等問題。

圖9 Bump map方案

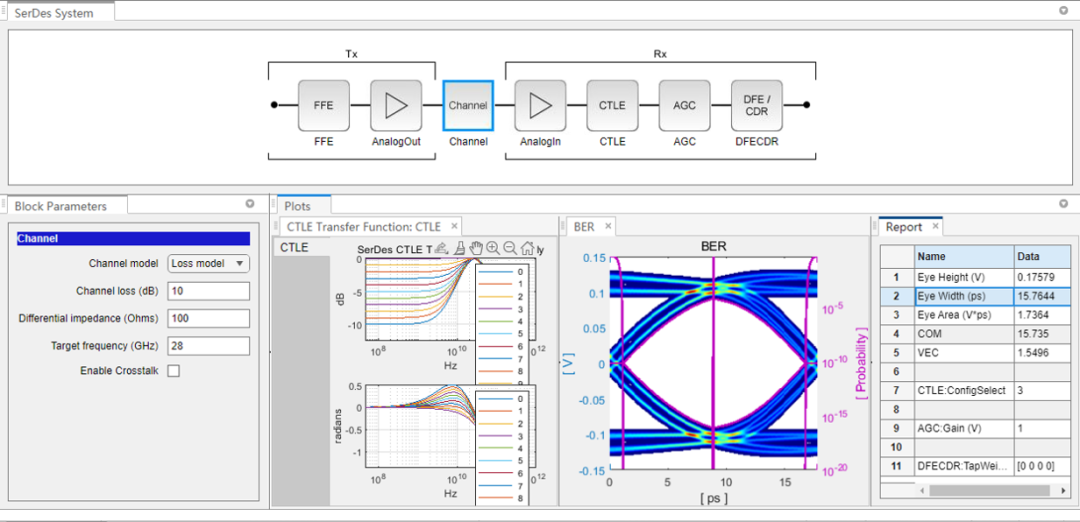

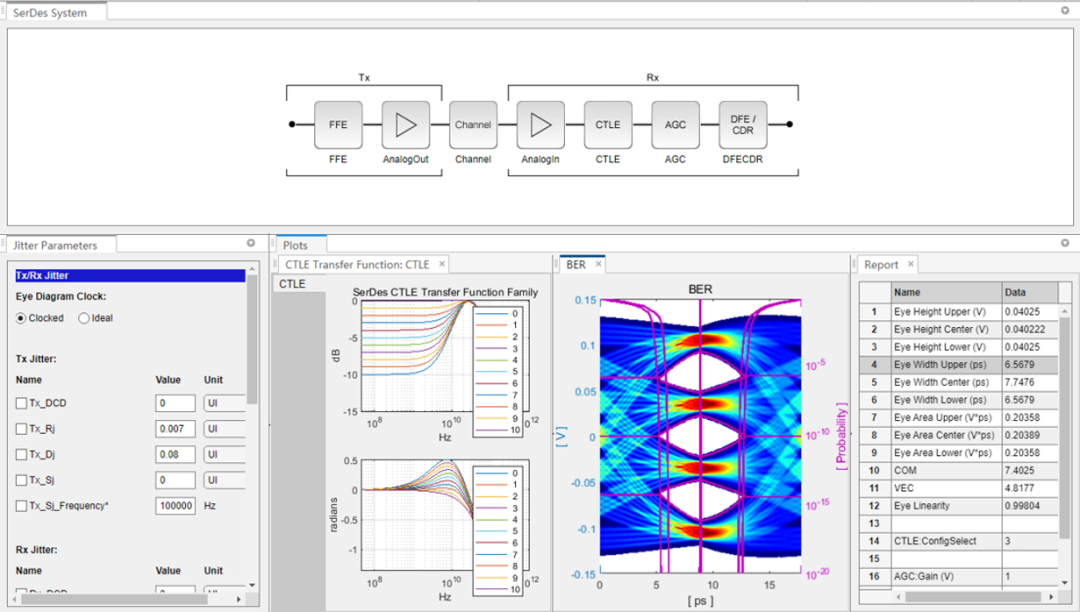

封裝設(shè)計(jì)好后,需要抽取S參數(shù),并利用IBIS-AMI模型驗(yàn)證信號質(zhì)量。能建模IBIS-AMI并驗(yàn)證走線S參數(shù)的工具有很多,它們中大部分都提供了自動化IBIS-AMI建模流程,可以基于圖形界面設(shè)計(jì)[8]。如圖10和圖11所示,用戶可以使用軟件內(nèi)建的常用算法模型,來快速對TX的FFE去加重預(yù)加重均衡和模擬輸出(AnalogOut)以及RX的模擬輸入(AnalogIn),CTLE連續(xù)時(shí)間線性均衡,AGC自動增益放大, DFE自適應(yīng)判決反饋均衡和CDR時(shí)鐘恢復(fù)等進(jìn)行建模,既可設(shè)置為NRZ模式也可設(shè)置為PAM4模式,而且內(nèi)建的Channel模型可以很方便調(diào)用Touchstone格式的通道S參數(shù)。

圖10中,Channel調(diào)用的通道S參數(shù)為-10dB@28GHz;TX設(shè)置為NRZ模式,數(shù)據(jù)率為56Gbps,擺幅為500mV,輸入信號為PRBS31,F(xiàn)FE均衡不使能;RX 設(shè)置CTLE gain-boost從0dB到-10dB,AGC增益設(shè)置為1,DFE不使能,CDR使能。仿真得到的眼高175mV,眼寬15.76ps,COM為15.7dB。圖11中,將設(shè)置改為PAM4模式,數(shù)據(jù)率為112Gbps,輸入信號為QPRBS13,其它不變的情況下。仿真得到的眼圖的三個眼高基本一致為40mV,眼的線性度RLM為99.8%。

圖10

用IBIS-AMI模型進(jìn)行NRZ信號通道分析

圖11

用IBIS-AMI模型進(jìn)行PAM4信號通道分析

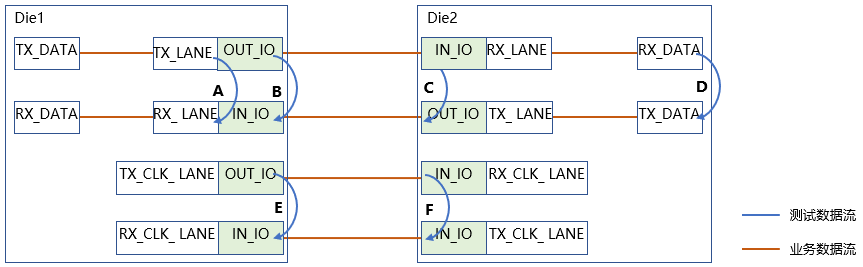

4.D2D測試方案

以串口D2D為例。為了全面測試和debug數(shù)據(jù)鏈路,D2D接口IP在設(shè)計(jì)時(shí),需考慮全面的環(huán)回測試路徑,如圖12所示。數(shù)據(jù)通路測試路徑包括:數(shù)字側(cè)近端環(huán)回路徑A:本端數(shù)字部分內(nèi)環(huán)測試;模擬側(cè)近端環(huán)回路徑B:本端模擬部分內(nèi)環(huán)測試;模擬側(cè)遠(yuǎn)端環(huán)回路徑C:對端模擬部分外環(huán)測試;數(shù)字側(cè)遠(yuǎn)端環(huán)回路徑D:對端數(shù)字部分外環(huán)測試。時(shí)鐘通路測試路徑包括:時(shí)鐘近端環(huán)回路徑E:本端發(fā)送時(shí)鐘至接收時(shí)鐘的環(huán)回測試;時(shí)鐘遠(yuǎn)端環(huán)回路徑F:對端接收時(shí)鐘至發(fā)送時(shí)鐘的環(huán)回測試。

圖12 環(huán)回測試模式

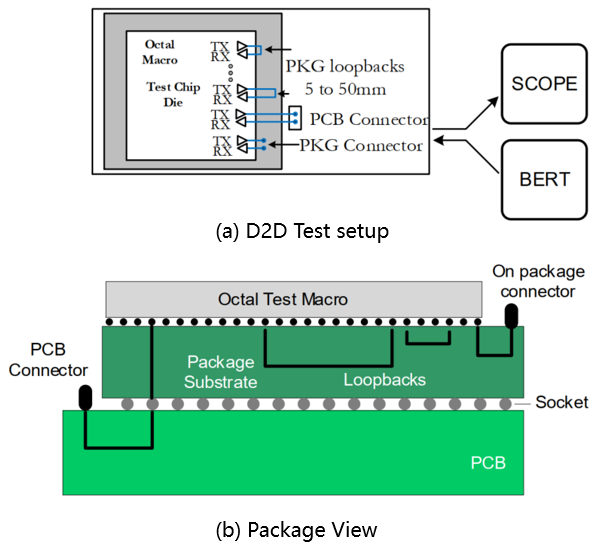

由于D2D高速引腳一般封裝在Package內(nèi),不引出。這樣對D2D IP的測試造成了一定的不方便。因此,測試方案和Package設(shè)計(jì)都需要特殊考慮。如圖13所示[9][10],測試需要2個Die(Octal Macro)實(shí)現(xiàn)TX到RX的環(huán)回測試。為了驗(yàn)證D2D IP能過不同的通道損耗,通道損耗設(shè)計(jì)為1dB~10dB@28GHz。為了真實(shí)測試出D2D IP的性能,需要對從PCB連接器處到封裝基板的走線做去嵌處理。

圖13

D2D test setup and package view

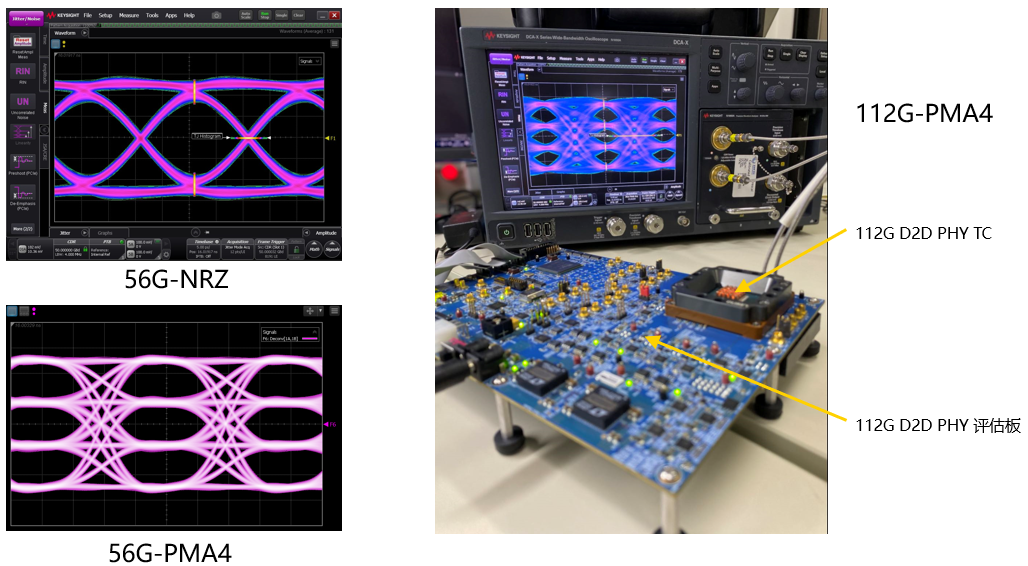

采用以上測試方案,通道損耗為-10dB@28GHz時(shí),芯耀輝設(shè)計(jì)的112G 串口D2D 樣片TX輸出的測試結(jié)果如圖14所示。圖中56G-NRZ測試采用PRBS31碼型,眼高為363mV,Rj為345fs(rms);56G-PAM4測試采用QPRBS13碼型,三個眼高從上到下分別為224.6mV,235.6mV,229.0mV,RLM=97.7%;112G-PAM4測試采用QPRBS13碼型,三個眼高從上到下分別為為99mV,109.2mV,97mV,RLM=95.3%。測試結(jié)果滿足CEI-112G-XSR協(xié)議要求。

圖14XSR D2D TX測試結(jié)果

5.結(jié)束語

多晶粒Chiplet已成為芯片設(shè)計(jì)行業(yè)主流系統(tǒng)方案,D2D接口規(guī)范為設(shè)計(jì)人員帶來了極具競爭力的性能優(yōu)勢,包括高能效 (pJ/b),高帶寬線密度 (Tbps/mm) 和低延遲 (ns),支持主流IO協(xié)議以及任何用戶定義的協(xié)議,支持多種封裝類型。本文從接口IP設(shè)計(jì)到封裝設(shè)計(jì)再到測試方案,詳細(xì)介紹了Chiplet D2D解決方案。參照此方案可輕松實(shí)現(xiàn)多晶粒系統(tǒng)互連。

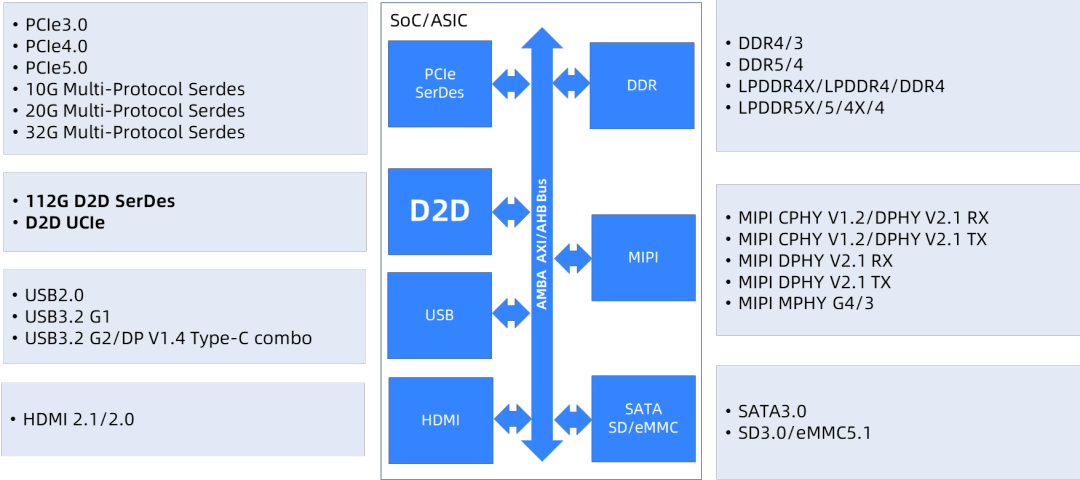

2022年4月,芯耀輝作為首批會員加入了UCIe組織,推出支持UCIe協(xié)議且兼容多樣化D2D和C2C場景的“并口D2D PHY IP”以及高能效比和高寬帶利用率的“串口112G D2D SerDes PHY IP”的完整D2D解決方案,如圖15所示。同年10月,芯耀輝承接了國家科技部重點(diǎn)研發(fā)專項(xiàng),作為國家隊(duì)成員著力推動國內(nèi)Chiplet標(biāo)準(zhǔn)CCITA的產(chǎn)業(yè)化落地。公司一直專注于高速接口IP領(lǐng)域,積累了豐富的經(jīng)驗(yàn)和技術(shù)能力,已經(jīng)為客戶提供了5G、數(shù)據(jù)中心、網(wǎng)絡(luò)交換機(jī)等相關(guān)芯片IP產(chǎn)品,率先實(shí)現(xiàn)了市場客戶的量產(chǎn)。隨著產(chǎn)業(yè)進(jìn)一步的發(fā)展,以及相關(guān)的下游的封裝等一些技術(shù)的成熟,Chiplet在國內(nèi)的發(fā)展前景可期。

圖15 芯耀輝完整IP解決方案

-

封裝

+關(guān)注

關(guān)注

128文章

8474瀏覽量

144756 -

IP

+關(guān)注

關(guān)注

5文章

1779瀏覽量

151267 -

chiplet

+關(guān)注

關(guān)注

6文章

452瀏覽量

12859

原文標(biāo)題:特刊收錄丨后摩爾時(shí)代的Chiplet D2D解決方案

文章出處:【微信號:AkroStar-Tech,微信公眾號:芯耀輝科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

基于瑞薩電子RA8D1 MCU的USB和I2S數(shù)字音頻應(yīng)用解決方案

淺談Chiplet與先進(jìn)封裝

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

FA10-220D09E2D4 FA10-220D09E2D4

2.5D集成電路的Chiplet布局設(shè)計(jì)

廣電計(jì)量受邀參加后摩爾器件研討會 攜半導(dǎo)體綜合技術(shù)解決方案亮相

Alpahwave Semi推出全球首個64Gbps UCIe D2D互聯(lián)IP子系統(tǒng)

對話郝沁汾:牽頭制定中國與IEEE Chiplet技術(shù)標(biāo)準(zhǔn),終極目標(biāo)“讓天下沒有難設(shè)計(jì)的芯片”

高帶寬Chiplet互連的技術(shù)、挑戰(zhàn)與解決方案

回顧:奇異摩爾@ ISCAS 2024 :聚焦互聯(lián)技術(shù)與創(chuàng)新實(shí)踐

UCIe規(guī)范引領(lǐng)Chiplet技術(shù)革新,新思科技發(fā)布40G UCIe IP解決方案

智原科技與奇異摩爾2.5D封裝平臺量產(chǎn)

創(chuàng)新型Chiplet異構(gòu)集成模式,為不同場景提供低成本、高靈活解決方案

剖析 Chiplet 時(shí)代的布局規(guī)劃演進(jìn)

評論