數據路徑和時鐘路徑

reg2reg路徑約束的對象是源寄存器(時序路徑的起點)和目的寄存器(時序路徑的終點)都在FPGA內部的路徑。如圖1所示,FPGA內部圈起來的部分是從一個寄存器到另一個寄存器的數據路徑,他們共用一個時鐘(當然也有不共用一個時鐘的reg2reg路徑,這種路徑的分析會復雜一些,本節我們只探討同時鐘源的時序路徑)。

對于reg2reg路徑,我們只要告訴FPGA的編譯工具它們的時鐘頻率(或時鐘周期),那么時序設計工具通常就“心領神會”的將時鐘周期、建立時間和保持時間等相關參數代入特定的公式后,計算出這條reg2reg的路徑允許的延時范圍,并以此為目標進行布局布線。

圖1 reg2reg路徑模型

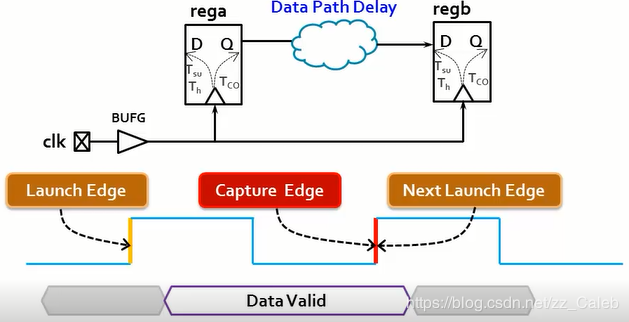

如圖2所示,reg2reg模型中的數據路徑(datapath)和時鐘路徑(clock path)清晰明了。所謂數據路徑,就是數據在整個傳輸起點到傳輸終點所經過的路徑;所謂時鐘路徑,則是指時鐘從源端到達源寄存器和目的寄存器的路徑。相比于數據路徑的“華山一條路”,時鐘路徑通常由時鐘源到源寄存器和時鐘源到目的寄存器兩條路徑組成。

圖2 reg2reg的數據路徑和時鐘路徑

數據到達路徑和數據需求路徑

如圖3所示,為了便于后續的時序余量分析和計算,我們提出了數據到達路徑(data arrival path)和數據需求路徑(data required path)的概念。數據到達路徑,是指數據在兩個寄存器間傳輸的實際路徑,由此路徑可以算出數據在兩個寄存器間傳輸的實際時間;數據需求路徑,則是指為了確保穩定、可靠且有效的傳輸(即滿足相應的建立時間和保持時間要求),數據在兩個寄存器間傳輸的理論所需時間的計算路徑。

從圖2.11的示意可以看到,兩條路徑的傳輸起點都是時鐘源,傳輸終點都是目標寄存器。數據到達路徑包括了數據路徑和一條時鐘路徑(時鐘源到源寄存器),這兩條路徑的總延時就是數據到達時間。而數據需求路徑則只有一條從時鐘源到目的寄存器的時鐘路徑,在進行數據需求時間計算時,應結合寄存器的建立時間和保持時間進行計算。

圖3 reg2reg的數據到達路徑和數據需求路徑

-

FPGA

+關注

關注

1646文章

22059瀏覽量

619227 -

寄存器

+關注

關注

31文章

5437瀏覽量

124732 -

時序

+關注

關注

5文章

399瀏覽量

38052 -

時鐘源

+關注

關注

0文章

98瀏覽量

16346

發布評論請先 登錄

FPGA的約束、時序分析的概念詳解

評論