同步電路

即電路中的所有受時鐘控制的單元,全部由一個統一的全局時鐘控制:

- 觸發器(Flip Flop)

- 寄存器(Register)

同步電路優點:

缺點:

電路里面所有的觸發器都由同一個時鐘驅動,所以必須構建時鐘樹、時鐘網絡,因此時鐘到達哥哥觸發器的時間不一樣,則會引入時鐘偏斜和時鐘抖動問題:

- 時鐘偏斜( Clock Skew )

- 時鐘抖動(Clock Jitter )

- 時鐘樹綜合,需要加入大量的延遲單元,使得電路的面積和功耗大大增加

全局異步電路

全局異步設計跟同步設計最大的不同就是它的電路中的數據傳輸可以在任何時候發生,電路中沒有一個全局的或局部的控制時鐘。

異步電路優點:

異步電路缺點:

同步異步時鐘,指時鐘源是不是同一個,假設是同一個PLL出來的,就能看成是同步時鐘,不同PLL下即使是同頻也是異步時鐘

在一個性想的全局時鐘控制下,只要電路的各個功能壞節都買現了時序收斂,整個電路就可以可靠工作了。由于 EDA 工具的廣泛支持,采用同步電路設計的方法是目前ASIC 和 SoC 設計的基本要求。但是常大規模 ASIC 和 SoC 芯片中都采用了全局異步、局部同步的方法。因此,在設計中必須要注意 異步信號與同步電路的交互問題 。

在不同時鐘域間,如何安全傳遞信號

跨時鐘域電路主要分為以下幾種:

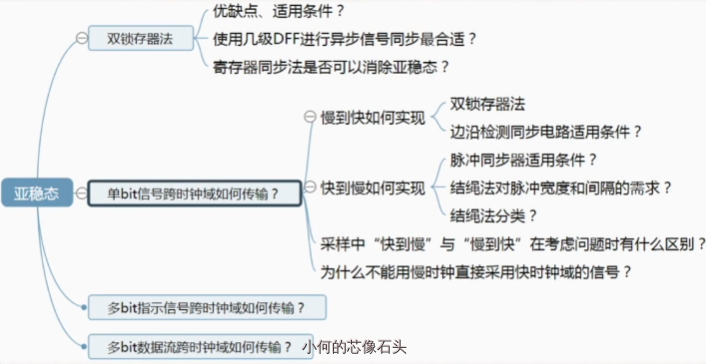

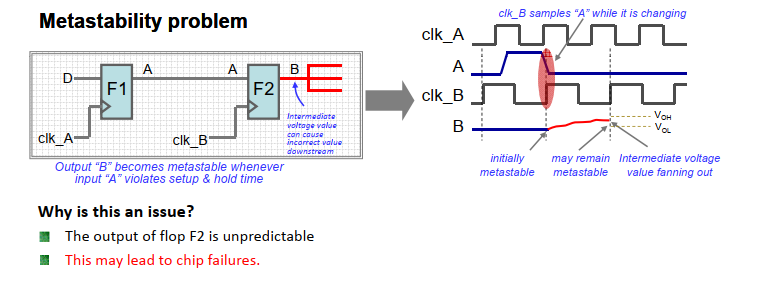

亞穩態相關概念和原理

- 亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。

- 亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。

- 在這個期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。

- 亞穩態不能從根本上消除,但可以通過采取一定的措施使其對電路造成的影響降低。

亞穩態影響衡量指標MTBF(Mean Time Between Failure),MTBF越大,亞穩態影響越小:

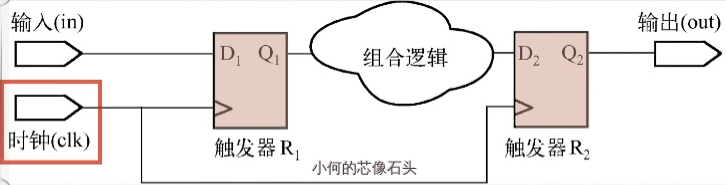

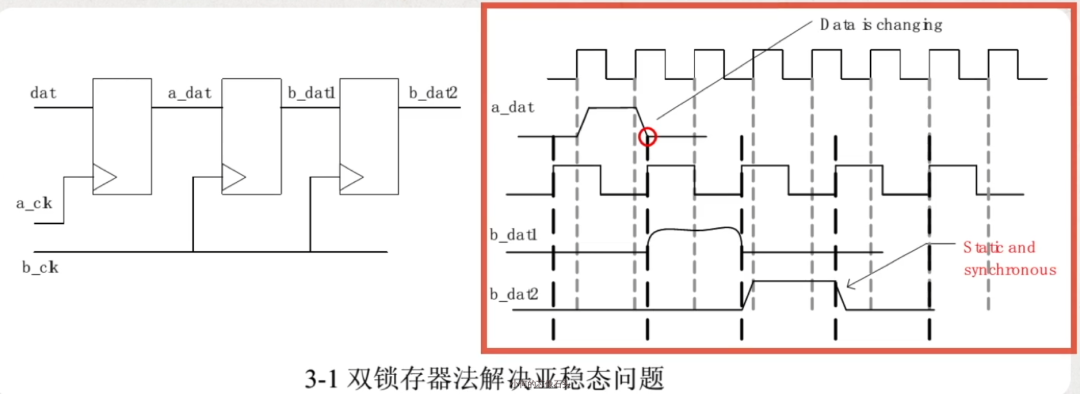

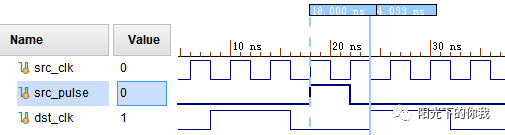

雙鎖存器電平同步器

雖然說的是鎖存器,但實際上是兩個觸發器:

- 一個信號在過渡到另一個時鐘域時,如果僅僅用一個觸發器將其鎖存,那么用b_clk進行采樣的結果將可能是亞穩態。這也是信號在跨時鐘域時應該注意的問題。

為了避免上節所述的亞穩態問題,就應當使參數 MTBF 盡可能的大,通常采用的方法是雙鎖存器法,即在一個信號進入另一個時鐘域之前,將該信號用兩個鎖存器連續鎖存兩次,最后得到的采樣結果就可以消除亞穩態問題。

雙鎖存器法,優點:

- 結構簡單、易實現,面積消耗很小。

缺點:

- 增加了兩級觸發器延時;

- 高性能計算中,兩個時鐘周期消耗對系統性能有消極的影響。

- 當快時鐘域轉到慢時鐘域時,易造成慢時鐘采樣丟失(還未來得及采樣,數據就變化了)。

使用條件:

- 常用于慢時鐘域轉到快時鐘域

- {(Clk_slow的周期)} > {(Clk_fast的周期) + (路徑延時)} ,確保信號可以被Clk_fast采樣到(假設Clk_fast和Clk_slow起始時刻相同求得)

- {(data數據變化間隔)}>{(Clk_slow的周期)+2*(CIk_fast的周期) +(路徑延時)},確保所有的數據變化均能采集到。

結論:

- 對于典型的0.25gm 工藝 ASIC 庫中的一個觸發器,則 MTBF=2.01(day ) ,即觸發器每兩天便可能出現一次亞穩態。如果將采樣時間和異步事件觸發頻率都提高,亞穩態出現還要頻繁。

- 對于同樣的參數,雙鎖存器法可將MTBF提升為9.57* 年,這個數值足夠保證電子系統穩定地運行。

- 兩級觸發器已經將MTBF變得足夠大

- 三級或者更多級雖然能將亞穩態出現概率 降得更低 ,但是影響電路效率

增加寄存器進行同步的方法,只是不斷降低亞穩態出現概率

單bit信號跨時鐘域如何傳輸

慢時鐘到快時鐘的信號傳輸

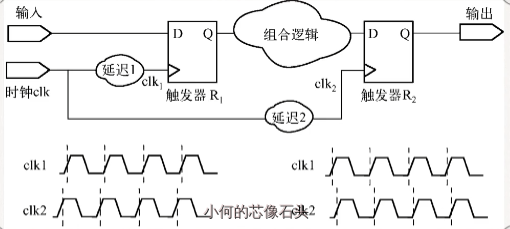

采用邊沿檢測同步器電路。這種方法通常應用在慢速向快速時鐘傳遞過程中,可以檢測輸入信號的上升沿,也可以檢測它的下降沿。輸出的的與門間相差一個快時鐘的延遲:

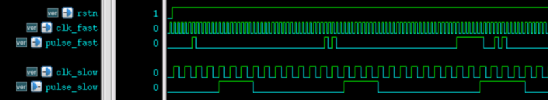

其時序圖為:

適用條件:

- 輸入數據的寬度必須比—個接受時鐘周期加上一個同步觸發器的hold時間要長,最安全的就是兩個同步周期寬度。

- 保證: 慢時鐘域的脈沖足夠保持到被快時鐘的同步器拿到

快時鐘到慢時鐘的信號傳輸

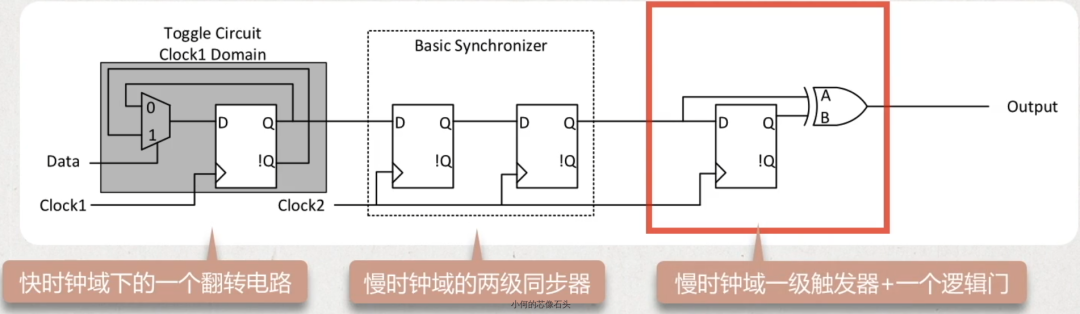

對于快時鐘域到慢時鐘域,通常采用脈沖同步器進行同步。這個電路結構中,最左邊是快時鐘域下的一個翻轉電路。中間是慢時鐘域的兩級同步器,最后是慢時鐘域一級觸發器+一個邏輯門。

基本功能是從快時鐘域取出一個單時鐘寬度脈沖,然后在慢時鐘域中建立另一個單時鐘寬度的脈沖。對電路結構的功能分析:

限制如下:

- 輸入脈沖之間的最小間隔必須等于兩個同步器時鐘周期。

- 如果輸入脈沖相互過近,則新時鐘域中的輸出脈沖也緊密相鄰,結果是輸出脈沖寬度比一個時鐘周期寬。

- 當輸入脈沖時鐘周期大于兩個同步器時鐘周期時,這個問題更加嚴重。

- 這種情況下,如果輸入脈沖相鄰太近,則同步器就不能檢測到每個脈沖。

對單bit同步器總結:

三種同步器總結

- 電平同步器,輸入信號必須保持兩個接受時鐘周期寬度,每一次同步之后,輸入信號必須恢復到無效狀態。

- 邊沿檢測同步器,適用于低頻時鐘域向高頻時鐘域傳輸,輸入信號必須保持兩個接受時鐘周期寬度。

- 脈沖檢測同步器,適用于高頻時鐘域向低頻時鐘域傳輸,輸入的脈沖時間的距離必須保持兩個接收時鐘周 期以上。

采用結繩法 進行單bit信號傳輸

- 信號從快時鐘域到慢時鐘域過渡時 ,慢時鐘將可能無法對變化太快的信號實現正確采樣;

- 上述同步器法對兩個時鐘之間的關系要求很嚴格,而“結繩法”適合任何時鐘域的過渡。

“結繩法1”

原理:

- 將快時鐘信號的脈沖周期延長,等到慢時鐘同步采樣后再“解繩”,還原為原來的脈沖周期寬度。

- 利用數據的邊沿作時鐘(圖中上升沿)。(可以將脈沖無限延長,直到可以采集到數據,然后復位,要考慮產生數據的頻率)。

- 這種結繩法的原理是,數據作為Din_clkA ,即當數據有上升沿(0->1)時,寄存器1的輸出將會穩定在高電平,此時等待CIkB采樣;當CIkB完成采樣后,寄存器4會輸出高電平,若此時Din_clkA為低電平,那么即可完成復位,開始下一次采樣等待。

- 這里需要注意的是當數據來臨(上升沿)時,ClkB域需要等待3個ClkB才會在寄存器4輸出并完成輸入端的復位,所以Din_CIkA如果變化較快,即持續時間短于3個CIkB,也就是Din_ClkA頻率大于CIkB的1/3,那么這時Din_ClkA的變化將無法被采樣到,因為CIkB域需要3個CIkB才能完成采樣,并且此時Din_CIkA必須是低電平才能復位,采用異步復位。

- 在慢時鐘采樣快時鐘的時候,結繩法適合采樣數據較少(即脈沖間隔較大的控制信號。即脈沖間隔Ta>3Tb;即等待3個clkB時鐘后,完成復位,才允許下一個輸入脈沖。

結繩法2:

- 利用數據作為異步復位,置位信號:

結繩法3:

- 利用握手協議:

電路功能為:

結繩法總結

- 結繩就是將單脈沖延長,以方便采集到數據。

結繩的方法歸結為2類:

- 利用脈沖的邊沿做時鐘;

- 利用脈沖的電平(部分場合要求最小脈沖寬度)做選擇器或者異步復位,置位。

- 另外的關鍵點就是什么時候結繩結束(采集到了數據就要讓對方回到初始狀態)

這里的操作也有2種方法:

- 利用采集到的脈沖做異步復位,置位。

- 利用采集到的脈沖再次結繩采集做握手響應信號。

總結:

- 結繩法可以解決快時鐘域向慢時鐘域過渡的問題,且其適用的范圍很廣。

- 結繩法實現較為復雜,特別是其效率不高,在對設計性能要求較高的場合應該慎用。

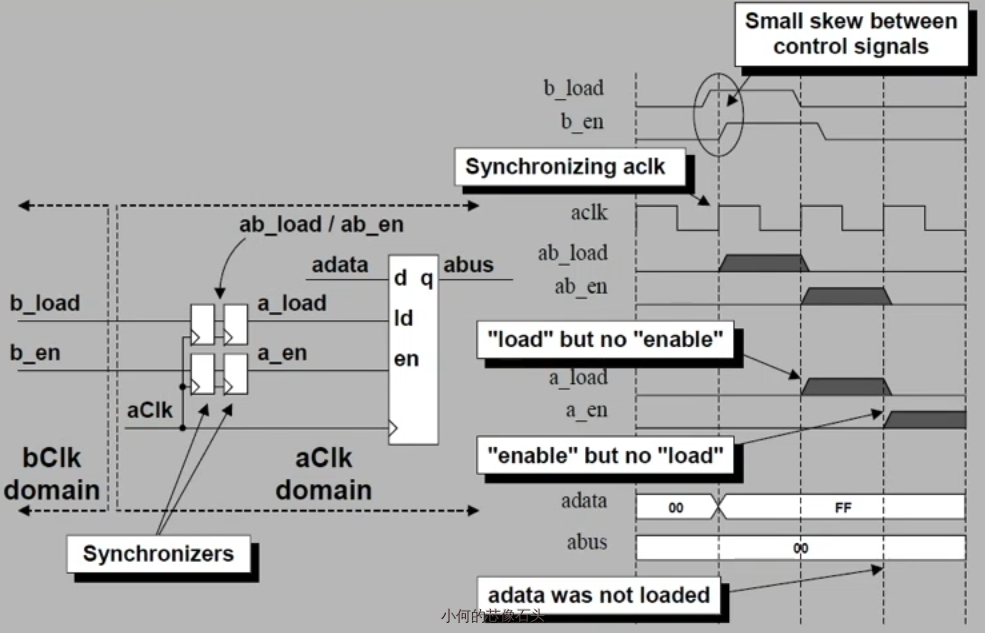

傳輸兩個同時需要的信號(b_load 和b_en)

多個控制信號跨時鐘域僅僅通過簡單的同步器同步有可能是不安全的

當兩個信號中出現一點skew時,跨時鐘域不一定能夠正確在同一個時刻被采樣到:

b_load和b_en同步至a_clk時鐘域,如果這兩個信號有一個小的ske導致在a_clk時鐘域中兩個信號并不是在同一時刻起作用,與在b_clk中的邏輯關系不同。

解決方法(合并信號)

將b_load和b_en信號在b_clk時鐘域中合并成一個信號b_lden,然后同步至a_clk中。

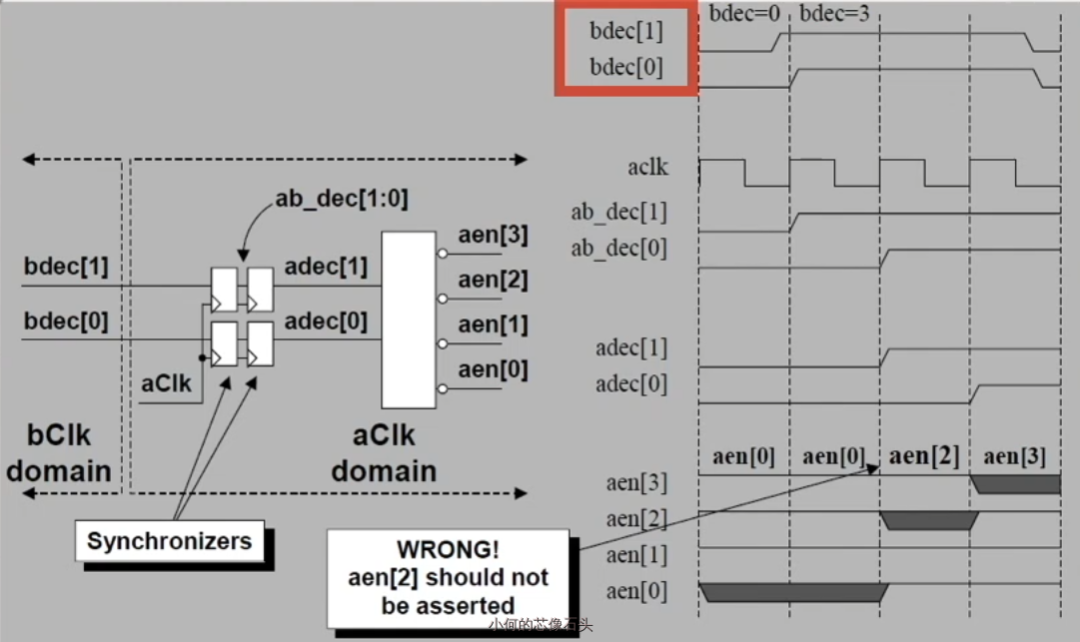

對不能合并的情況

如果遇到不能合并的情況,如譯碼信號。如果Bdec[0]、bdec[1]間存在skew將導致同步至a_clk中后譯碼錯誤,出現誤碼。

在這種情況下,建議加入另一個控制信號,確保bdec[0]、bec[1]穩定時采。例如在bdec[0]、bec[1]穩定輸出后一到兩個周期b_clk域輸出一個en信號,通知a_clk域此時可以采bdec[O]、bec[1]信號。這樣可確保正確采樣。

小結

采樣中“快到慢”與“慢到快”在考慮問題時有什么區別?

慢到快:

- 只需要考慮亞穩態問題

快到慢:

- 亞穩態問題

- 考慮慢時鐘的采樣速率問題。因為根據采樣定理,采樣頻率低于信號最高頻率2倍的時候,是無法完整采樣的。

-

電磁兼容

+關注

關注

54文章

1874瀏覽量

97866 -

寄存器

+關注

關注

31文章

5336瀏覽量

120248 -

EDA工具

+關注

關注

4文章

267瀏覽量

31789 -

觸發器

+關注

關注

14文章

2000瀏覽量

61134 -

同步電路

+關注

關注

1文章

60瀏覽量

13310

發布評論請先 登錄

相關推薦

單bit信號跨時鐘域如何傳輸?

單bit信號跨時鐘域如何傳輸?

評論