大多數FPGA程序員認為,高級工具總是發出更大的比特流,作為提高生產率的 "代價"。但是這總是真的嗎?

在本文中,我們展示了一個真實的例子,我們使用傳統的RTL/Verilog工具創建了一個普通的網絡函數(RSS),然后在相同的硬件上使用高級合成工具(HLS)來實現相同的功能。

我們發現,令人驚訝的是:HLS方法實際上使用了更少的FPGA門和內存。這好像和我們習慣的思維不太一致啊…

通過使用Vivado(Xilinx)或Intel(Quartus)工具,FPGA開發的HLS方法是只抽象出可以在C/C++環境中輕松表達的應用程序的部分。

要想在HLS取得成功,重要的是要認識到項目中哪些部分或模塊適合在HLS中實現。基本準則可以概括如下(可能描述不太清楚準確):

目標用途一般是以高級語言開始定義的IP塊。一個數學算法會很有效,或者像我們的RSS塊那樣,一些網絡協議處理。

另一類用途是定義不明確的塊,因此可能需要多輪的實現。這里最大的好處是允許HLS工具自動對產生的本地FPGA代碼進行流水線處理,通常比快速手工編碼流水線的階段要少。另外,當需要修改手工編碼的流水線時,一個并行路徑上的延遲變化會對所有的東西產生連鎖反應。使用HLS工具自動進行第二次流水線,從頭開始,消除了這種頭痛的問題。

最后,HLS流程使不同FPGA品牌之間的代碼移植變得更加容易。這是因為HLS會自動生成適當數量的流水線階段--這是你在使用Verilog或VHDL時需要手動指定的。

目前HLS的局限性很明顯,它的范圍限于IP塊。應用團隊仍然需要其他組件的RTL。還應該注意的是,對于最簡單的代碼或主要由預先優化的組件組成的大型設計來說,HLS是一個不太理想的選擇。

1. 用于做對比的應用,FPGA上的聯網RSS

什么是RSS?RSS是 "接收方擴展 "的意思。它是一種散列算法,用于在多個CPU上有效分配網絡數據包。RSS是現代以太網卡的一項功能,一般實現微軟定義的特定托普利茨哈希。

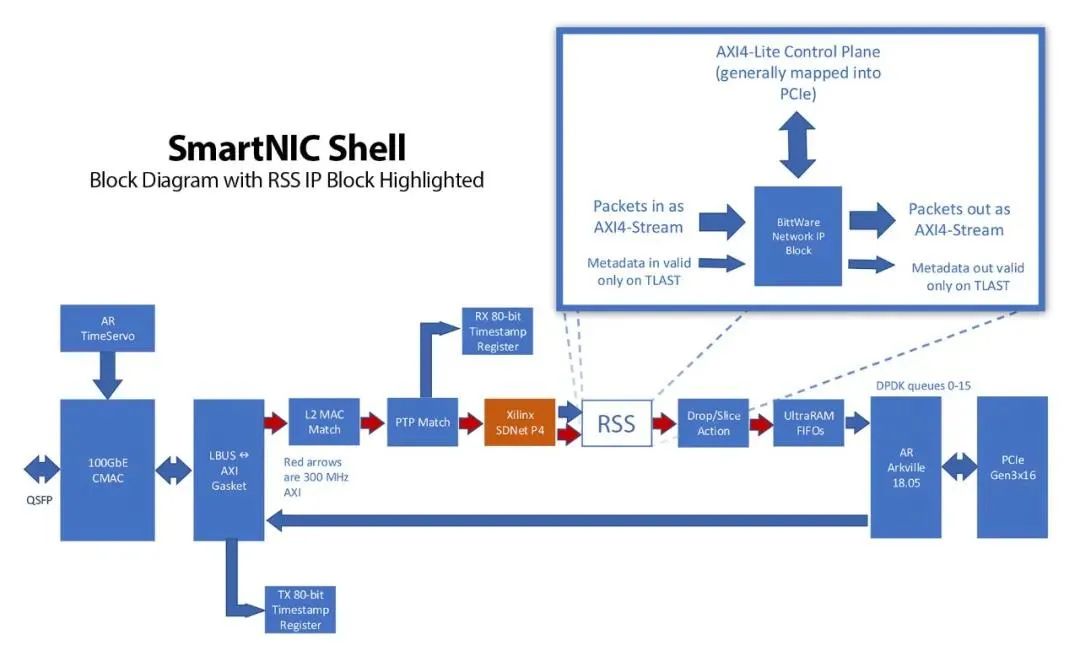

SmartNIC Shell框架的實施實例框圖。這里的RSS塊被替換成了HLS實現。

2. 用RTL和HLS實現RSS的結果對比

我們評估的假設如下:本地FPGA編碼總是導致最小的資源使用。然而,BittWare的一位工程師對這一決定提出了質疑,并在HLS中重新實現了RSS,以測試這一方法。他是對的,現在BittWare已經用HLS代碼取代了我們SmartNIC Shell中的RSS模塊和解析器模塊。

兩種實現方式的最大區別是Verilog/RTL版本使用了FIFO,而HLS C++版本沒有使用。我們很驚訝地看到,通過轉移到HLS,資源的使用量實際上下降了——這與我們預想的差異較大。

開發時間呢?粗略地說,我們看到原生RTL版本的時間線為一個月,而HLS代碼在一周內完成。

3. 總結

“今天的高層FPGA開發工具被設計用來減少上市時間和對硬件工程師的依賴。然而,使用這些工具總是帶來應用性能的妥協——無論是速度還是硅資源”。然而這種假設是錯誤的。

我們發現使用HLS為BittWare的SmartNIC Shell開發IP塊,將開發時間從大約一個月縮短到一周。我們還發現,它實際上使用了更少的門電路來實現。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1635文章

21837瀏覽量

608346 -

Verilog

+關注

關注

28文章

1355瀏覽量

110842 -

HDL

+關注

關注

8文章

328瀏覽量

47562 -

函數

+關注

關注

3文章

4353瀏覽量

63294 -

Vivado

+關注

關注

19文章

819瀏覽量

67264

原文標題:Vivado HLS 能否取代HDL開發

文章出處:【微信號:Hack電子,微信公眾號:Hack電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

探索Vivado HLS設計流,Vivado HLS高層次綜合設計

請問如何只下載Vivado HLS 2015.2

Vivado HLS設計流的相關資料分享

嵌入式硬件開發學習教程——Xilinx Vivado HLS案例 (流程說明)

Hackaday讀者有話說:Vivado HLS使用經驗分享

用Vivado-HLS實現低latency 除法器

基于Vivado HLS的計算機視覺開發

如何創建Vivado HLS項目

如何使用Tcl命令語言讓Vivado HLS運作

關于Vivado HLS錯誤理解

極客對Xilinx Vivado HLS工具使用經驗和心得

Vivado HDL編寫示例

將VIVADO HLS設計移植到CATAPULT HLS平臺

Vivado HLS能否取代HDL開發

Vivado HLS能否取代HDL開發

評論