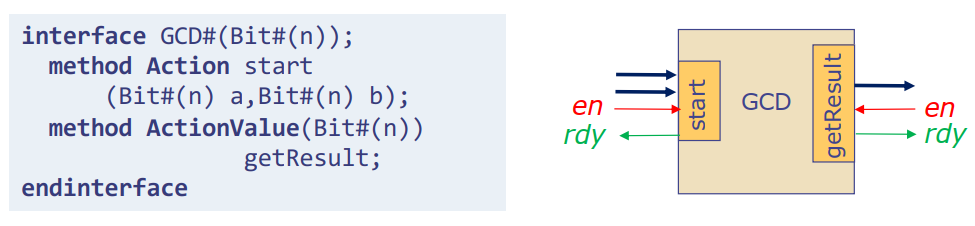

Bluespec SystemVerilog (BSV) 是由Arvind 開發的 Bluespec 語言,這是一種高級功能 硬件 描述編程語言,本質上是Haskell(Haskell ( / ?h ?s k ?l / ) 是一種通用的、靜態類型的、純函數式 編程語言,具有類型推斷和惰性求值。)的擴展,用于處理一般的芯片設計和電子設計自動化。Bluespec的主要設計者和實現者是Lennart Augustsson。Bluespec 被部分評估(轉換 Haskell 部分)并編譯為術語重寫系統(TRS)。它帶有一個SystemVerilog前端。BSV 編譯為Verilog RTL 設計文件。

為什么要 BSV?Verilog 不好用?

BSV 是一門高級硬件描述語言(High-Level Hardware Description Language, HL-HDL),與 Verilog 一樣,被用于 FPGA 或 ASIC 的設計和驗證。BSV 于 2003 年被 Bluespec 公司開發,期間是商業收費工具,到 2020 年它的編譯器才開源,這才給了我們接觸它的機會。

Verilog 的語法簡單、特性少,卻能全面且精準地描述數字電路,是“小而美”的語言。學習 Verilog 時,只需要掌握3種常見寫法:assign, always @ (*) 和 always @ (posedge clk) ,剩下的就依賴于你對電路設計的理解了。當然,這才是最難的,包括各種繁雜的硬件設計思維——狀態機、并行展開、流水線化、握手信號、總線協議等。

各位讀到這里有沒有意識到問題——用如此簡單的抽象級別來描述如此復雜的數字電路系統,會不會很吃力?相信每個接觸過復雜的 Verilog 系統的讀者,都體會過被 always 塊下的幾十個狀態所支配的恐懼,也清晰地記得模塊實例化時那幾十行嚇人的端口連接。因此,我們需要一種抽象層次更高的 HDL 來提高開發效率,BSV 就能勝任這一工作。

對BSV有興趣的可以看看上面文章《爆肝6萬字的 Bluespec SystemVerilog (BSV) 中文教程上線了》。

今天的核心是使用BSV設計一款游戲,看下在實際設計中BSV表現如何~

使用BSV設計《太空入侵者》

緒論

2020年1月,Bluespec開源了bsc(Bluespec SystemVerilog Compiler)。因此我安裝了 bsc,這是一個編譯器,可以對用BSV (Bluespec SystemVerilog)編寫的設計進行高級綜合。BSV 與任何其他語言一樣,無法通過閱讀手冊來學習,我認為學習新語言的唯一方法是實際設計應用程序。因此,我嘗試使用 BSV 設計《太空入侵者》游戲。

BSV

簡而言之,Verilog HDL 是一種標準化為 IEEE 1364 的硬件設計語言 (HDL),而 SystemVerilog 是其標準化為 IEEE 1800 的擴展。BSV 是進一步擴展 SystemVerilog 的 HDL。

使用設備

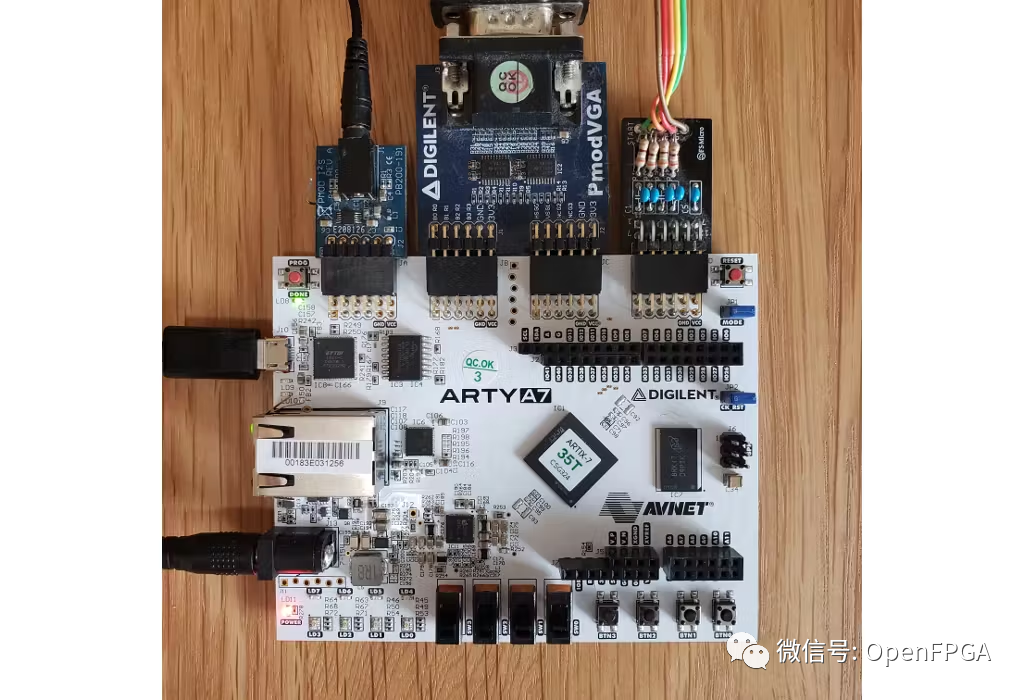

使用的開發板如下:

第一步 - 聲音 FSM(有限狀態機)設計

第一次應用BSV時,聲音狀態機的規模比較小,所以這是第一個設計目標。

確定聲道

游戲中使用了 10 種不同的聲音;需要確定同時發生的數量(=聲道的數量)。考慮到游戲場景中同時發生的條件,假設有4個通道:玩家自己的船的聲音、入侵者的聲音1和2、UFO的聲音。

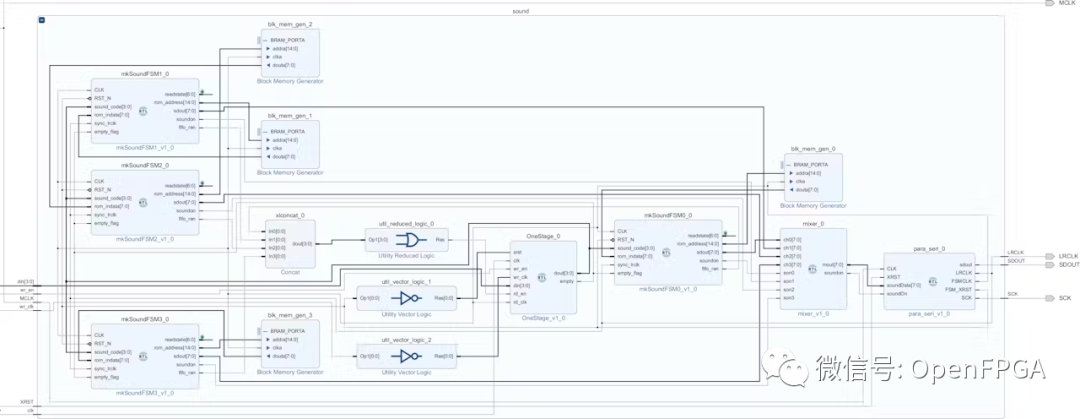

聲音系統框圖

框圖如下圖所示。聲音FSM從之前的設計擴展到4個通道。

第二步——游戲FSM設計

然后繼續進行游戲FSM的狀態機設計。

在設計聲音 FSM 時,我使用基于狀態的設計方法來設計 FSM 。本文中的基于狀態的FSM設計方法是指將序列手動分解為狀態,并為每個狀態一一編寫規則的方法。這種方法基本上需要與Verilog相同的工時。換句話說,使用高級語言沒有什么好處。

另一方面,BSV 有一個名為StmtFSM的庫,可以高效地設計狀態機。在這個游戲FSM中,我充分利用了這一點,設計時無需手動進行狀態分解。在本文中,這種方法將被稱為基于序列的方法。

博弈FSM算法

基本上,我發現游戲可以用與用C編寫相同的方式來編寫。例如,如果我考慮子彈移動、碰撞檢測、碰撞處理以及顯示和擦除爆炸標記的算法,則算法是對于自己和敵人的子彈來說都是一樣的,如下所示。

if(bullet_explosion_timer>=1){//Bulletexploding bullet_explosion_timer++; if(bullet_explosion_timer==MAX){ bulletdeletion;//logicaldeletion erasebullet_explosion_mark;//logicalerasure bullet_explosion_timer<=?0; ????} }?else?{ ????if?(no?bullets?and?bullet?generation?condition)?{ ????????bullet?generation?process; ????????bullet?sound;?//?only?own?bullets,?no?sound?for?enemy?bullets ????} ????if?(bullet?exists)?{ ????????Collision?detection; ????????if?(collision?with?object)?{?//?invader?and?UFO?for?own?bullets,?ship?for?enemy?bullets ????????????delete?bullet;?//?logical?deletion ????????????erase?bullet_mark;?//?Physical?deletion ????????????object?state?<=?explosion; ????????????object_explosion_timer?<=?0; ????????}?else?if?(up?down?hash?||?base?||?bullets)?{?//?bullets:?if?own?bullets,?enemy?bullets;?if?enemy?bullets,?own?bullets ????????????erase?bullet_mark;?//?physical?erase ????????????show?bullet_explosion_mark; ????????????bullet_explosion_timer?<=?1;?//?start?timer ????????}?else?{?//?if?no?collision ????????????advance?bullet;?//?if?no?collision,?advance?the?bullet;?//?if?no?collision,?advance?the?bullet ????????} ????} }

另一方面,該對象需要專門的處理,如下面的代碼所示。

if(objectstate==explosion){

if(object_explosion_timer==0){

object_explosion_timer<=?1;?//?start?timer

????????object?explosion?sound;

????????show?object_explosion_mark?;

????}?else?{

????????object_explosion_timer++;

????????if?(object_explosion_timer?==?MAX)?{

???????????delete?object;?//?logical?deletion

???????????erase?object_explosion_mark;?//?physical?erasure

????????}

????}

}

通過應用 StmtFSM,可以將項目符號序列描述為一種算法,而無需將其分解為逐個時鐘狀態。我用類C語言編寫了上面的偽代碼,但我只需要將BSV中的'{'更改為seq ,將'}'更改為endseq 。if、while、for等控制語法由bsc進行行為綜合,并轉換為Verilog中的狀態機。

游戲完成

下面的動圖展示了可能是世界上第一部由 BSV 設計的《太空入侵者》游戲的視頻。

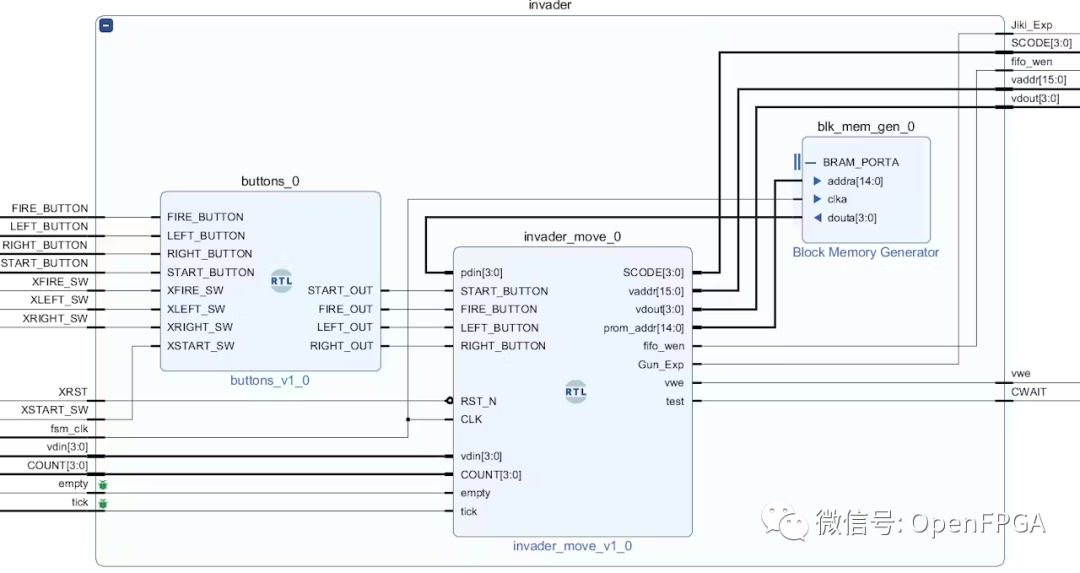

完整的入侵者層次結構如下圖所示。Button_0 只是一個對板載開關和外部開關進行或運算的電路。入侵者_移動_0是BSV設計的游戲FSM。blk_mem_gen_0是連接到游戲FSM的ROM,用于存儲入侵者的模式等。

BSV的優勢

雖然 BSV 看起來效率更高,但它增加了 bsc 的編譯時間,對于大型設計來說可能會超過一個小時。因此,對于這樣的設計,修改、模型創建和仿真的TAT(周轉時間)將非常長,這可能使其效率低于Verilog。然而,Bluesim 中的仿真速度比 iverilog 中快約 3, 000 倍。

總結

對于這一“語言”,其發展肯定會在某一方面有突出優點,之后才能被慢慢接受,類似SpinalHDL/CHISEL等,但是該門語言目前未在業內受到重視,但是未來的發展我抱有希望

審核編輯:湯梓紅

-

Verilog

+關注

關注

28文章

1351瀏覽量

110077 -

編程語言

+關注

關注

10文章

1942瀏覽量

34711 -

數字電路

+關注

關注

193文章

1605瀏覽量

80581 -

開源

+關注

關注

3文章

3320瀏覽量

42473 -

編譯器

+關注

關注

1文章

1624瀏覽量

49108

發布評論請先 登錄

相關推薦

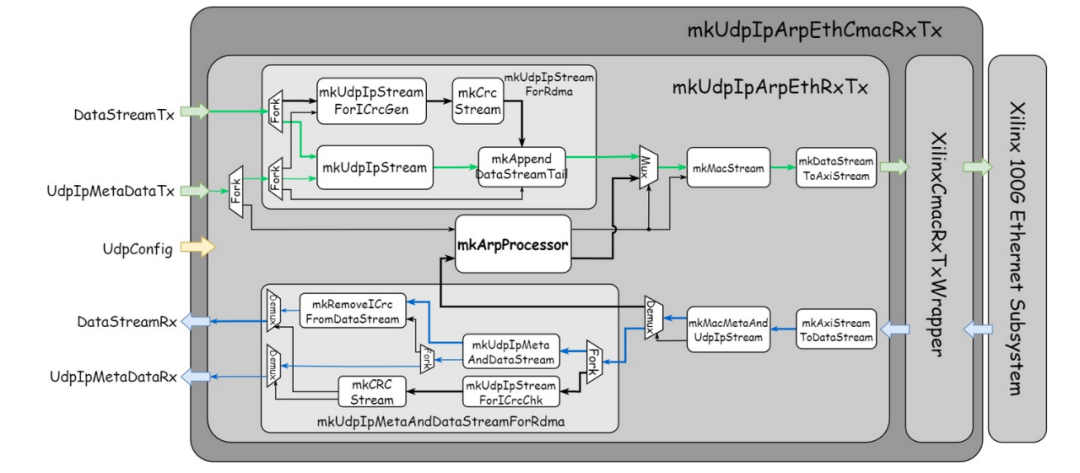

Bluespec SytemVerilog握手協議接口轉換設計實現

blue-ethernet高性能FPGA網絡數據包處理項目簡介

做FPGA工程師需要掌握SystemVerilog嗎?

SystemVerilog 3.1a語言參考手冊

SystemVerilog設計語言

基于SystemVerilog語言的驗證方法學介紹

開源的Bluespec SystemVerilog (BSV)語言表現如何?

開源的Bluespec SystemVerilog (BSV)語言表現如何?

評論