PWM 比較器的功能

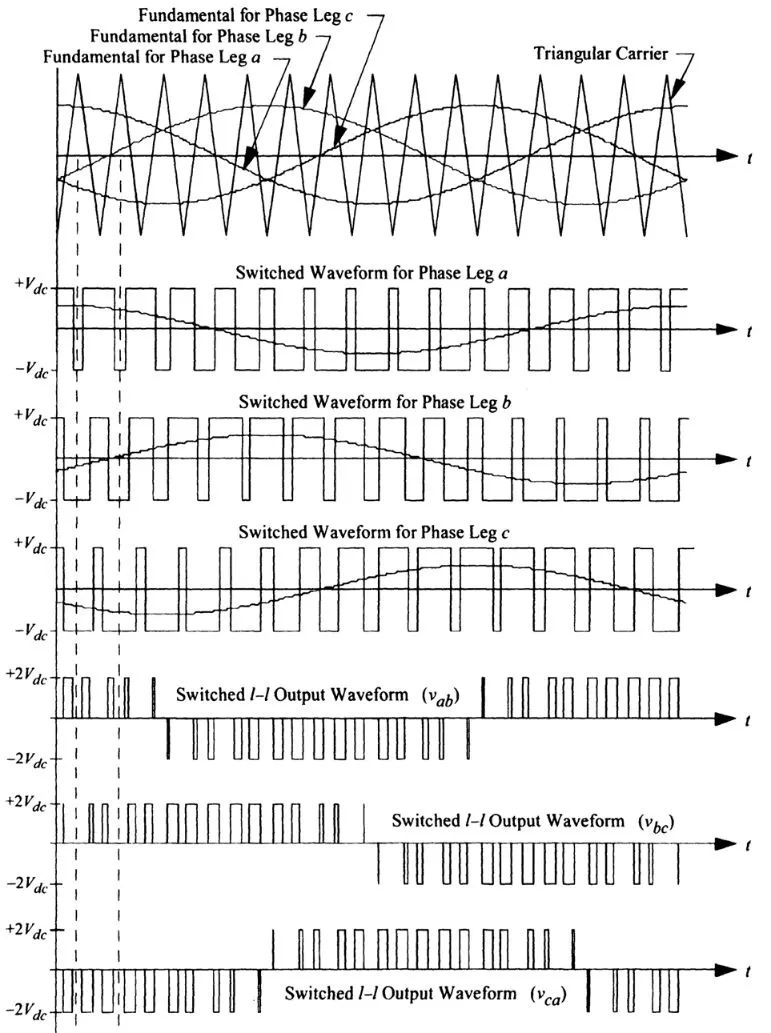

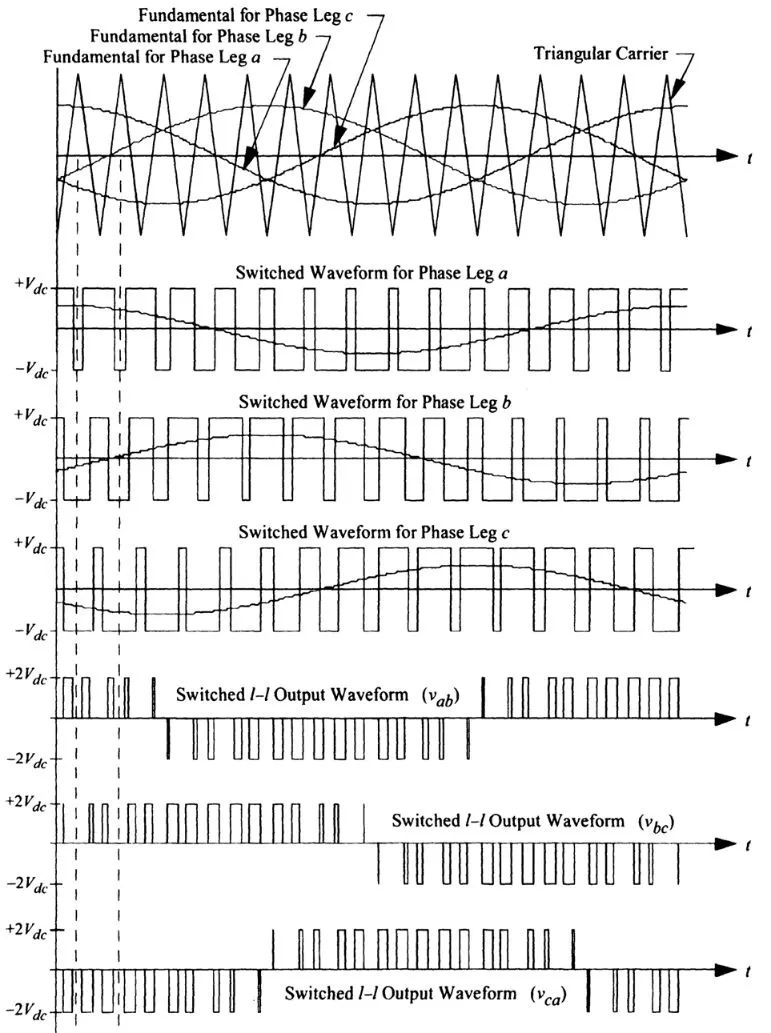

還是以本系列文章中,用到的三相兩電平逆變器為控制對(duì)象。下圖是正弦波調(diào)制(SPWM)的三相兩電平逆變器的波形。

輸入的是三相的正弦波信號(hào),三角載波與正弦信號(hào)波進(jìn)行比較,當(dāng)正弦信號(hào)波的值大于三角載波的值,輸出“1”,否則,就輸出“0”;PWM比較器一共生成6個(gè)PWM信號(hào),控制6個(gè)IGBT的開(kāi)通和關(guān)斷。PWM比較器輸出“1”控制IGBT開(kāi)通,“0”信號(hào)IGBT關(guān)斷。控制逆變器輸出的三相相電壓和三相線電壓如下圖所示。

對(duì)于三相兩電平逆變器,為了防止上下橋臂同時(shí)導(dǎo)通而短路,PWM比較器還需要插入死區(qū)時(shí)間。

此外,為了讓電流、速度和位置采樣與PWM占空比的更新同步,以及控制器算法模型的觸發(fā)運(yùn)行,必須還有中斷觸發(fā)信號(hào)生成功能。

因此整個(gè)PWM比較器包括四部分:

(1) 三角載波生成;

(2) 信號(hào)比較,生成PWM控制信號(hào);

(3) 插入死區(qū)時(shí)間;

(4) 中斷觸發(fā)信號(hào)生成;

正弦波調(diào)制(SPWM)的三相兩電平逆變器的波形

三角載波生成

因?yàn)槿禽d波生成的模型是在FPGA中運(yùn)行的,因此數(shù)據(jù)類(lèi)型需要整型。

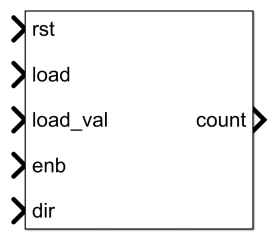

最方便的方法就是使用Simulink的HDL Coder模型庫(kù)中的HDL Counter模塊。通過(guò)控制輸入端口dir控制HDL Counter模塊的計(jì)數(shù)方向。

HDL Counter模塊

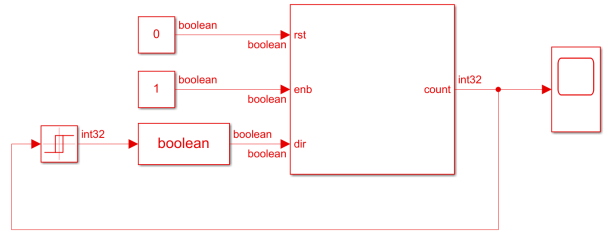

示例模型如下:

三角載波生成的Simulink模型

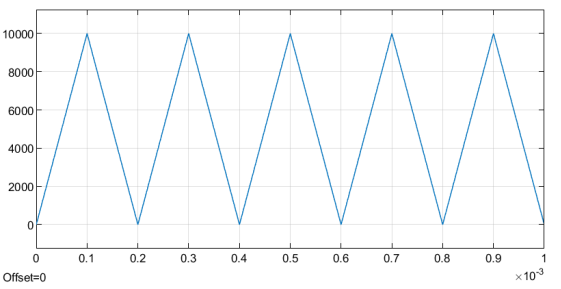

仿真步長(zhǎng)為1e-8,Relay 模塊的Switch on point為10000,Switch off point為0,輸出“0”或者“1” 控制HDL Counter模塊的計(jì)數(shù)方向,生成0~10000的三角波,頻率為5kHz。

三角載波信號(hào)

PWM 信號(hào)生成

三角載波與信號(hào)波進(jìn)行比較,當(dāng)信號(hào)波的值大于三角載波的值,輸出“1”,否則,就輸出“0”;PWM比較器一共生成6個(gè)PWM信號(hào),控制6個(gè)IGBT的開(kāi)通和關(guān)斷。

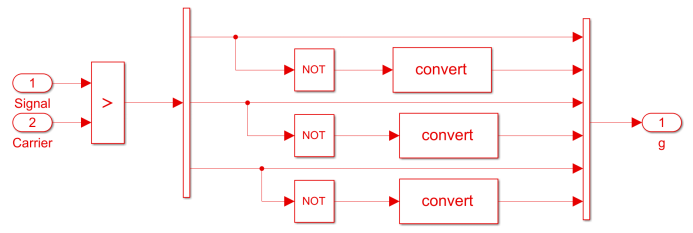

此功能的Simulink模型如下:

PWM信號(hào)生成的Simulink模型

死區(qū)時(shí)間

通常死區(qū)時(shí)間的插入通過(guò)增加PWM信號(hào)的開(kāi)通延時(shí)實(shí)現(xiàn)的。

簡(jiǎn)單說(shuō)就是:如果PWM信號(hào)由“1”變“0”,即由開(kāi)通變?yōu)殛P(guān)斷,則馬上關(guān)斷;如果PWM信號(hào)由“0”變“1”,即由關(guān)斷變?yōu)殚_(kāi)通,則延時(shí)T_delay再開(kāi)通;此功能的Simulink模型如下,C_delay端口為輸開(kāi)通延時(shí)計(jì)數(shù)值。

死區(qū)時(shí)間的Simulink模型

中斷觸發(fā)信號(hào)生成

此功能比較簡(jiǎn)單,Simulink模型如下圖所示,在三角波的底點(diǎn)和頂點(diǎn)都產(chǎn)生中斷,如果只在底點(diǎn)或者只在頂點(diǎn),可以根據(jù)需要修改即可。

中斷觸發(fā)信號(hào)生成的Simulink模型

以上模型皆可以通過(guò)Simulink的HDL Coder工具生成HDL代碼,部署至Speedgoat的FPGA板卡。

-

IGBT

+關(guān)注

關(guān)注

1278文章

4076瀏覽量

254920 -

三相逆變器

+關(guān)注

關(guān)注

3文章

94瀏覽量

19388 -

PWM比較器

+關(guān)注

關(guān)注

0文章

9瀏覽量

8072 -

FPGA開(kāi)發(fā)板

+關(guān)注

關(guān)注

10文章

125瀏覽量

31997 -

simulink仿真

+關(guān)注

關(guān)注

0文章

75瀏覽量

8784

發(fā)布評(píng)論請(qǐng)先 登錄

基于模型的設(shè)計(jì)(MBD)的深入討論

電動(dòng)助力轉(zhuǎn)向EPS——理論公式推導(dǎo)及simulink模型

Simulink模型生成代碼

如何建立一個(gè)simulink模型

永磁同步電機(jī)控制系統(tǒng)仿真—PWM比較器的Simulink模型

評(píng)論