6月21日,在結束美洲、歐洲、中國臺灣等地的年度技術論壇之后,臺積電正式在中國上海召開年度技術論壇。本場論壇由臺積電總裁魏哲家、臺積電中國總經理羅鎮球領銜,臺積電業務開發暨海外運營辦公室資深副總張曉強、歐亞業務及技術研究資深副總侯永清也都有出席。在此次論壇上,臺積電分享了其最新的技術路線以及對產業未來趨勢的看法。此外,之前傳聞還顯示,臺積電相關高管還將拜訪阿里巴巴 、壁仞等大陸重要客戶。

臺積電最新2022年年報顯示,去年產出占全球半導體(不含存儲)市場產值30%,較前一年度的26%增加。公司營收凈額以客戶營運總部所在地區分,北美市場占比高達68%、亞太市場(不含日本與中國大陸)占比11%、大陸市場占比11%。另外,臺積電大陸廠區獲利則約占臺積電全年度獲利個位數百分比。

從今年第一季度財報來看,中國大陸業務占臺積電營收10%至15%,僅次于北美業務。

從臺積電在中國大陸的產能布局來看,臺積電2002年在上海松江設立8吋晶圓廠,并于2016年在南京設12吋晶圓廠和一座設計服務中心。目前,臺積電南京廠的28nm制程擴產已于去年量產。

數據顯示,臺積電上海廠營收在臺積電2021年總營收當中的占比僅約1%,上海與南京廠2021年獲利約200億元新臺幣(約合人民幣46.4億元),由于臺積電獲利穩健成長,該年度累計獲利超過5,100億元新臺幣(約合人民幣1184億元),大陸兩個廠區獲利貢獻接近4%,仍有相當大的成長空間。

此次臺積電上海技術論壇的召開以及傳聞魏哲家將在會后帶隊拜訪中國大陸客戶,目的是為了進一步加強與國內廠商的合作,降低如美國新規等外在因素對于臺積電與國內客戶之間正常合作的影響,即明確對于在非實體清單內的國內客戶可以不受影響的正常代工合作,也就是說目前臺積電最先進的3nm代工都不會受到影響。目前國內已經有若干客戶在采用臺積電3nm工藝代工。不過,未來涉及GAA的制程可能存在影(美方有限制GAA相關EDA)。

對于臺積電來說,在半導體行業下行周期之下,加強與大陸廠商合作,也有望幫助臺積電提升產能利用率和維持毛利率。

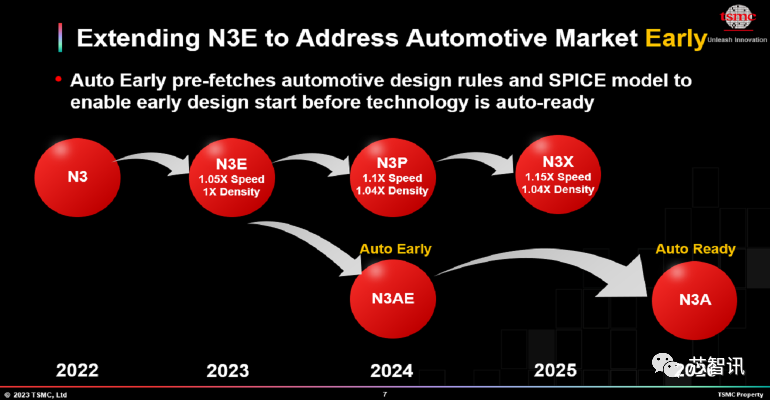

對于此次上海論壇的內容,除了宣布將推出面向汽車的N3AE和N3A制程,以及面向射頻的N4PRF制程之外,基本與之前的海外技術論壇內容相近。

臺積電認為隨著 AI、5G 和其他先進工藝技術的發展,全球正通過智能邊緣網絡產生大量的運算工作負載,因此需要更快、更節能的芯片來滿足此需求。預計到2030年,因需求激增,全球半導體市場將達到約 1萬億 美元規模,其中高性能計算(HPC)相關應用占 40%、智能手機占 30%、汽車占 15%、物聯網占10%。

2022年,臺積公司與其合作伙伴共創造了超過 12,000 種創新產品,運用近 300 種不同的臺積公司技術。臺積電表示,將持續投資先進邏輯工藝、3DFabric 和特殊制程等技術,在適當的時間提供合適的技術,協助推動客戶創新。

一、先進制程

隨著臺積電的先進工藝技術從 10 納米發展至 2 納米,臺積電的能源效率在約十年間以 15% 的年復合增長率提升,以支持半導體產業的驚人成長。

臺積電先進工藝技術的產能年復合增長率在 2019 年至 2023 年間將超過40%。

作為第一家于 2020 年開始量產 5 納米的晶圓廠,臺積電通過推出 N4、N4P、N4X 和 N5A 等技術,持續強化其 5 納米工藝家族。

臺積電的 3 納米工藝技術是半導體產業中第一個實現高量產和高良率的工藝技術,臺積電預計 3 納米將在移動和 HPC 應用的驅動下快速、順利地實現產能提升(ramping)。臺積電2024年和2025年分別推出 N3P 和 N3X 來提升工藝技術價值,在提供額外性能和面積優勢的同時,還保持了與今年推出的N3E 的設計規則兼容性,能夠最大程度地實現 IP 復用。

N3是臺積電3nm最初版本,號稱對比N5同等功耗性能提升10-15%、同等性能功耗降低25-30%,邏輯密度達提升了70%,SRAM 密度提升了20%,模擬密度提升了10%。但在去年的IEDM上,臺積電公開N3的高密度位單元僅將 SRAM 密度提高了約5%。雖然,N3的接觸式柵極間距(Contacted Gate Pitch, CGP)為 45nm,是迄今為止最密集的工藝,領先于Intel 4的50nm CGP、三星4LPP的54nm CGP和臺積電 N5的51nm CGP。但是 SRAM 密度僅5%的提升,意味著 SRAM設計復雜度會增加,導致成本成本顯著增加。并且N3的良率和金屬堆疊性能也很差。

總結來說,N3的實際的性能、功耗、量產良率和進度等都未能達到預期。于是有了今年的增強版的N3E。據悉,N3E修復了N3上的各種缺陷,設計指標也有所放寬,對比N5同等功耗性能提升15-20%、同等性能功耗降低30-35%,邏輯密度約1.6倍(相比原計劃的N3有所降低),芯片密度約1.3倍。根據臺積電最新披露的數據顯示,N3E相比N3將帶來5%左右的性能提升;而后續的N3P相比N3E則將帶來4%的密度提升,10%的性能提升;N3X相比N3P將帶來4%的密度提升,15%的性能提升。

二、特殊工藝

臺積電提供了業界最全面的特殊工藝產品組合,包括電源管理、射頻、CMOS 影像感測等,涵蓋廣泛的應用領域。從2017年到2022年,臺積電對特殊工藝技術投資的年復合增長率超過40%。到2026年,臺積公司預計將特殊工藝產能提升近50%。

汽車:將3nm帶入汽車市場

隨著汽車產業向自動駕駛方向發展,運算需求正在快速增加,且需要最先進的邏輯技術。到 2030 年,臺積電預計 90% 的汽車將具備先進駕駛輔助系統(ADAS),其中 L1、L2 和 L2+/L3 將有望分別達到 30% 的市場占有率。

在過去三年,臺積電推出了汽車設計實現平臺(ADEP),通過提供領先業界、Grade 1 品質認證的 N7A 和 N5A 工藝來實現客戶在汽車領域的創新。

為了讓客戶在技術成熟前就能預先進行汽車產品設計,臺積電推出了 AutoEarly,作為提前啟動產品設計并縮短上市時間的墊腳石。

●N4AE 是基于 N4P 開發的新技術,將允許客戶在 2024 年開始進行試產。

●從前面的臺積電的Roadmap來看,臺積電計劃在2024年推出業界第一個基于3nm的Auto Early技術,命名為N3AE。N3AE提供以N3E為基礎的汽車制程設計套件(PDK),讓客戶能夠提早采用3nm技術來設計汽車應用產品,以便于2025年及時采用屆時已全面通過汽車制程驗證的N3A 工藝技術。N3A 也將成為全球最先進的汽車邏輯工藝技術。

支持 5G 和聯網性的先進射頻技術

臺積電在 2021 年推出了 N6RF,該技術是基于公司創紀錄的 7 納米邏輯工藝技術,在速度和能源效率方面均具有同級最佳的晶體管性能。

●結合了出色的射頻性能以及優秀的 7 納米邏輯速度和能源效率,臺積電的客戶可以通過從 16FFC 轉換到 N6RF,在半數字和半類比的射頻 SoC 上實現功耗降低 49%,減免移動設備在能源預算以支持其他不斷成長的功能。

●臺積電在此次上海技術論壇上宣布推出最先進的互補式金屬氧化物半導體(CMOS)射頻技術 N4PRF,預計于 2023 年下半年發布。相較于 N6RF,N4PRF 邏輯密度增加 77%,且在相同效能下,功耗降低45%。N4PRF 也比其前代技術 N6RF 增加了 32%的 MOM 電容密度。

超低功耗

●臺積電的超低功耗解決方案持續推動降低 Vdd,以實現對電子產品而言至關重要的節能。

●臺積電不斷提升技術水平,從 55ULP 的最小 Vdd 為 0.9V,到 N6e 的 Vdd已低于 0.4V,我們提供廣泛的電壓操作范圍,以實現動態電壓調節設計來達成最佳的功耗∕性能。

●相較于 N22 解決方案,即將推出的 N6e 解決方案可提供約 4.9 倍的邏輯密度,并可降低超過 70%的功耗,為穿戴式設備提供極具吸引力的解決方案。

●臺積電最先進的 eNVM 技術已經發展到了基于 16/12 納米的鰭式場效應晶體管(FinFET)技術,令客戶能夠從 FinFET 晶體管架構的優秀性能中獲益。

●由于傳統的浮閘式 eNVM 或 ESF3 技術越來越復雜臺積電還大量投資于RRAM 和 MRAM 等新的嵌入式存儲器技術。

這兩種新技術都已經取得了成果,正在 22 納米和 40 納米上投產。

臺積電正在計劃開發 6 納米 eNVM 技術。

RRAM:已經于 2022 年第一季開始生產 40/28/22 納米的 RRAM。

●臺積電的 28 納米 RRAM 進展順利,具備可靠效能,適于汽車應用。

●臺積電正在開發下一代的 12 納米 RRAM,預計在 2024 年第一季就緒。

MRAM:2020 年開始生產的 22 納米 MRAM 主要用于物聯網應用,現在,臺積電正在與客戶合作將 MRAM 技術用于未來的汽車應用,并預計在 2023 年第二季取得 Grade 1 汽車等級認證。

CMOS 影像傳感器

●雖然智能手機的相機模組一直是互補式金屬氧化物半導體(CMOS)影像感測技術的主要驅動力,但臺積公司預計車用相機將推動下一波 CMOS 影像感測器(CIS)的增長。

●為了滿足未來感測器的需求,實現更高品質且更智能的感測,臺積電一直致力于研究多晶圓堆疊解決方案,以展示新的感測器架構,例如堆疊像素感測器、最小體積的全域快門感測器、基于事件的 RGB 融合感測器,以及具有集成存儲器的 AI 感測器。

顯示器

●在 5G、人工智能和 AR/VR 等技術驅動下,臺積電正致力于為許多新應用提供更高的分辨率和更低的功耗。

●下一代高階 OLED 面板將需要更多的數字邏輯和靜態隨機存取存儲器(SRAM)內容,以及更快的幀率,為了滿足此類需求,臺積公司正在將其高壓(HV)技術導入到 28 奈納米的產品中,以實現更好的能源效率和更高的靜態隨機存取存儲密度。

●臺積電領先的 μDisplay on silicon 技術可以提供高達 10 倍的像素密度,以實現如 AR 和 VR 中使用的近眼顯示器所需之更高分辨率。

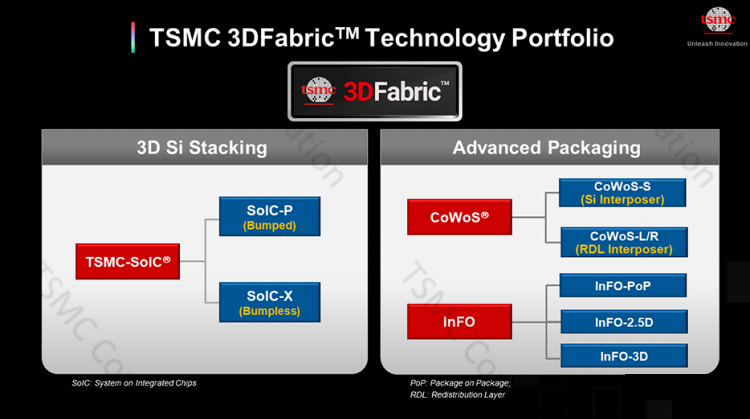

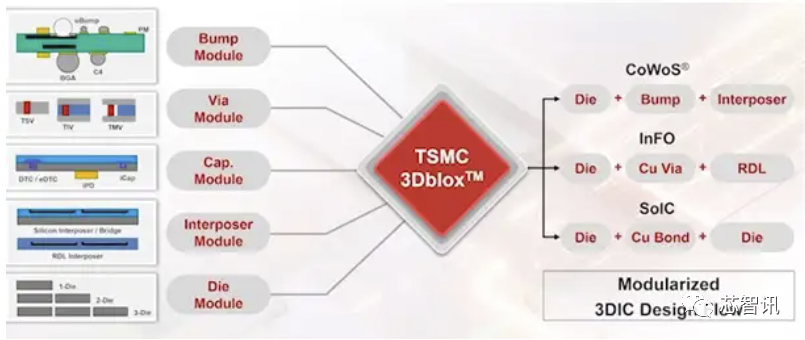

三、先進封裝技術:TSMC 3DFabric

為了進一步發展微縮技術,以在單芯片片上系統(monolithic SoCs)中實現更小且更優異的晶體管,臺積電還在開發 3DFabric 技術,發揮異質整合的優勢,將系統中的晶體管數量提高5倍,甚至更多。

臺積電3DFabric 系統整合技術包括各種先進的 3D 芯片堆疊和先進封裝技術,以支持廣泛的下一代產品:在 3D 芯片堆疊方面,臺積電在系統整合芯片(TSMC-SoIC)技術家族中加入微凸塊的 SoIC-P,以支持更具成本敏感度的應用。

2.5D CoWoS 平臺得以實現先進邏輯和高頻寬記憶體的整合,適用于人工智能、機器學習和數據中心等 HPC 應用;整合型扇出層疊封裝技術(InFOPoP)和 InFO-3D 支持移動應用,InFO-2.5D 則支持 HPC 小芯片整合。

基于堆疊芯片技術的系統整合芯片(SoIC)現可被整合于整合型扇出(InFO)或 CoWoS 封裝中,以實現最終系統整合。

1、CoWoS 家族

●主要針對需要整合先進邏輯和高帶寬存儲器的 HPC 應用。臺積電公司已經支持超過 25 個客戶的 140 多種 CoWoS 產品。

●所有 CoWoS 解決方案的中介層面積均在增加,以便整合更多先進芯片和高帶寬存儲器的堆疊,以滿足更高的性能需求。

●臺積電正在開發具有高達 6 個光罩尺寸(約 5,000 平方毫米)重布線層(RDL)中介層的 CoWoS 解決方案,能夠容納 12 個高帶寬存儲器堆疊。

具體來說,CoWoS已經擴展到提供三種不同的轉接板技術(CoWoS中的“晶圓”):

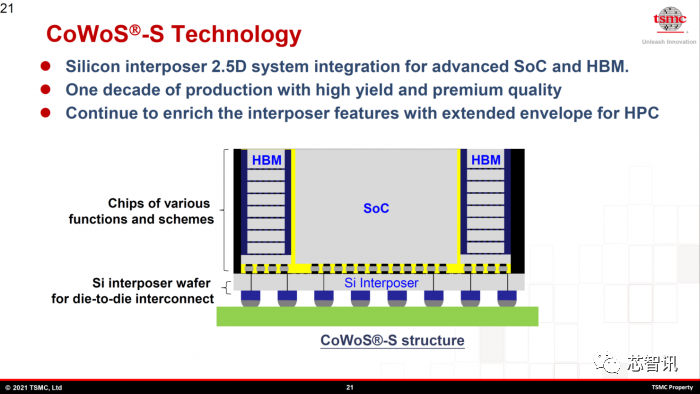

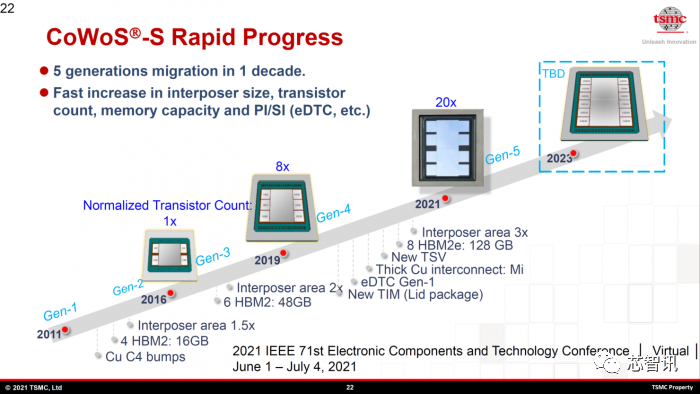

①CoWoS-S

●采用硅中介層,基于現有硅片光刻和再分布層的加工

●自2012年開始批量生產,迄今為止為已向20多家客戶提供了>100種產品

●轉接板集成了嵌入式“溝槽”電容器

●目前最新的第五代CoWoS-S封裝技術,將增加 3 倍的中介層面積、8 個 HBM2e 堆棧(容量高達 128 GB)、全新的硅通孔(TSV)解決方案、厚 CU 互連、第一代的eDTC1100(1100nF/mm2)、以及新的 TIM(Lid 封裝)方案。

根據官方的數據,臺積電第 5 代 CoWoS-S封裝技術,有望將晶體管數量翻至第 3 代封裝解決方案的 20 倍。

②CoWoS-R

●使用有機轉接板以降低成本

●多達 6 個互連的再分布層,2um/2um L/S

●4倍最大光罩尺寸,支持一個 SoC,在 55mmX55mm 封裝中具有 2 個 HBM2 堆棧;最新開發中的方案擁有 2.1 倍最大光罩尺寸,支持2 個 SoC 和 2HBM2 采用 85mmX85mm 封裝

③CoWoS-L

●使用插入有機轉接板中的小硅“橋”,用于相鄰芯片邊緣之間的高密度互連(0.4um/0.4um L/S 間距)

●2023年將會推出擁有2倍最大光罩尺寸大小,支持 2 個 SoC 和 6 個 HBM2 堆棧的方案;2024年將推出4倍最大光罩尺寸,可支持 12 個 HBM3 堆棧的方案。

臺積電強調,他們正在與 HBM 標準小組合作,共同制定 CoWoS 實施的 HBM3 互連要求的物理配置。

HBM3 標準似乎已經確定了以下堆棧定義:4GB(帶 4 個 8Gb 芯片)到 64GB(16 個 32Gb 芯片)的容量;1024 位信號接口;高達 819GBps 帶寬。這些即將推出的具有多個 HBM3 堆棧的 CoWoS 配置將提供巨大的內存容量和帶寬。

此外,由于預計即將推出的CoWoS設計將具有更大的功耗,臺積電正在研究適當的冷卻解決方案,包括改進芯片和封裝之間的熱界面材料(TIM),以及從空氣冷卻過渡到浸入式冷卻。

2、InFO

在臨時載體上精確(面朝下)放置后,芯片被封裝在環氧樹脂“晶圓”中。再分布互連層被添加到重建的晶圓表面。然后將封裝凸塊直接連接到再分配層。有InFO_PoP、InFO_oS和InFO_B三類。

①InFO_PoP

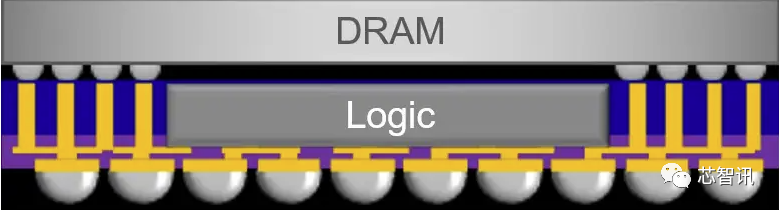

如下圖所示,InFO_PoP表示封裝對封裝配置,專注于DRAM封裝與基本邏輯芯片的集成。DRAM頂部芯片上的凸塊利用貫穿InFO過孔(TIV)到達重新分配層。

InFO_PoP主要用于移動平臺,自 2016 年以來,InFO_PoP出貨量超過 12 億臺。

InFO_PoP存在的一個問題是,目前DRAM封裝是定制設計,只能在臺積電制造。不過,在開發中的還有另一種InFO_B方案,其中在頂部添加了現有的(LPDDR)DRAM封裝,并且組件由外部合同制造商提供。

臺積電表示,在移動應用方面,InFO PoP 自 2016 年開始量產并運用于高端移動設備,可以在更小的封裝規格中容納更大、更厚的系統級芯片(SoC)。

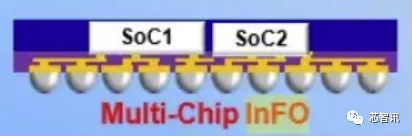

②InFO_oS

InFO_oS(基板上)可以封裝多個芯片,再分布層及其微凸起連接到帶有TSV的基板。目前,InFO_oS投產已達5年以上,專注于HPC客戶。

基板上有 5 個 RDL 層,2um/2um L/S

該基板可實現較大的封裝尺寸,目前為110mm X 110mm,并計劃實現更大的尺寸

擁有130um C4 凸塊間距

③InFO_M

InFO_M是InFO_oS的替代方案,具有多個封裝芯片和再分布層,無需額外的基板+ TSV(<500mm2封裝,于2022年下半年投產)。

臺積電表示,在 HPC 應用方面,無基板的 InFO_M 支持高達 500 平方毫米的小芯片整合,適用于對外型尺寸敏感度較高的應用。

3、3D 芯片堆疊技術

臺積電更先進的垂直芯片堆疊3D拓撲封裝系列被稱為“系統級集成芯片”(SoIC)。它利用芯片之間的直接銅鍵合,具有優秀的間距。

SoIC有兩種產品——“wafer-on-wafer”(WOW)和“chip-on-wafer”(COW)。WOW拓撲在晶圓上集成了復雜的SoC芯片,提供深溝槽電容(DTC)結構,以實現最佳去耦。更通用的 COW 拓撲堆疊多個 SoC 芯片。

下表顯示了符合SoIC組裝條件的工藝制程節點。

●SoIC-P 采用 18-25 微米間距微凸塊堆疊技術,主要針對如移動、物聯網等成本較為敏感的應用。

●SoIC-X 采用無凸塊堆疊技術,主要針對 HPC 應用。其芯片對晶圓堆疊方案具有 4.5 至 9 微米的鍵合間距,已在臺積公司的 N7 工藝技術中量產,用于HPC 應用。

●SoIC 堆疊芯片可以進一步整合到 CoWoS、InFo 或傳統倒裝芯片封裝,運用于客戶的最終產品。

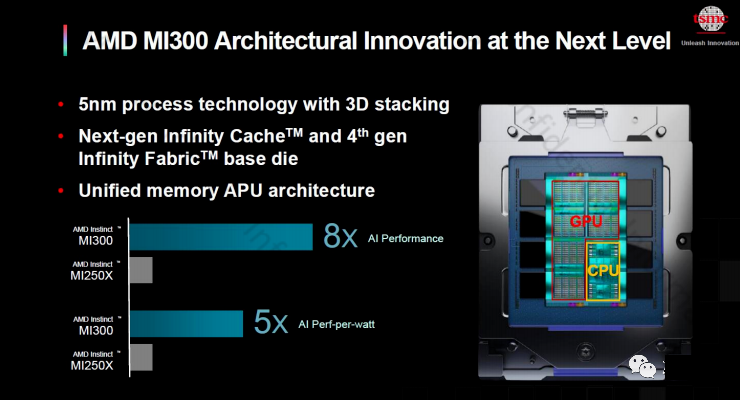

6月14日,處理器大廠AMD正式發布了新一代的面向AI及HPC領域的GPU產品——Instinct MI 300系列。其中,MI300X則是目前全球最強的生成式AI加速器,集成了高達1530億個晶體管,并支持高達 192 GB 的 HBM3內存,多項規格超越了英偉達(NVIDIA)最新發布的H100芯片。

臺積電表示,AMD Instinct MI 300X采用了臺積電 SoIC-X 技術將 N5 GPU 和 CPU 堆疊于底層芯片,并整合在CoWoS 封裝中,以滿足下一代百萬兆級(exa-scale)運算的需求,這也是臺積電3DFabric 技術推動 HPC 創新的絕佳案例。

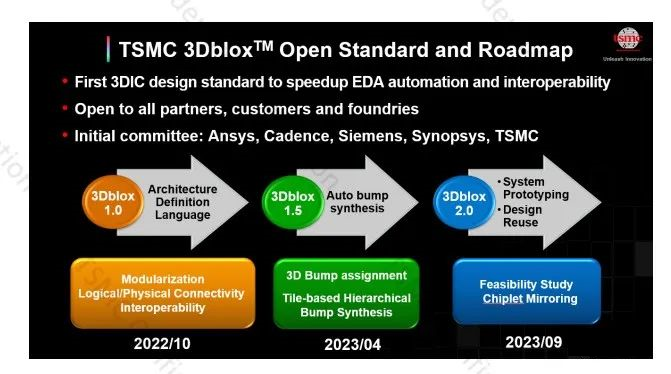

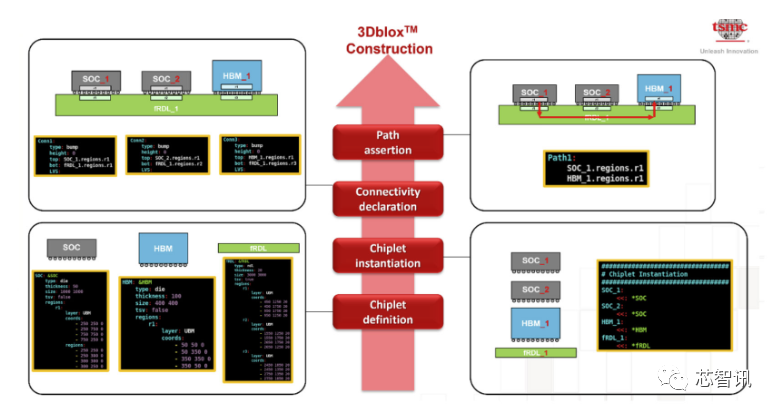

4、3DFabric 聯盟和 3Dblox 標準

在去年的開放創新平臺(Open Innovation Platform ,OIP)論壇上,臺積電宣布推出新的 3DFabric 聯盟,這是繼 IP 聯盟、電子設計自動化(EDA)聯盟、設計中心聯盟(DCA)、云端(Cloud)聯盟和價值鏈聯盟(VCA)之后的第六個 OIP聯盟,旨在促進下一代 HPC 和移動設計的生態系統合作,具體包括:

●提供 3Dblox 開放標準

●實現存儲器和臺積公司邏輯工藝之間的緊密協作

●將基板和測試合作伙伴導入生態系統

臺積電推出了最新版本的開放式標準設計語言 3Dblox 1.5,旨在降低 3D IC 設計的門檻。

四、卓越制造

臺積電在先進制程的缺陷密度(D0)和每百萬件產品缺陷數(DPPM)方面的領先地位,展現了其制造卓越性。

●N5 工藝復雜度遠高于 N7,但在相同階段,N5 的良率優化比 N7 更好。

●臺積電 N3 工藝技術在高度量產中的良率表現領先業界,其 D0 效能已經與 N5 同期的表現相當。

●臺積電 N7 和 N5 制程技術在包括智能手機、電腦和汽車等方面,展現了領先業界的 DPPM,我們相信 N3 的 DPPM 很快就能追上 N5 的表現。

●通過利用臺積電領先業界的 3DFabric 制造技術,客戶可以克服系統級設計復雜性的挑戰,加速產品創新。

●CoWoS 和 InFO 家族在量產后很快就達到了相當高的良率。

●SoIC 和先進封裝的整合良率將達到與 CoWoS 和 InFO 家族相同的水平。

五、產能布局

為了滿足客戶不斷增長的需求,臺積公司加快了晶圓廠拓展的腳步。

從 2017 年到 2019 年,臺積電平均每年進行大約 2 期的晶圓廠建設工程。

從 2020 年到 2023 年,臺積公司晶圓廠的平均建設進度大幅增加至每年約5 期的工程。

在過去兩年,臺積公司總共展開了 10 期的晶圓廠新建工程,包括在臺灣地區的 5 期晶圓廠工程與 2 期先進封裝廠工程,以及全球范圍內的 3 期晶圓廠工程。

●中國臺灣地區以外,28 納米及以下工藝產能在 2024 年將比 2020 年增加 3 倍。在中國臺灣地區,臺積電 N3 制程量產的基地在南科 18 廠;此外,臺積電正在為N2 制程的新晶圓廠進行準備。

●在中國大陸,臺積電2002年在上海松江設立8吋晶圓廠,并于2016年在南京設12吋晶圓廠和一座設計服務中心。目前,南京廠新 1 期的 28 納米制程擴產已于去年量產。

●在美國,臺積電正在亞利桑那州建造 2 期晶圓廠,總投資400億美元。目前第一期已經開始移入設備,第二期正在興建中。

●在日本,臺積電正在熊本興建一座晶圓廠,計劃總投資86億美元,預計在2023 年 9 月完工,2024 年底開始量產16 納米和 28 納米技術。今年1月,臺積電對外表示,考慮在日本興建第二座晶圓廠。在6月6日的股東會上,臺積電董事長劉德音首度透露評估中的日本二廠可能仍會建在熊本縣,會設在日本一廠附近,并且仍將面向成熟制程。

●在德國,臺積電正考慮在德國建一座晶圓廠,目前對于德國建廠的可能性仍在談判當中,但在 8 月之前不會做出決定。

據此前彭博社的報道顯示,臺積電正在與合作伙伴討論,計劃在爭取到《歐洲芯片法案》的補助支持的情況下,在2023年8月份的董事會上批準赴德國建立晶圓廠計劃。預計將投資最高將接近100億歐元,具體落腳點可能是在德國薩克森州。一旦臺積電決定在德國建廠,那么這將是臺積電在歐洲的首座晶圓廠。因為歐洲汽車工業的需求,該座晶圓廠預計將會以生產車用 MCU 需求的28nm成熟制程開始。

臺積電董事長劉德音曾表示,如果在德國設廠,原則上還是希望能夠維持獨資,不過,如果客戶希望能擁有部分股份,將會讓其小額持股,臺積電還是會持有大部分股權,希望能自由調配產能,避免以后產能遭控制。

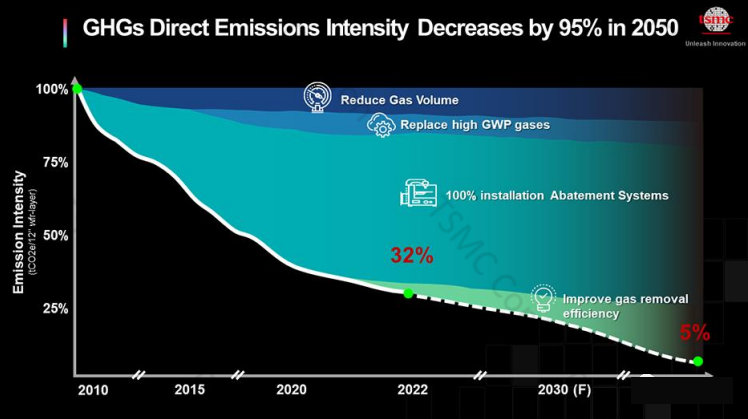

六、綠色制造

為了實現 2050 年凈零排放的目標,臺積電持續評估并投資各種減少溫室氣體排放的機會。

●到 2022 年,臺積電直接溫室氣體排放量已經較 2010 年降低了 32%。

●此一成果是通過降低工藝氣體消耗、替換可能造成全球暖化的氣體、安裝現場廢氣處理設備,以及提高氣體去除效率等方式實現。

臺積電目標每個工藝技術于量產第五年時,生產能源效率提高一倍。

●N7 制程技術的生產能源效率在量產后第五年提高了 2.5 倍。

●臺積電預計到 2024 年,N5 制程技術的生產能源效率將提高 2.5 倍。

去年,臺積電在臺灣地區南部建立了第一座再生水廠,每日供水量 5,000 公噸,時至今日,該再生水廠每日供水量達 20,000 公噸。

●到 2030 年,臺積公司的每生產單位自來水消耗量將降至 2020 年的 60%。

編輯:黃飛

-

mcu

+關注

關注

146文章

17123瀏覽量

350995 -

臺積電

+關注

關注

44文章

5632瀏覽量

166414 -

射頻技術

+關注

關注

4文章

147瀏覽量

35954 -

5G

+關注

關注

1354文章

48436瀏覽量

563971 -

先進制程

+關注

關注

0文章

82瀏覽量

8421

原文標題:臺積電上海技術論壇到底講了些什么?

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

預計到2030年全球半導體市場將達到約1萬億美元

預計到2030年全球半導體市場將達到約1萬億美元

評論