很多小伙伴開始學習時序約束的時候第一個疑惑就是標題,有的人可能會疑惑很久。不明白時序約束是什么作用,更不明白怎么用。

FPGA內部結構=LUT+觸發器+走線+嵌入式模塊(RAM,乘法器等)。下圖大致描述了它的抽象結構。

以上公式告訴我們:信號是通過走線和各個模塊產生連接。然后信號通過走線必然有延遲,有人認為電信是光速走線延時應該很短,可以忽略(全局時鐘線的延時在時序緊張的情況下是不可忽略的),然而走線延遲可能超過你的想像。

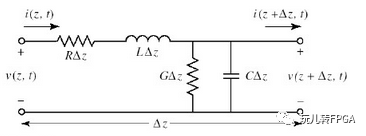

1.電信號在走線槽里面傳播并不是光速,走線上有分布電感和地平面有分布電容,二者值越大,對電容充電時間越長,走線延遲越長,這寫參數自然由工藝和封裝來決定,和我們設計無關,但是卻對我們的設計方法產生重大影響,傳輸模型如下:

2.除了傳輸線模型的延時以外,走線本身會經過很多類似路由器的結構去改變走線方向,在資源緊張的情況下可能會走過多個路由,這也就是為什么FPGA內部走線會很繞的原因,經過多級路由的走線延時會大大增加,在時序報告里面也可以看到的走線延遲=傳輸線延遲+路由延遲。

3.如果設計里面組合邏輯很多那么信號就會經過多個LUT,這也會產生延遲,在時序報告里面可以看見組合邏輯延遲和邏輯級數這2個選項。

綜合以上3點,FPGA內部延時不可忽略!并且常常達到ns級!。

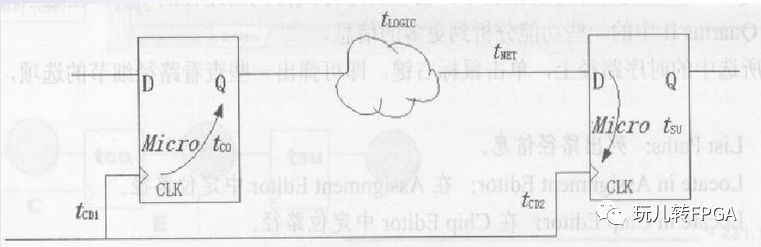

上圖為實際生成的數字電路模型,從中看出

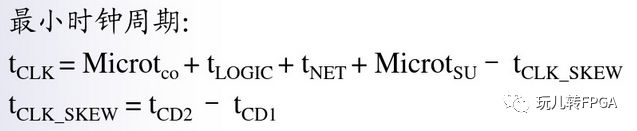

根據上圖公式,tnet和tlogic一旦增加,最小時鐘周期就會增加,也就意味著系統可以跑的最高頻率會下降。

那么編譯器怎么知道哪個是你的時鐘,你的主時鐘需要跑多少MHZ呢?如果編譯器設計高了,會編譯時間增長甚至報錯,低了會導致實際上板產生競爭冒險,從而導致錯誤。所以為了避免以上問題,我們需要高速編譯器這個時鐘到底要多快,還有,相位關系,占空比。這樣編譯器才能根據我們的需求去對比延時所算出來會不會競爭冒險。所有的時序約束都是要告訴編譯器,我的時鐘和數據要滿足怎樣的關系,然后交給編譯器去計算最糟糕的情況下能不能滿足條件,還差多少ns就會不滿足條件。

所以,為了告訴編譯器時鐘參數就有了

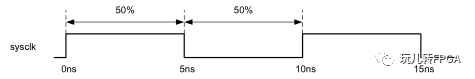

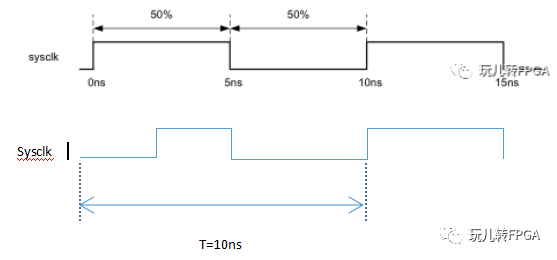

create_clock -name clk -period 10 [get_ports sysclk],這句xdc命令告訴編譯器,時鐘clk,從sysclk(get ports 后面攝取的是頂層要分配引腳的物理引腳,get pins后面攝取的是生成的某個寄存器或者器件的引腳,get nets攝取的是里面生成的某根線)這個引腳輸入,時鐘周期是10ns,由于相位和占空比未聲明,所以初相位為0,占空比為50%。如下圖:

如果想調節初相位90°和占空比25%:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports sysclk]

這里-waveform {2.5 5}代表第一個跳變沿在第2.5ns處產生,第二個跳變沿在5ns處產生從而形成下圖的時鐘,這樣就可以把所有的相位和占空比關系都描述清除。

編譯器會根據時鐘sysclk的周期和相位,在整個sysclk時鐘域,計算延遲后對比sysclk和對應寄存器的數據端口進行對比,看是否滿會產生競爭冒險,不滿足的地方會報告出來。

-

嵌入式系統

+關注

關注

41文章

3683瀏覽量

131525 -

乘法器

+關注

關注

9文章

212瀏覽量

38003 -

觸發器

+關注

關注

14文章

2040瀏覽量

62204 -

LUT

+關注

關注

0文章

50瀏覽量

12860 -

FPGA系統

+關注

關注

0文章

10瀏覽量

7168

發布評論請先 登錄

VIVADO時序約束及STA基礎

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA中的時序約束設計

深入了解時序約束以及如何利用時序約束實現FPGA 設計的最優結果

FPGA時序約束簡介

評論