1. 進(jìn)制轉(zhuǎn)換

會(huì)算數(shù)值在二進(jìn)制、八進(jìn)制、十進(jìn)制以及十六進(jìn)制之間的任意轉(zhuǎn)換。

會(huì)算數(shù)值的正碼、反碼、補(bǔ)碼、BCD碼。

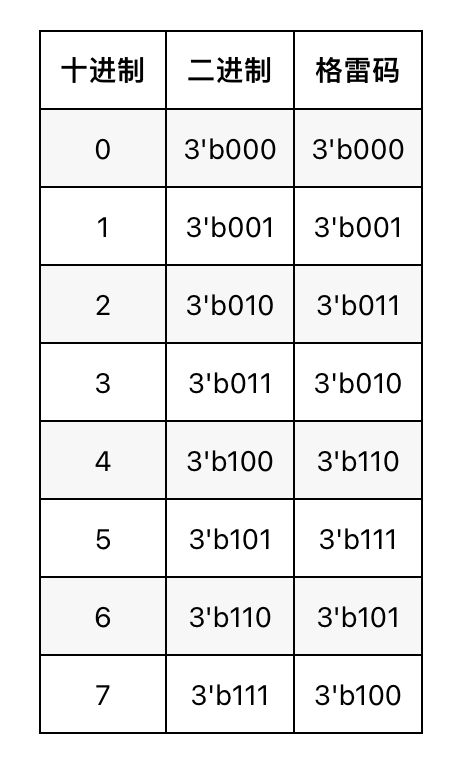

2. 什么是格雷碼(Gray code),它有什么優(yōu)點(diǎn)。

在一組二進(jìn)制編碼中,若任意兩個(gè)相鄰的數(shù)值還有1位二進(jìn)制數(shù)不同,則稱這種編碼為格雷碼,由于最大數(shù)和最小數(shù)之間也僅1位數(shù)不同,即”首尾相連”,因此又稱為循環(huán)碼或反射碼。比如下面對(duì)于0-7數(shù)值的格雷碼和二進(jìn)制碼關(guān)系:

在實(shí)際電路中,兩個(gè)二進(jìn)制數(shù)值之間如果有多位bit不一致,在發(fā)生轉(zhuǎn)換時(shí),由于每1bit的轉(zhuǎn)換時(shí)間不同,因此可能出現(xiàn)短暫的其它數(shù)值,在特定的情況下可能導(dǎo)致電路狀態(tài)錯(cuò)誤或輸入錯(cuò)誤,使用格雷碼可以避免這種錯(cuò)誤。格雷碼的另一個(gè)好處是相鄰數(shù)值的轉(zhuǎn)換,只需要變換1bit,因此可以減少動(dòng)態(tài)功耗。

3. 什么是奇偶校驗(yàn)位,以及它是如何算出來的?

奇偶校驗(yàn)位(Parity bit)是放在一個(gè)二進(jìn)制數(shù)值的最后1bit,它指示1個(gè)二進(jìn)制數(shù)中1的個(gè)數(shù)是偶數(shù)還是奇數(shù)。因此,有兩種類型:偶校驗(yàn)和奇校驗(yàn)。如果一組給定數(shù)據(jù)位中 1 的個(gè)數(shù)是奇數(shù),那么偶校驗(yàn)位就置為 1,從而使得總的 1 的個(gè)數(shù)是偶數(shù)。如果給定一組數(shù)據(jù)位中 1 的個(gè)數(shù)是偶數(shù),那么奇校驗(yàn)位就置為 1,使得總的1 的個(gè)數(shù)是奇數(shù)。

奇偶校驗(yàn)位可以通過將二進(jìn)制數(shù)據(jù)的所有bits進(jìn)行XOR運(yùn)算得到。它可以用于最簡單的錯(cuò)誤檢測(cè)機(jī)制。

舉個(gè)例子,有1個(gè)二進(jìn)制數(shù)為’b1011_0011, 可以看出這個(gè)二進(jìn)制數(shù)中1的個(gè)數(shù)為5個(gè)。如果采用奇校驗(yàn)的話,那么parity bit是0;如果使用偶校驗(yàn)的話,那么parity bit是1。

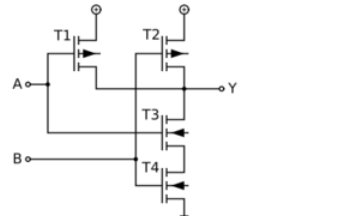

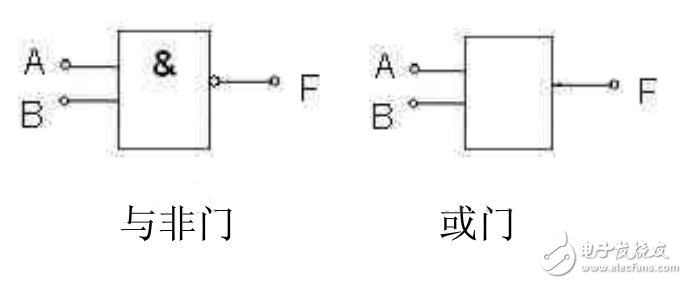

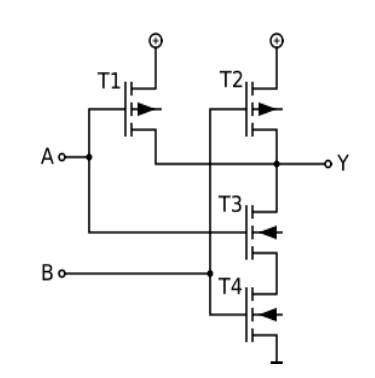

4. 如何使用兩輸入與非門(NAND gate)實(shí)現(xiàn)1個(gè)兩輸入的與門(AND gate),1個(gè)兩輸入的或門(OR gate),1個(gè)單輸入的非門(NOT gate)?

我們先看與非門的邏輯表達(dá)式:Y=!(A&&B),其中A和B是與非門的兩個(gè)輸入,Y是輸出。

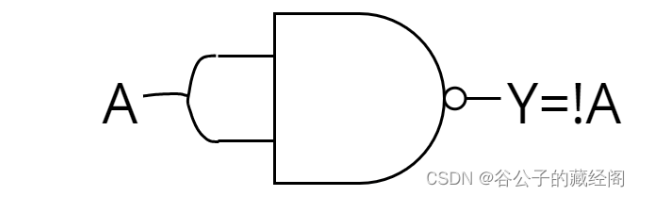

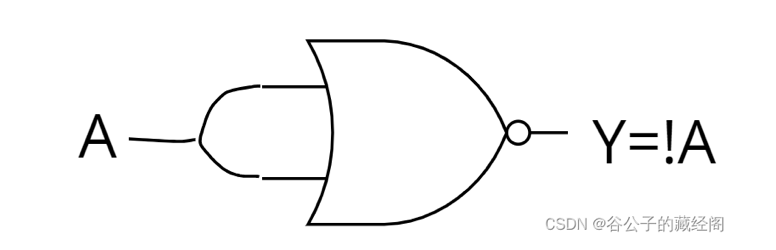

對(duì)于非門的邏輯表達(dá)式為:Y=!(A),可以讓與非門的輸入A和B連接在一起,就是非門了。電路圖如下:

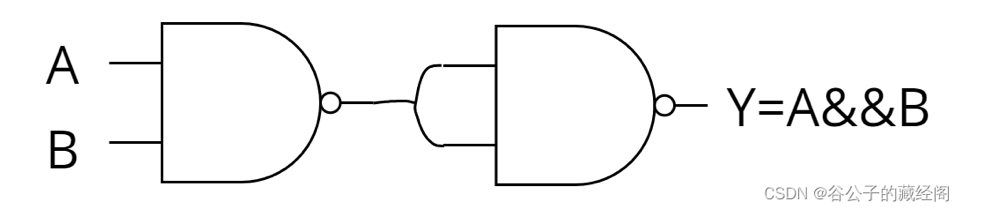

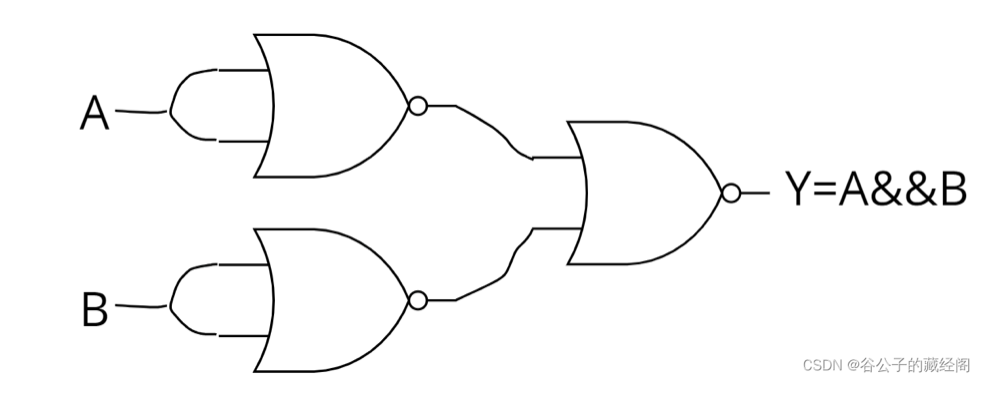

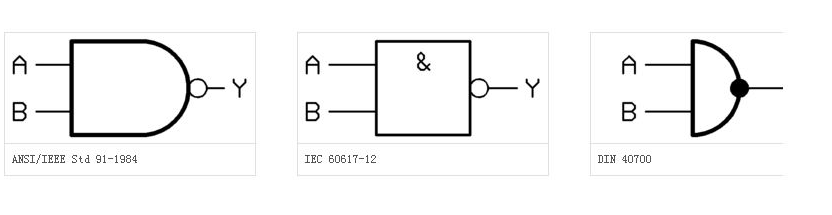

對(duì)于與門的邏輯表達(dá)式為:Y=A&&B,可以在與非門后面串上1個(gè)非門就可以了。電路圖如下:

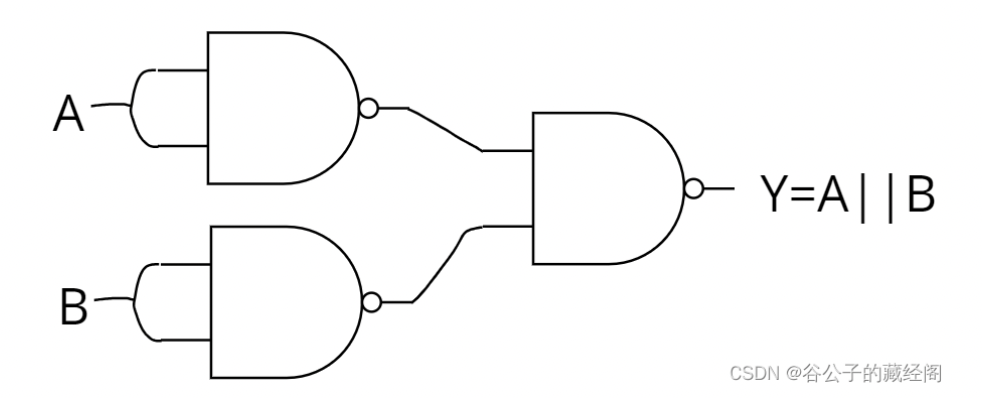

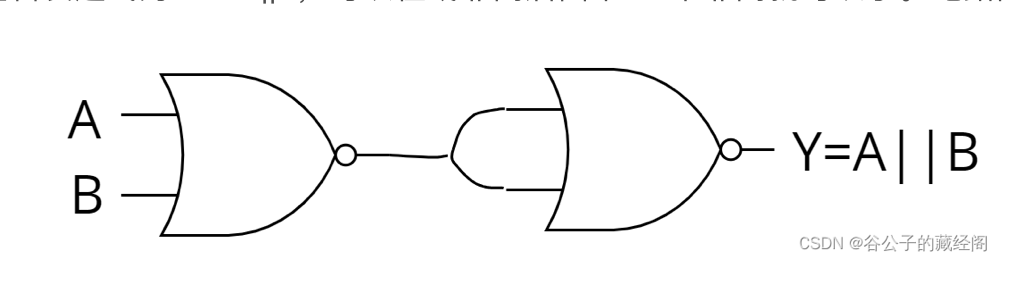

對(duì)于或門的邏輯表達(dá)式為:Y=A||B,對(duì)右邊進(jìn)行兩次取反并用德摩根定律得到:Y=!((!A)&&(!B)),因此需要3個(gè)與非門,電路圖如下:

5. 如何使用兩輸入或非門(NOR gate)實(shí)現(xiàn)1個(gè)兩輸入的與門(AND gate),1個(gè)兩輸入的或門(OR gate),1個(gè)單輸入的非門(NOT gate)?

我們先看或非門的邏輯表達(dá)式:Y=!(A||B),其中A和B是與非門的兩個(gè)輸入,Y是輸出。

對(duì)于非門的邏輯表達(dá)式為:Y=!(A),可以讓與非門的輸入A和B連接在一起,就是非門了。電路圖如下:

對(duì)于與門的邏輯表達(dá)式為:Y=A&&B,可以對(duì)右邊進(jìn)行兩次取反并用德摩根定律得到:Y=!(!A || !B),因此需要3個(gè)或非門,電路圖如下:

對(duì)于或門的邏輯表達(dá)式為:Y=A||B,可以在或非門后面串上1個(gè)非門就可以了。電路圖如下:

6. 如何使用2選1 選擇器(MUX)實(shí)現(xiàn):a. 單輸入非門;b. 兩輸入與門;c. 兩輸入或門;d. 兩輸入或非門;e. 兩輸入或非門;f. 兩輸入異或門;

這類題目的分析方法類似,我們就分析如何用2選1 MUX實(shí)現(xiàn)兩輸入與門,其余的讀者可以自行分析,有問題的話可以后臺(tái)留言討論。

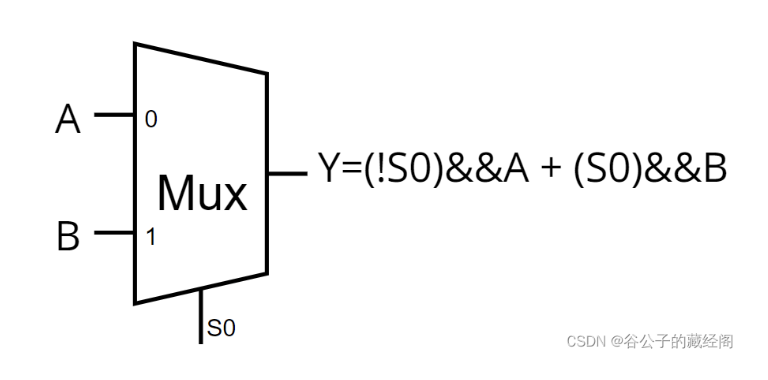

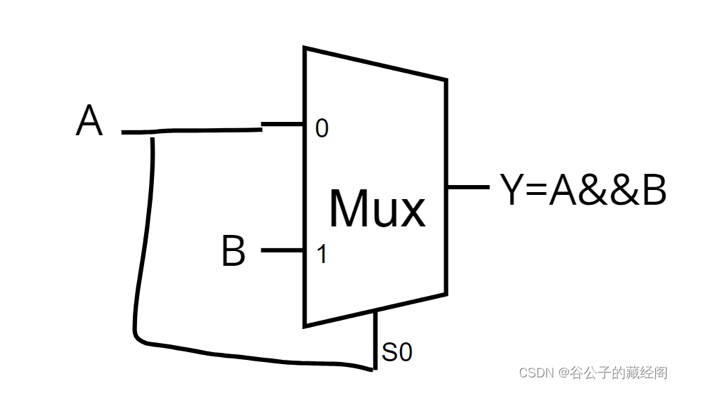

2選1 MUX是根據(jù)S0的值從兩輸入A和B中選擇1個(gè)送到輸出Y,它的邏輯表達(dá)式為:Y=(!S0)&&A + (S0)&&B。電路圖為:

然后兩輸入與門的邏輯表達(dá)式為:Y=A&&B,進(jìn)一步可變換為Y=!A&&A || A&&B,因此我們只要MUX的輸入A和S0連接起來,就是1個(gè)與門了。電路圖如下:

剩下的幾個(gè)門的轉(zhuǎn)換讀者自行分析吧,思路一樣,還蠻有意思的。

-

格雷碼

+關(guān)注

關(guān)注

2文章

34瀏覽量

13267 -

狀態(tài)機(jī)

+關(guān)注

關(guān)注

2文章

492瀏覽量

27779 -

BCD碼

+關(guān)注

關(guān)注

1文章

52瀏覽量

18441 -

多路選擇器

+關(guān)注

關(guān)注

1文章

22瀏覽量

6583

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

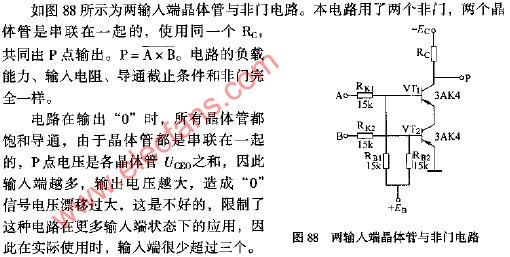

二輸入端與非門測(cè)量電路

為何我用Quartus II 13.1畫出的與非門是一個(gè)與門+一個(gè)非門

為什么與非門觸發(fā)器輸入信號(hào)要非

與非門的作用是什么 與非門的用法和特點(diǎn)

與非門實(shí)現(xiàn)非門功能方法介紹

兩個(gè)與非門電路的介紹

如何使用兩輸入與非門實(shí)現(xiàn)1個(gè)兩輸入的與門?

如何使用兩輸入與非門實(shí)現(xiàn)1個(gè)兩輸入的與門?

評(píng)論