手機射頻電路基本是平臺廠商已經決定了架構和相關配合的射頻器件,根據參考設計進行設計,重點在Layout和射頻匹配的調試。射頻參數很多,精湛的Layout技術和后期射頻調試完成后這些參數都會符合規范要求。

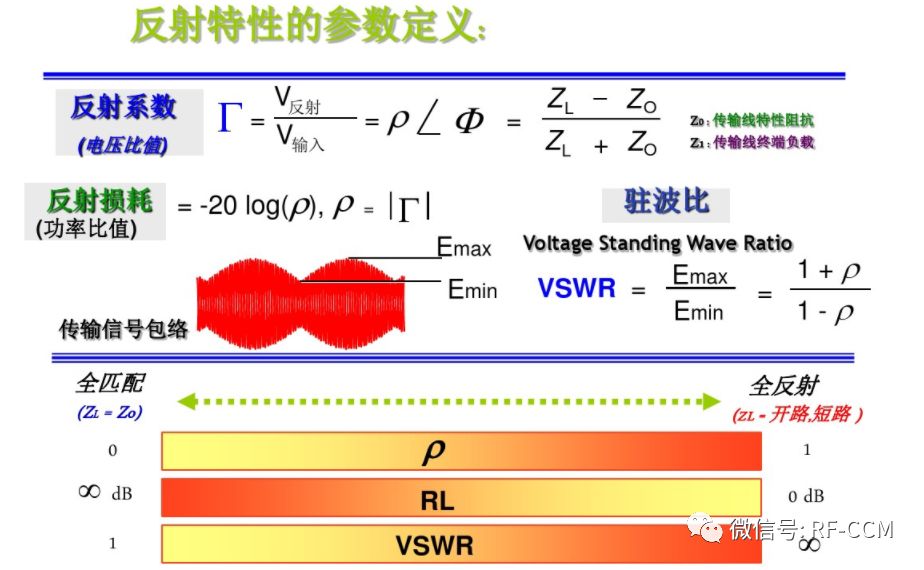

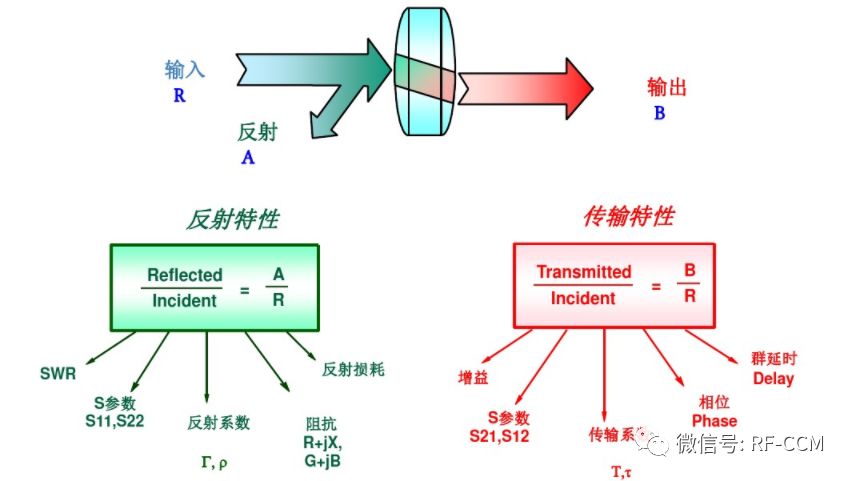

回波損耗(Return Loss): 入射功率/反射功率, 為dB數值

反射系數(Г): 反射電壓/入射電壓, 為標量

電壓駐波比(Voltage Standing Wave Ration): 波腹電壓/波節電壓 ,從能量傳輸的角度考慮, 理想的VSWR為 1:1 ,即此時為行波傳輸狀態,在傳輸線中,稱為阻抗匹配 ;最差時 VSWR無窮大,此時反射系數模為1,為純駐波狀態,稱為全反射,沒有能量傳輸 。

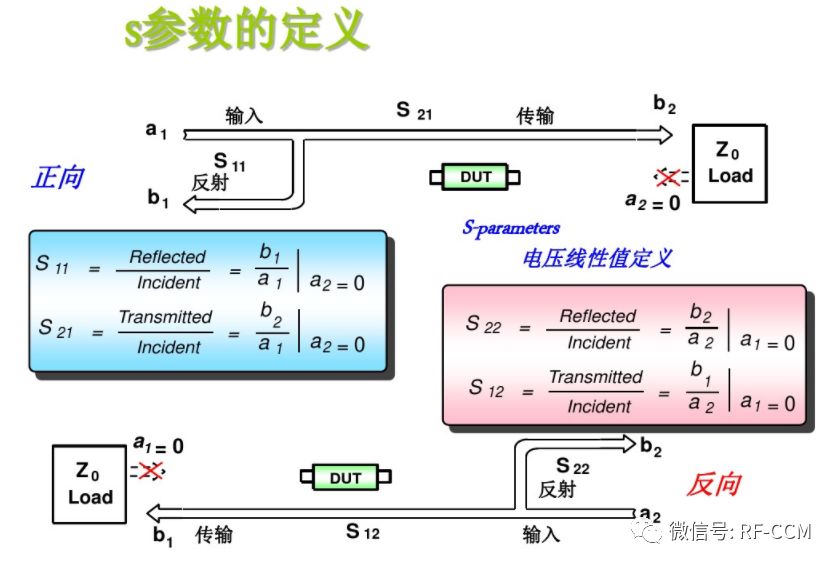

S參數

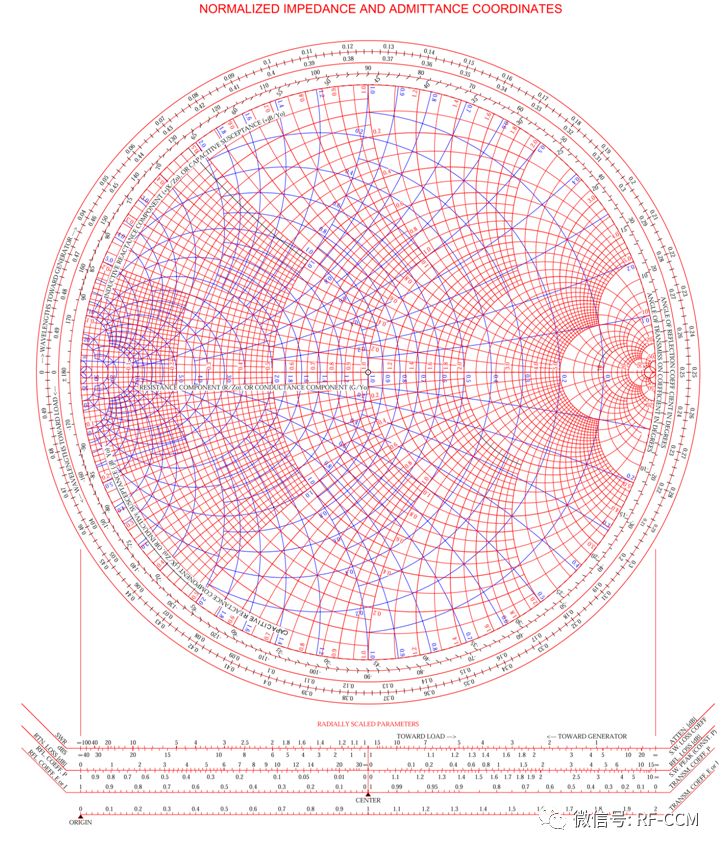

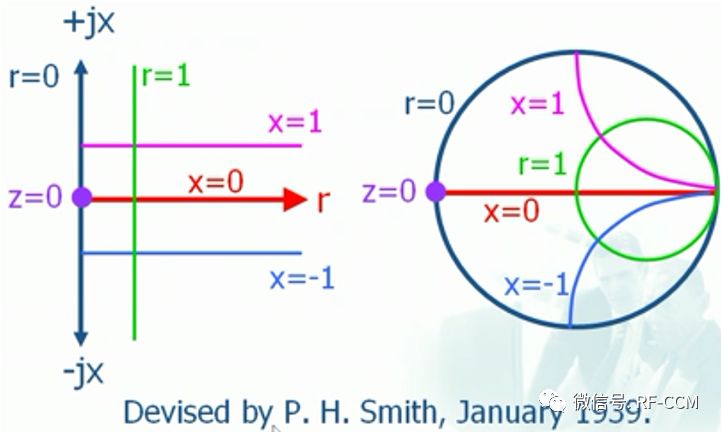

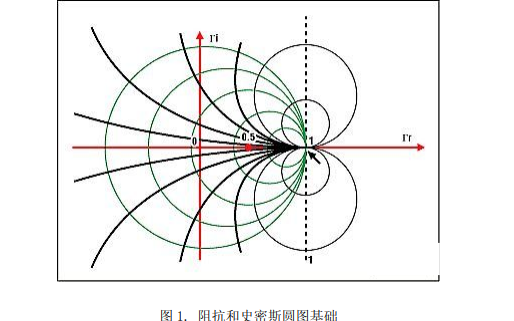

史密斯圓圖 ( Smith Chart)

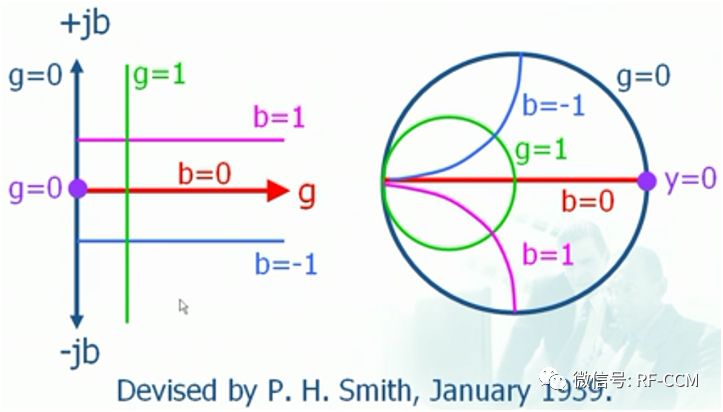

** Phillip Smith于1939年發明**

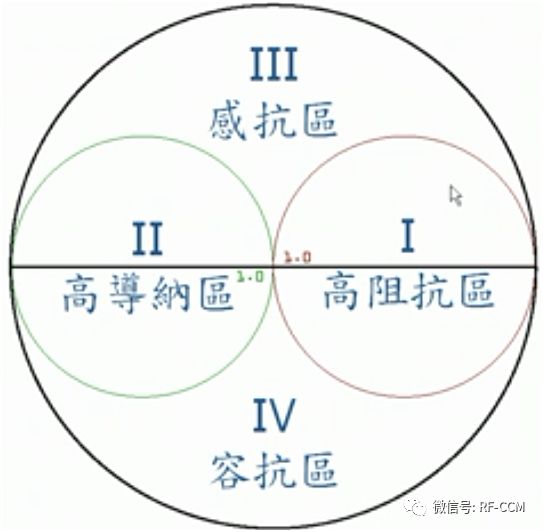

圖中分為藍色和紅色兩部分,其中:

藍色部分為導納圖,導納圖用的比較少,在并聯元件時候使用。

紅色部分為阻抗圖,在串聯元件時候使用,通常使用中主要以阻抗圖為主。

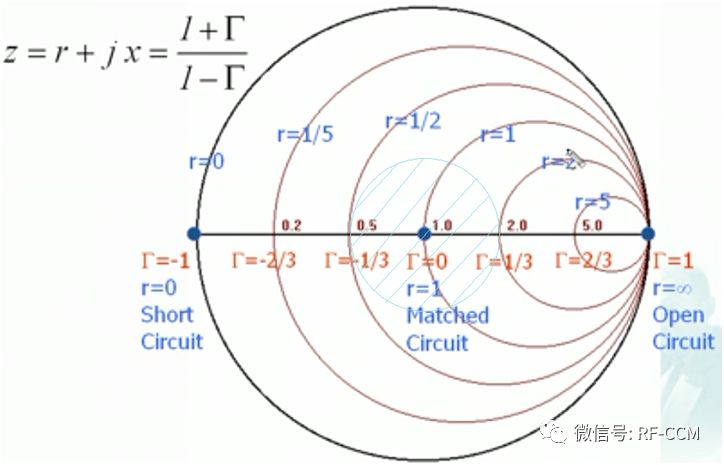

看到Smith Chart的時候的第一件事情是要想到反射系數

Smith Chart表示的就是反射系數。

Z=R+jX,射頻電路里面的阻抗是個復阻抗;

R的取值范圍為0~∞,j的取值范圍為-∞~+∞

那么對于Z來說就會有無限的組合,用圖表來表示是表示不完的,但是反射系數Γ****為 0< ** | Γ | < 1 ,即用一個半徑為1的圓即可表示完所有的反射系數,且一個阻抗對應唯一的一個反射系數** Γ ,只要在Smith Chart中找到一個 Γ ,就可以通過實部r與虛補j的相交點確認該點的阻抗。所以聰明的前輩Smith,就發明了以反射系數來表示的史密斯圓圖。

在SmithChart中使用歸一化后的阻抗(歸一化即Z/50=R/50+jx/50=z=r+jx),所以看到z=r+jx時候就要明白其表示歸一化后的阻抗。

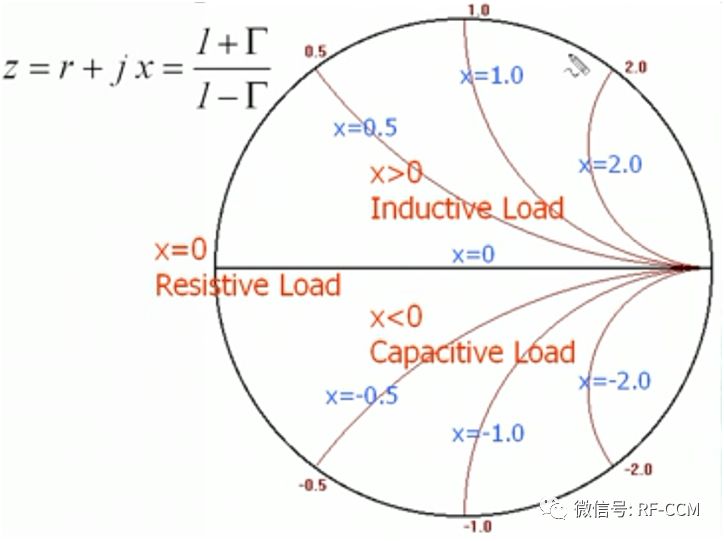

Smith Chart上半圓表示感性阻抗,下半圓表示容性阻抗。

匹配元件在Smith Chart上的移動方向

在設計匹配電路的時候,并聯元件在 導納圓上移動 ,串聯元件在 阻抗圓上移動 ,電感元件向上半圓移動,電容元件向下半圓移動。

Constant R Circle

上圖表示恒定阻抗的圓(實部)的阻抗為:

0.2=10Ω;0.5=25Ω;1.0=50Ω;2.0=100Ω;5.0=250Ω

利用這些恒定的阻抗圓可以估計附近的阻抗為多少,為不使用PC而評估阻抗提供便利。

最外圓 (黑色) 表示r=0即 Z=0+jx ,表示全反射,代表能量過不去,一定是有開路或短路的情況了,或者就是看過去的不是純電感就是純電容。這種情況在用VNA(矢量網絡分析儀)調試匹配時候,如果RF Cable沒有焊接好的時候經常碰到。

導納圖

在匹配使用到并聯元件時候使用導納圖進行匹配設計

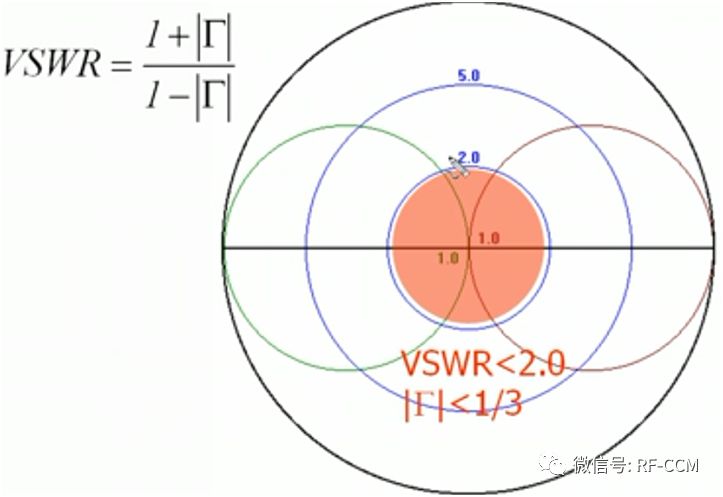

VSWRCircle

如何在實際中使用VSWR圓?

對RF設計的要求 VSWR < 2.0 , S11=1/3, 此即 Γ , 得到 中心圓部分 ,該圓中包含的部分就是符合 VSWR < 2.0 , S11=1/3的部分,這時候如果設計的band的所有點都落在該圓內的話就沒太大問題了。

在用VNA測試的時候怎么估計band的點是否落在這個圓內呢?

設定要測試的Start Freq和Stop Freq,通過調節匹配,將整個band的點拉到該圓即可,估計圓的大小時候參考恒定阻抗的圓中0.5,1.0,2.0三個點,以1.0為中心,過0.5和2.0做圓,該圓即為符合 VSWR < 2.0 , S11=1/3的圓,這樣就可不用PC而用心算來估計自己設計的RF電路是否符合要求。

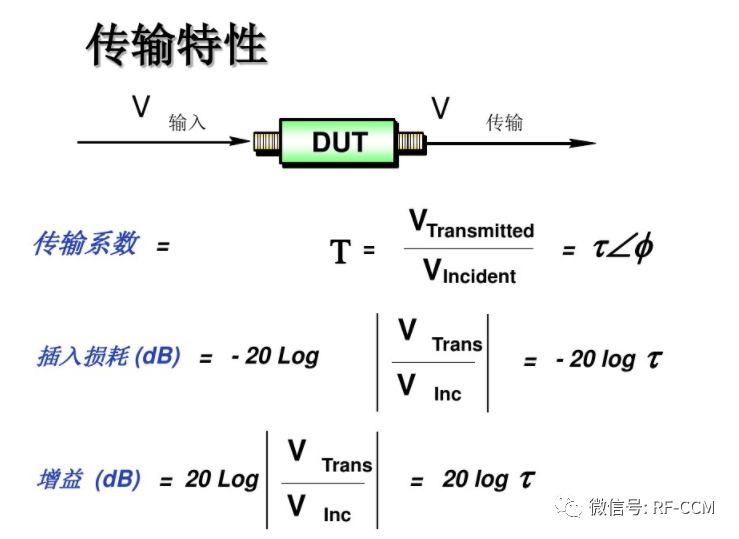

S21可以用來評估插損 (IL: Insertion Loss)的大小,就是“黑盒”的衰減。經驗值從PA到RF Jack大概是3.2左右,當然 越小越好 。

射頻電路要求

VSWR < 2.0

S11=1/3, 此即****Γ

S11ˊ(dB)=-9.54 ,通常要求為 -10 ,此即 RL, 將****Γ 做對數運算后 -20log(S11)=RL

相關公式:

Γ= (Z L -Z 0 )/(Z L +Z 0 **) **

** = (** | ** VSWR**** |** ** -1) / (** | ** VSWR**** |**** +1)**

VSWR=1+ | Γ | ** /1-** | Γ |

Z L =Z 0 *(1+Γ)/(1-Γ)

**Z0:特性阻抗(特征阻抗),RF的特征阻抗為50Ω **

歸一化阻抗:

**z=r+jx=1+Γ/1-Γ=Z/50** **(** **Z=R+jX** **)**

** Γ=Γr+jΓx**

** 注意Γ是個復數,而|Γ|是Γ的模,不要混淆。**

Four Matching Regions of Smith Chart

阻抗落在不同的區域,能選擇的匹配的方式就會受到限制。

感抗區和容抗區幾乎都是高感抗和高容抗的。

Matching Network

調試的一些規律

高阻抗區即地I區,需要并聯元件,即并聯電容。

低阻抗區(高導納區),即第II區需要串聯元件,即串聯電感。

看到阻抗的時候,可以拿這個阻抗和50Ω去比,大于50Ω或小于50Ω,通常就應該知道一開始的匹配元件應該是串還是并。

并聯電容阻抗變小,串聯電感阻抗變大。

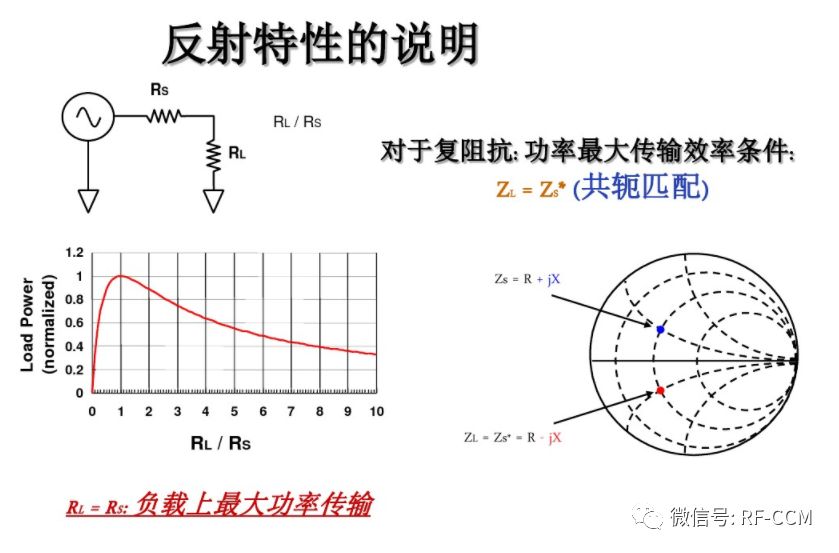

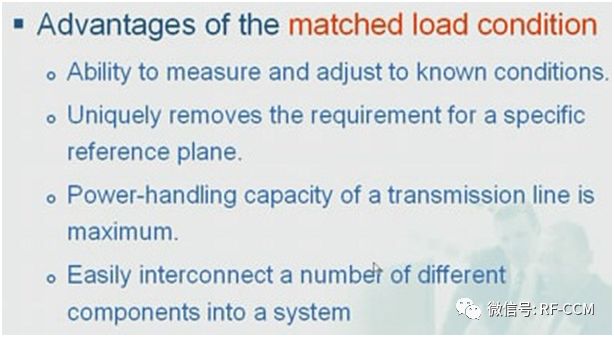

阻抗匹配實質就是使得復阻抗的實部相等,虛部對消。

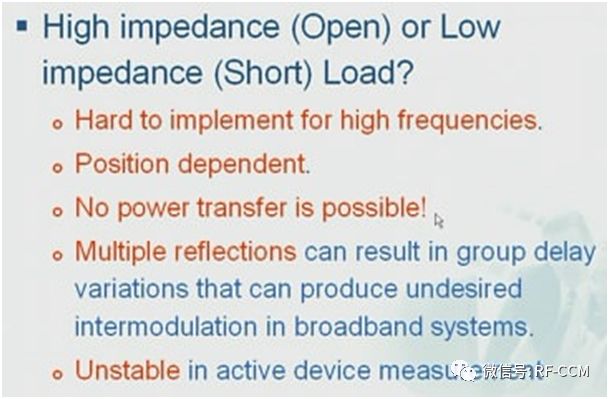

為什么要做阻抗匹配

對于傳輸線

Z 0 = √ L/C, 特性阻抗

Vp=1/ √ L/C ,相速

在傳輸線理論中若Δz≈0的話則可用KVL(基爾霍夫電壓定律)來計算電路特性,傳輸線方程就是基于Δz≈0時候的KVL推導出來的,那么什么是Δz≈0,模擬業界認為是<λ/20時候。通常仿真過程在等效電路的時候,每λ/20等效為一個LC。

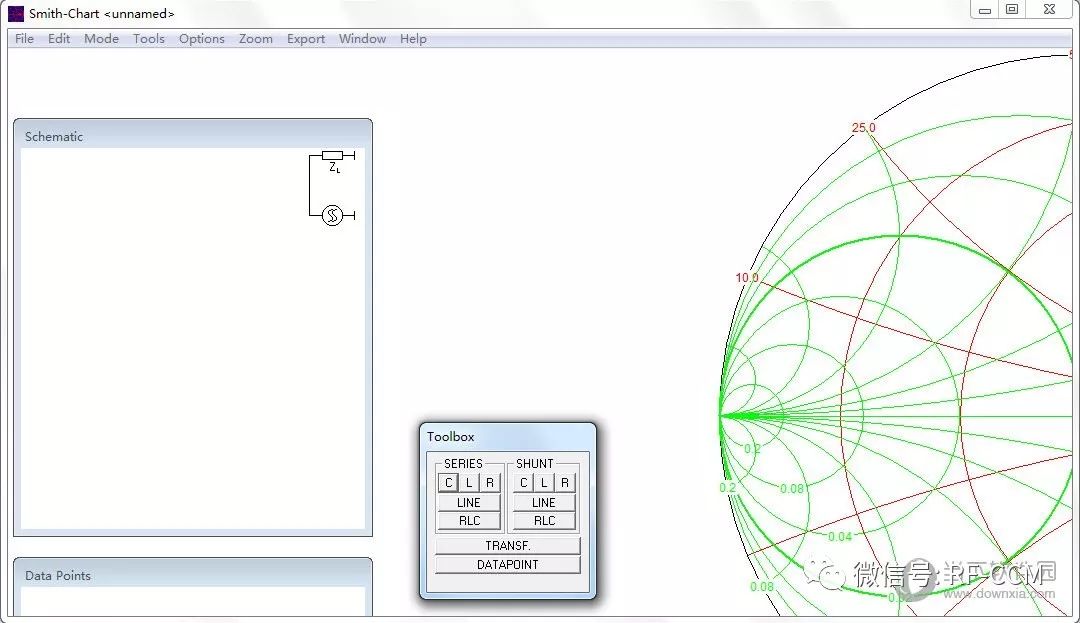

史密斯圓圖計算工具

調試匹配非常有用

這個工具使用的時候,加入的元件是并聯還是串聯,電容、電感大小,在圓圖上Z會有方向和步驟的進行移動。

電容或者電感決定了Z的移動方向,其大小決定了Z在圓圖上走過的距離。

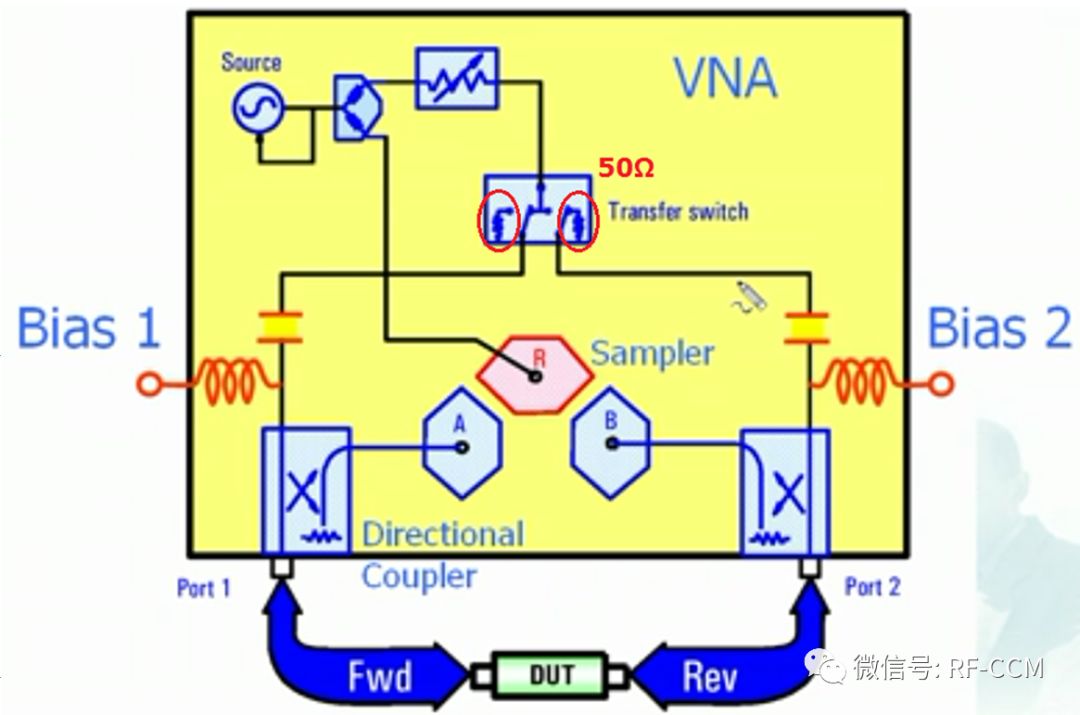

VNA(Vector Network Analyzer)簡介

VNA是一個發射和測量接收設備,用來發射信號和測量經過電路后的信號,其輸出是CW(Continue Wave連續波)信號,這就是導致為什么在WCDMA和CDMA電路用VNA調試后,有源測試時并不能總是得到與VNA調試結果完全相符的結果的原因,因VNA輸出是CW信號,所以電路處理的是CW信號,而實際有源情況是電路處理的是類噪聲信號,因此而產生偏差。其內部有50Ω點,在測試時候會讓相關端口處于50Ω匹配狀態,如下圖示為VNA簡圖。

在用VNA測試芯片阻抗的時候總是會有一個問題困擾,就是測試端口網絡S參數的前提是在測試某端口S參數的時候,其它端口需為50Ω匹配,不然不符合S參數的定義,且 芯片端口基本不會是50Ω的,實質是復阻抗形式,更多的時候表現為容性阻抗( 所以匹配中很多時候需要用到電感 ) 。

那么如何保證/確認在測試網絡某端口的時候,保證其它網絡端口為50Ω呢?對于微波系統來說,其本身就是按50Ω來設計的,系統某處已設計總有一個點是在50Ω的,所以可以將該系統50Ω之前的所有路徑及器件均視為“黑盒”,對整個“黑盒”進行S參數的測試,對這個“黑盒”進行匹配。

WCDMA信號由于采用直接序列擴頻,具有內在的類噪聲特性,信號波動劇烈,峰均比遠高于傳統模擬系統的穩定信號和一般的 非擴頻數字調制信號 (GSM 是非擴頻信號,所以峰均比較小,即信號較穩定,所以在用傳統網分測試時候效果好 ) ,而且 波動特性 ( 信號幅度概率分布 ) 與 基帶編碼 ( 碼道數量和組合 ) 有直接關系。而傳統網絡分析儀的激勵信號都是 CW 穩定信號, 可以反映器件的傳統靜態指標 (如用于器件篩選和維修診斷),但**無法反映器件在實際應用過程中通過真實**** WCDMA ** 信號所產生的質量變化 。所以用VNA調試完成后,需要在信令模式進行匹配的微調。

射頻環境主要是要在屏蔽房中完成射頻相關的工作,以防產生不必要的結果。

舉例如WLAN Rx測試時候如果在普通場合,儀器發1000個package給DUT,而DUT計算PER的時候的總數比1000多,這就是內部噪聲和外界干擾共同作用產生的結果,射頻環境和規范測試很重要。

-

VSWR

+關注

關注

0文章

60瀏覽量

15970 -

Layout

+關注

關注

14文章

403瀏覽量

61741 -

串聯電感

+關注

關注

0文章

29瀏覽量

8057 -

電壓駐波比

+關注

關注

0文章

34瀏覽量

7615 -

手機射頻電路

+關注

關注

1文章

5瀏覽量

2040

發布評論請先 登錄

相關推薦

阻抗匹配與史密斯(Smith)圓圖:基本原理

應用史密斯圓圖工具進行阻抗匹配的實例[分享史密斯圓圖工具]

阻抗匹配與史密斯(Smith)圓圖:基本原理

利用史密斯圓圖進行RF阻抗匹配設計

阻抗匹配與史密斯圓圖

史密斯圓圖的的天線阻抗匹配解決方案

阻抗匹配與史密斯圓圖的基本原理資料免費下載

史密斯圓圖與阻抗匹配的調試

史密斯圓圖與阻抗匹配的調試

評論