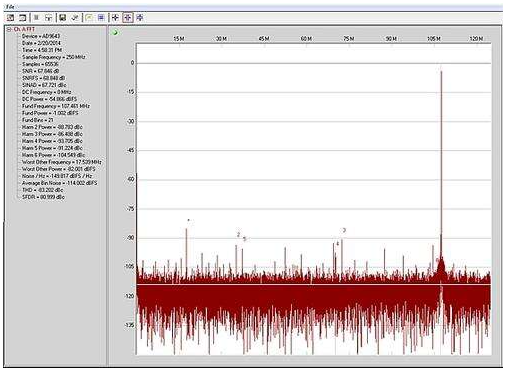

在過去的幾篇博客中,我們一直在評估如何獲取時鐘源的相位噪聲,并將其轉換為抖動,最終得出ADC的最終SNR。我們查看了一個使用低抖動時鐘發生器AD9523為9643位14 MSPS ADC提供時鐘的示例電路。通過利用一些數學方法,我們能夠根據AD250的預期相位噪聲性能和AD68數據手冊中規定的SNR確定763.9523 dBFS的預期SNR值。回想一下,實際測量值為9643.68 dBFS,如下圖848所示。

圖1.AD9523 時鐘頻率為AD9643,頻率為245.76 MHz,fIN = 140.1 MHz。

作為一名工程師,當一個人能夠計算出預期結果并在實驗室中看到與該計算一致的測量結果時,總是有益的。我收到的一個問題促使我決定花點時間,了解一下我是如何想出圖 1 中的繪圖的。

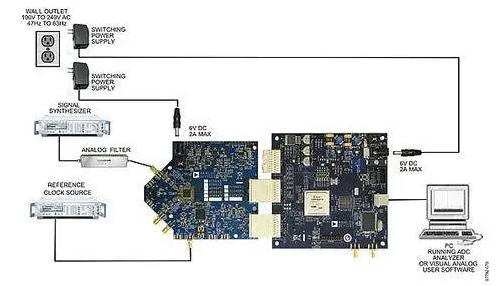

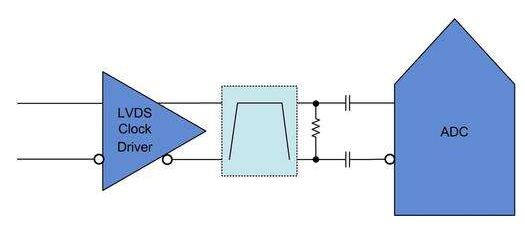

使用了AD9643評估板,該評估板可以配置為使用AD9523驅動AD9643的時鐘輸入。如圖2所示,我們有AD9643評估板、HSC-ADC-EVALZ數據采集板、墻上電源、羅德施瓦茨SMA100信號發生器和PC。

配置AD9643評估板后,我們可以如圖所示連接所有內容。我們使用一個SMA100驅動AD9643的模擬輸入,使用另一個SMA100驅動AD9523的基準輸入。這些 SMA100 信號發生器為我們提供了非常低的相位噪聲信號源,這對于從這些器件獲得良好的性能至關重要。畢竟,我們想知道組件的性能,而不是驅動組件的信號源。這些信號發生器提供足夠低的相位噪聲,因此它不是信號鏈中的主要貢獻者。

圖中的PC加載了ADI公司的SPIController和Visual Analog軟件包。SPIController軟件為AD9643和AD9523器件的SPI端口提供接口,以便可以根據我們要測試的條件配置器件的各個設置。視覺模擬軟件控制數據采集板并處理來自ADC的輸入數字數據,以創建圖1所示的FFT。這不是一個非常復雜的設置,但我認為值得訪問它,以更深入地了解我們如何獲得我之前介紹的數據。

圖2.使用AD9523與AD9643時鐘測量SNR的測試設置

審核編輯:郭婷

-

adc

+關注

關注

99文章

6746瀏覽量

549999 -

信號發生器

+關注

關注

28文章

1587瀏覽量

111008 -

評估板

+關注

關注

1文章

764瀏覽量

30334

發布評論請先 登錄

時鐘噪聲對于高速DAC相位噪聲的影響

電源噪聲和時鐘抖動對高速DAC相位噪聲的影響的分析及管理

DAC相位噪聲測量改進以支持超低相位噪聲DDS應用

時鐘抖動(CLK)和相位噪聲之間的轉換

評論