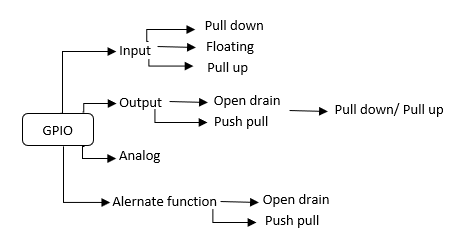

1. 數(shù)字輸入輸出的定義

數(shù)字輸入或輸出(英語(yǔ):Digital Input or Digital Input),又叫開關(guān)量輸入或輸出,只有通和斷二種狀態(tài),離散狀態(tài)。

常見的數(shù)字輸入有GPIO,GTA等

本文主要說(shuō)明GPIO

2. GPIO輸入主要電路結(jié)構(gòu)

施密特觸發(fā)器分TTL門電路、CMOS門電路和運(yùn)放比較器三種種分別說(shuō)明

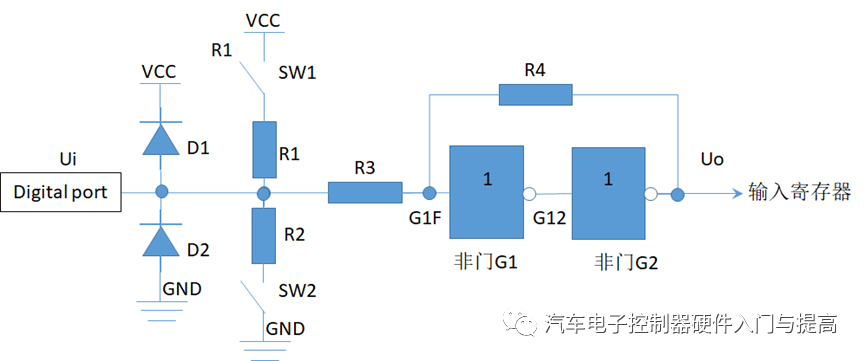

2.1.TTL施密特觸發(fā)器下的GPIO主要電路結(jié)構(gòu)

其中

1)R1,R2為內(nèi)部弱上拉或弱下拉,阻值很大,一般為100k以上;

2)D1,D2為嵌位二極管,可以嵌位到-V(D2)到VCC+V(D1)之間,如果選擇硅管二極管,可以嵌位到-0.7V~5.7V;

3)R3=100Kohm,R4=1000kohm

2.2.TTL施密特觸發(fā)器下的GPIO閾值計(jì)算

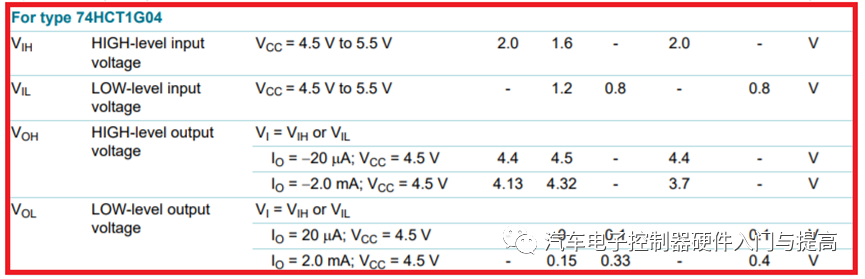

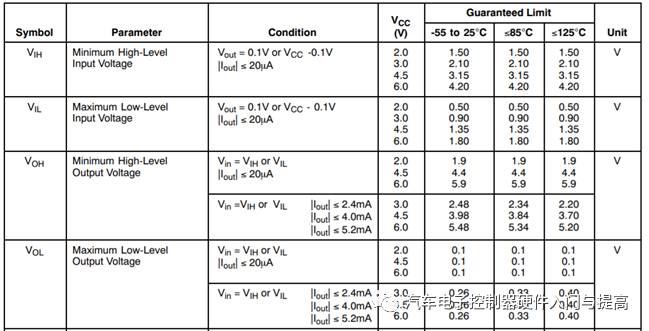

非門以74HCT1G04舉例,此處不討論R1,R2接入情況

1)當(dāng)外部信號(hào)Ui未接入時(shí),真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 懸空 | 0 | 1 | 0 |

| 電壓值 | 懸空 | 懸空 | 4.4V | 0.4V |

UG1F=Ui*R4/(R3+R4)

2)當(dāng)外部信號(hào)Ui輸入上升,UG1F>=UIH=2.0V時(shí),

Ui>=UG1F*(R3+R4)/R4=UIH*(R3+R4)/R4=2*(100+1000)/1000=2.2V

即VDIH=2.2V

假設(shè)Ui從0V升到4.2V

真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 1 | 1 | 0 | 1 |

| 電壓值 | 4.2V | 2.8V | 0.4V | 4.4V |

3)當(dāng)外部信號(hào)Ui輸入從5V下降時(shí),

(Uo-Ui)/(R3+R4)=(Uo-UG1F)/R4,即UG1F=(Ui*R4+Uo*R3)/(R3+R4)<=0.8V

Ui=

其中R3=100K,R4=1000K,Uo=4.4V,解得:Ui<=0.44V,即VDIL=0.44V

假設(shè)Ui從4.4V降到0.3V

真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 0 | 0 | 1 | 0 |

| 電壓值 | 0.3V | 0.67V | 4.4V | 0.4V |

經(jīng)過(guò)一段時(shí)間后,穩(wěn)定后的

UG1F=(UiR4+UoR3)/(R3+R4)=(0.310+0.41)/11=0.1V

真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 0 | 0 | 1 | 0 |

| 電壓值 | 0.3V | 0.1V | 4.4V | 0.4V |

綜上所述,VDIH=2.2V ,VDIL=0.44V

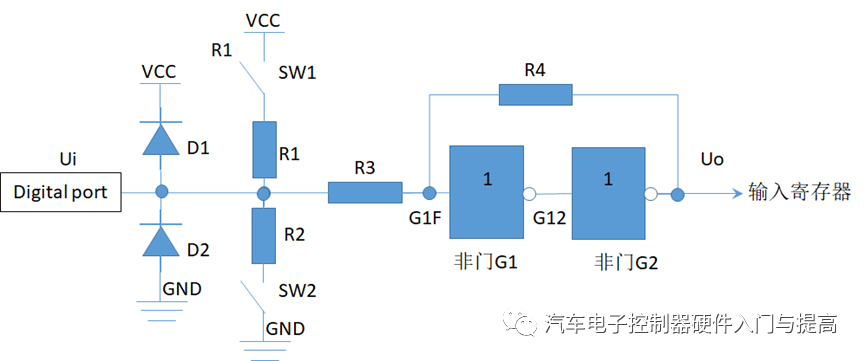

2.3.CMOS施密特觸發(fā)器下的GPIO主要電路結(jié)構(gòu)

其中

1)R1,R2為內(nèi)部弱上拉或弱下拉,阻值很大,一般為100k以上;

2)D1,D2為嵌位二極管,可以嵌位到-V(D2)到VCC+V(D1)之間,如果選擇硅管二極管,可以嵌位到-0.7V~5.7V;

3)R3=100Kohm,R4=3000kohm

2.4.CMOS施密特觸發(fā)器下的GPIO閾值計(jì)算

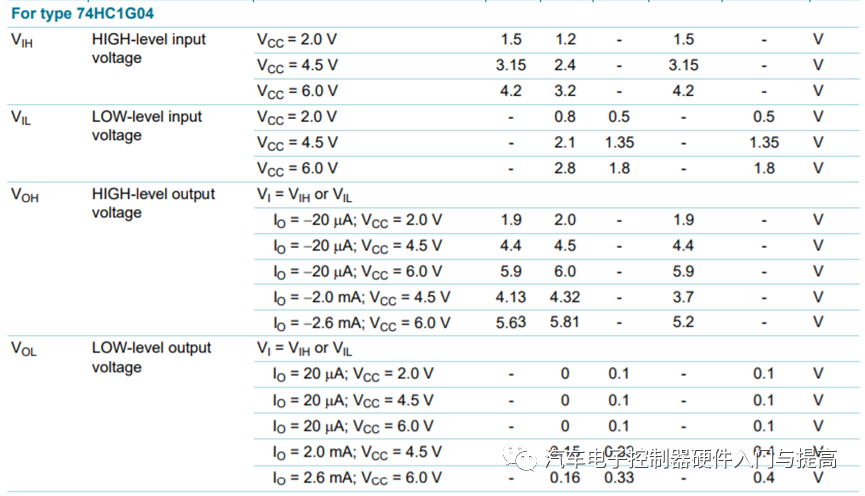

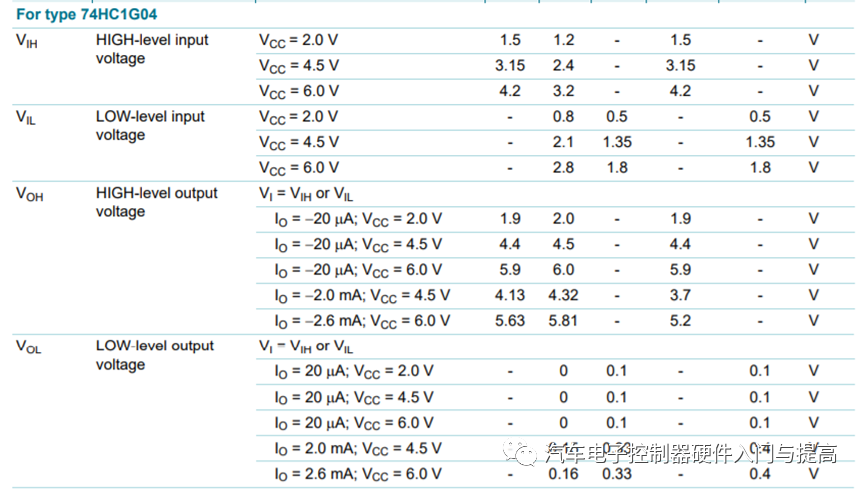

非門以74HC1G04舉例,此處不討論R1,R2接入情況

假設(shè)供電VCC=5V,那么UIH=3.5V,UIL=1.5V,VOH=4.5V,VOL=0.5V.

1)當(dāng)外部信號(hào)Ui未接入時(shí),真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 懸空 | 0 | 1 | 0 |

| 電壓值 | 懸空 | 懸空 | 4.5V | 0.5V |

UG1F=Ui*R4/(R3+R4)

2)當(dāng)外部信號(hào)Ui輸入上升,UG1F>=UIH=3.5V時(shí),

Ui>=UG1F*(R3+R4)/R4=UIH*(R3+R4)/R4=3.5*(100+3000)/3000=3.62V

即VDIH=3.62V

假設(shè)Ui從0V升到4.2V

真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 1 | 1 | 0 | 1 |

| 電壓值 | 4.2V | 3.62V | 0.5V | 4.5V |

3)當(dāng)外部信號(hào)Ui輸入從5V下降時(shí),

(Uo-Ui)/(R3+R4)=(Uo-UG1F)/R4,即UG1F=(Ui*R4+Uo*R3)/(R3+R4)<=0.5V

Ui=

其中R3=100K,R4=3000K,Uo=4.5V,解得:Ui<=0.37V,即VDIL=0.37V

假設(shè)Ui從4.2V降到0.2V

真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 0 | 0 | 1 | 0 |

| 電壓值 | 0.3V | 0.67V | 4.5V | 0.5V |

經(jīng)過(guò)一段時(shí)間后,穩(wěn)定后的

UG1F=(UiR4+UoR3)/(R3+R4)=(0.33000+0.5100)/3100=0.31V

真值表為以下

| 信號(hào) | Ui | UG1F | UG12 | Uo |

|---|---|---|---|---|

| 邏輯值 | 0 | 0 | 1 | 0 |

| 電壓值 | 0.3V | 0.31V | 4.5V | 0.5V |

綜上所述,VDIH=3.62V ,VDIL=0.37V

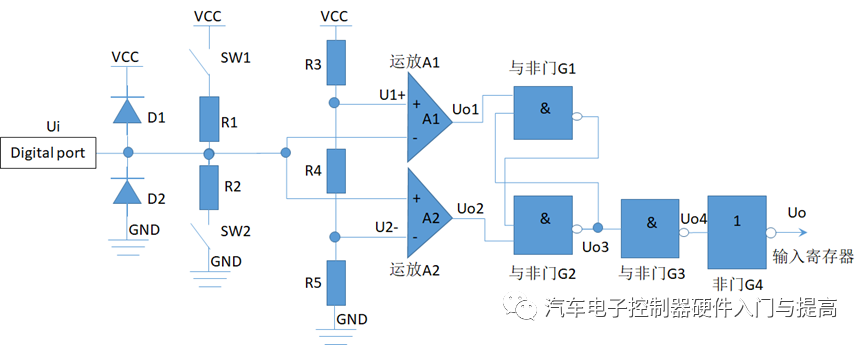

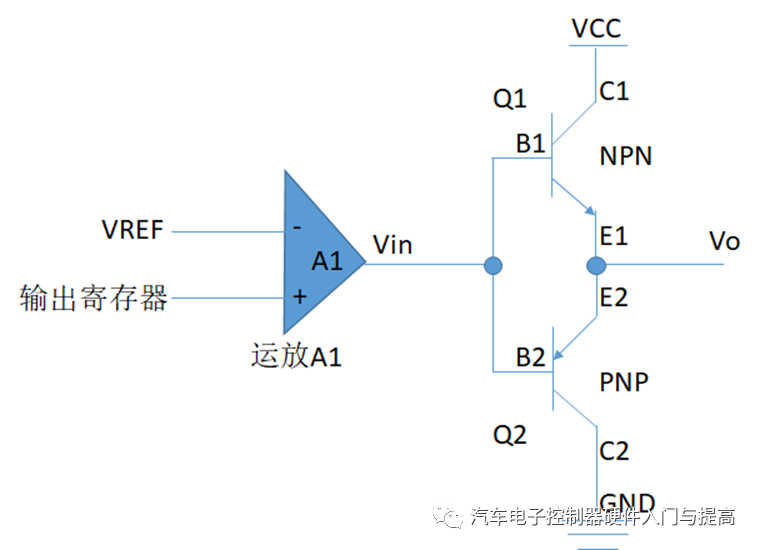

2.5.運(yùn)放比較器施密特觸發(fā)器下的GPIO主要電路結(jié)構(gòu)

其中

1)R1,R2為內(nèi)部弱上拉或弱下拉,阻值很大,一般為100k以上;

2)D1,D2為嵌位二極管,可以嵌位到-V(D2)到VCC+V(D1)之間,如果選擇硅管二極管,可以嵌位到-0.7V~5.7V;

3)R3=R4=R5=10Kohm

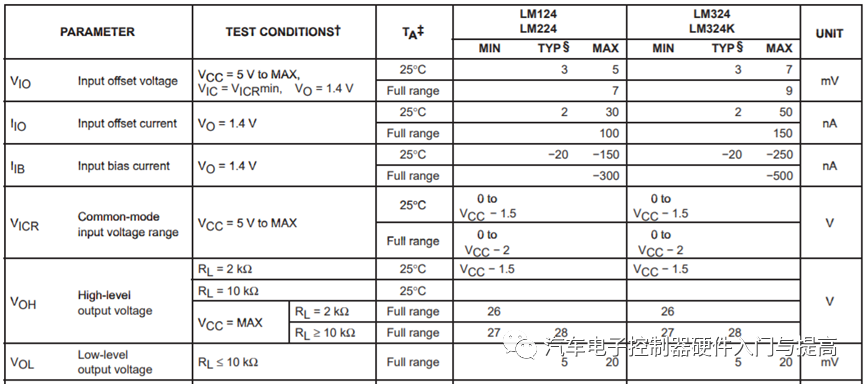

2.6.運(yùn)放比較器施密特觸發(fā)器下的GPIO閾值計(jì)算

利用運(yùn)放A1和A2的虛短特性,

U1+=VCC*(R4+R5)/(R3+R4+R5)=5*2/3=3.33V

U2+=VCCR5/(R3+R4+R5)=51/3=1.67V

與非門以74HC00DR2G舉例,此處不討論R1,R2接入情況

假設(shè)供電VCC=5V,那么UIH=3.5V,UIL=1.5V,VOH=4.5V,VOL=0.5V.

非門以74HC1G04舉例

假設(shè)供電VCC=5V,那么UIH=3.5V,UIL=1.5V,VOH=4.5V,VOL=0.5V.

運(yùn)放比較器以LM324為例,工作量程V+-V-最大7mV,也就是說(shuō)V+-V-超過(guò)7mV,運(yùn)放進(jìn)入放大飽和區(qū)間,此時(shí)輸出VOH=3.5V,即為比較器功能。

1)當(dāng)外部信號(hào)Ui未接入時(shí)

U1+=3.33V>Ui,那么U01=3.5V

Ui

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | 懸空 | 1 | 0 | 1 | 0 | 1 |

| 電壓值 | 懸空 | 3.5V | 0.005V | 4.5V | 0.5V | 4.5V |

2)當(dāng)外部信號(hào)Ui輸入上升,Ui<1.67V時(shí),

U1+=3.33V>Ui,那么U01=3.5V

Ui

假設(shè)Ui=1.0V

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | - | 1 | 0 | 1 | 0 | 1 |

| 電壓值 | 1.0V | 3.5V | 0.005V | 4.5V | 0.5V | 4.5V |

3)當(dāng)外部信號(hào)Ui輸入繼續(xù)上升,3.33V=>Ui>=1.67V時(shí),

U1+=3.33V>Ui,那么U01=3.5V

Ui>=U2-=1.67V,那么U02=3.5V

假設(shè)Ui=3V

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | - | 1 | 1 | 1 | 0 | 1 |

| 電壓值 | 3V | 3.5V | 3.5V | 4.5V | 0.5V | 4.5V |

4)當(dāng)外部信號(hào)Ui輸入繼續(xù)上升,Ui>=3.33V時(shí),

U1+

Ui>=U2-=1.67V,那么U02=3.5V

假設(shè)Ui=4.2V

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | - | 0 | 1 | 0 | 1 | 0 |

| 電壓值 | 4.2V | 0.005V | 3.5V | 0.5V | 4.5V | 0.5V |

綜合1)~4)可以得出VDIH=3.33V(Uo由4.5V變?yōu)?.5V)

5)當(dāng)外部信號(hào)Ui輸入從5V下降到, Ui>3.33V

U1+=3.33V>Ui,那么U01=0.005V

Ui>=U2-=1.67V,那么U02=3.5V

假設(shè)Ui=4.2V

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | - | 0 | 1 | 0 | 1 | 0 |

| 電壓值 | 4.2V | 0.005V | 3.5V | 0.5V | 4.5V | 0.5V |

6)當(dāng)外部信號(hào)Ui輸入繼續(xù)下降,3.33V=>Ui>=1.67V

U1+=3.33V>Ui,那么U01=3.5V

Ui>=U2-=1.67V,那么U02=3.5V

假設(shè)Ui=3V

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | - | 1 | 1 | 0 | 1 | 0 |

| 電壓值 | 3V | 3.5V | 3.5V | 0.5V | 4.5V | 0.5V |

7)當(dāng)外部信號(hào)Ui輸入繼續(xù)下降,Ui<=1.67V

U1+=3.33V

Ui<=U2-=1.67V,那么U02=0.005V

假設(shè)Ui=1.2V

真值表為以下

| 信號(hào) | Ui | Uo1 | Uo2 | Uo3 | Uo4 | Uo |

|---|---|---|---|---|---|---|

| 邏輯值 | - | 0 | 0 | 1 | 0 | 1 |

| 電壓值 | 1.2V | 0.005V | 0.005V | 4.5V | 0.5V | 4.5V |

綜合1)~4)可以得出VDIL=1.67V(Uo由0.5V變?yōu)?.5V)

-

輸入輸出

+關(guān)注

關(guān)注

0文章

42瀏覽量

10748 -

TTL

+關(guān)注

關(guān)注

7文章

503瀏覽量

70231 -

運(yùn)放

+關(guān)注

關(guān)注

47文章

1163瀏覽量

53062 -

觸發(fā)器

+關(guān)注

關(guān)注

14文章

2000瀏覽量

61132 -

GPIO

+關(guān)注

關(guān)注

16文章

1204瀏覽量

52056

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

STM32 GPIO寄存器的相關(guān)知識(shí)

STM32的GPIO輸入模式和輸出模式結(jié)構(gòu)

二.GPIO輸入輸出及延遲函數(shù)

04、STM8通用輸入輸出口(GPIO)

STM32的8種GPIO輸入輸出模式

GPIO通用輸入輸出

GPIO內(nèi)部結(jié)構(gòu)和工作模式

STM32-(基于STM32F4)-GPIO基本結(jié)構(gòu)-輸入/輸出模式

GPIO內(nèi)部結(jié)構(gòu)及輸入輸出模式

通用輸入輸出GPIO是什么

i.MX6ULL學(xué)習(xí)筆記:GPIO按鍵輸入捕獲

GPIO輸出主要電路結(jié)構(gòu)

GPIO輸入主要電路結(jié)構(gòu)

GPIO輸入主要電路結(jié)構(gòu)

評(píng)論