今年年初,美國硅谷舉辦了“首屆年度芯粒設(shè)計(jì)峰會(huì)”。此次峰會(huì)的主題是:

“摩爾定律”已經(jīng)失效,我們剩下的只有封裝。

在筆者之前的文章中提到過:

如今,來自一家公司的多芯粒設(shè)計(jì)正在大量出貨,他們準(zhǔn)備圍繞芯粒組建自己的生態(tài)系統(tǒng),而芯粒商店這種愿景目前還只是天方夜譚。

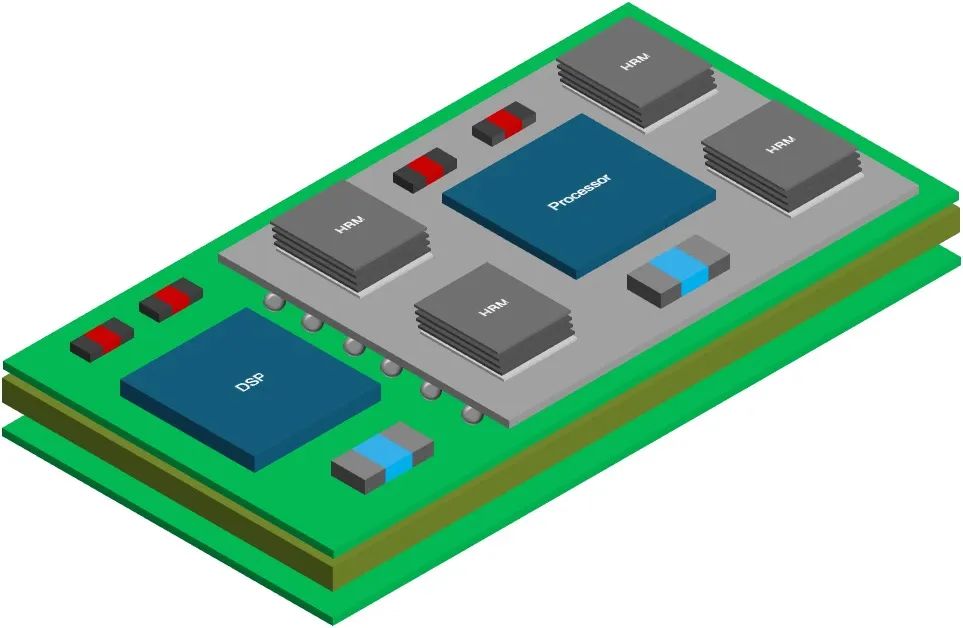

許多公司在制造芯粒時(shí)并未考慮到與其他公司的芯粒一同使用的情況,所以,要使用這些不同公司生產(chǎn)的芯粒進(jìn)行基于芯粒的設(shè)計(jì),必然需要解決一些技術(shù)問題。這類似于,我們從不同的制造商購買芯片,然后把它們放在一塊 PCB 上,以構(gòu)建一個(gè)可以運(yùn)行的系統(tǒng),但設(shè)計(jì)這些芯片的公司從未預(yù)想過此種使用場景。

2.5D vs 3D

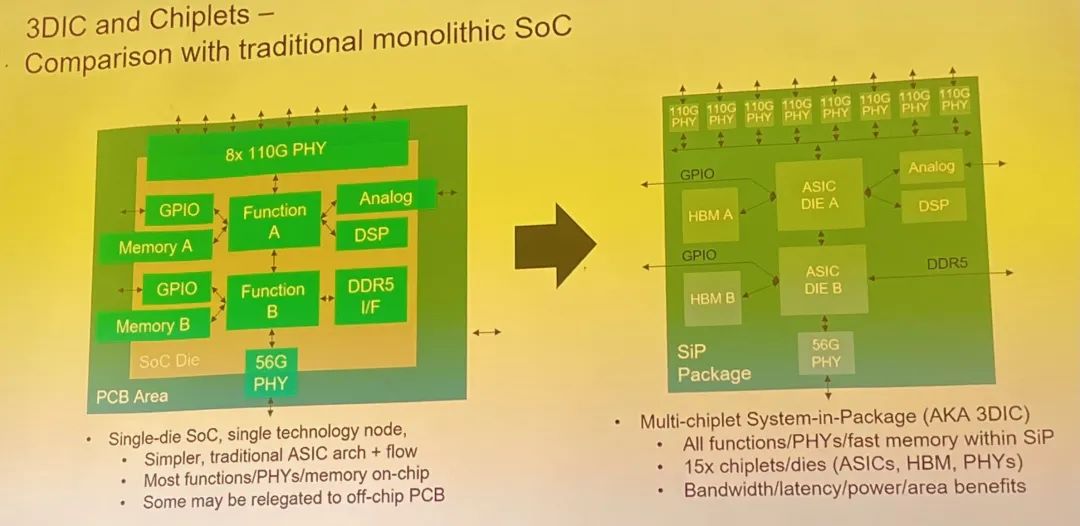

首先在此澄清,我們討論的是將多個(gè)基于芯粒的設(shè)計(jì)整合到一個(gè)中介層上(硅中介層或有機(jī)中介層),而不是真正的 3D 設(shè)計(jì),即多個(gè)裸片彼此堆疊。這種設(shè)計(jì)已經(jīng)上市了(例如,索尼的圖像傳感器有一個(gè)包含邏輯、存儲器和傳感器本身的三裸片堆疊)。然而,堆疊多個(gè)裸片通常需要利用硅通孔 (through-silicon vias,TSV),所以需要非常仔細(xì)地設(shè)計(jì)芯片,以確保所有東西都能對齊。要將不同廠商生產(chǎn)的裸片堆疊成真正的 3D 設(shè)計(jì),這個(gè)過程相當(dāng)漫長。

目前,任何真正的 3D 裸片堆疊都是由一家公司設(shè)計(jì)的,將一個(gè)大型設(shè)計(jì)分割成多個(gè)裸片。而且除了對齊所有 TSV,還需要解決艱巨的散熱挑戰(zhàn)。

因此,在后文(以及可以預(yù)見的未來)中,我們所說的基于芯粒的設(shè)計(jì)都是指 2.5D 設(shè)計(jì)。

交換格式

如果要完成一個(gè)基于芯粒的設(shè)計(jì),那么我們的設(shè)計(jì)工具需要具備相應(yīng)的功能來讀取描述芯片的重要信息。目前,有兩項(xiàng)重要的標(biāo)準(zhǔn)化工作。

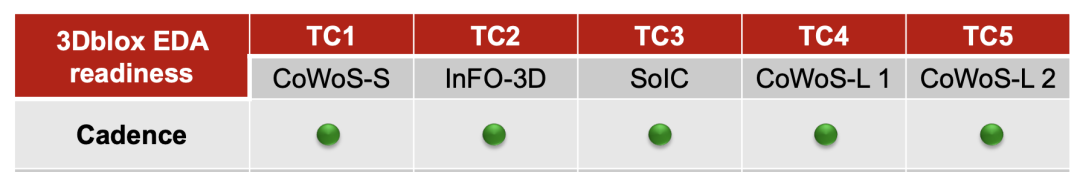

首先,臺積電在去年 10 月的 OIP 上宣布推出 3Dblox,3Dblox 是一個(gè)開放的標(biāo)準(zhǔn):

3Dblox 提供了能夠代表當(dāng)前和未來所有 3D-IC 結(jié)構(gòu)的通用語言結(jié)構(gòu)

將 3D-IC 結(jié)構(gòu)模塊化,從而使 EDA 工具和設(shè)計(jì)流程更加簡單和高效

確保標(biāo)準(zhǔn)化的 EDA 工具和設(shè)計(jì)流程符合臺積電 3DFabric 技術(shù)

3Dblox不是本文重點(diǎn),Cadence 的工具組合支持 3Dblox(上表中的所有綠點(diǎn))。

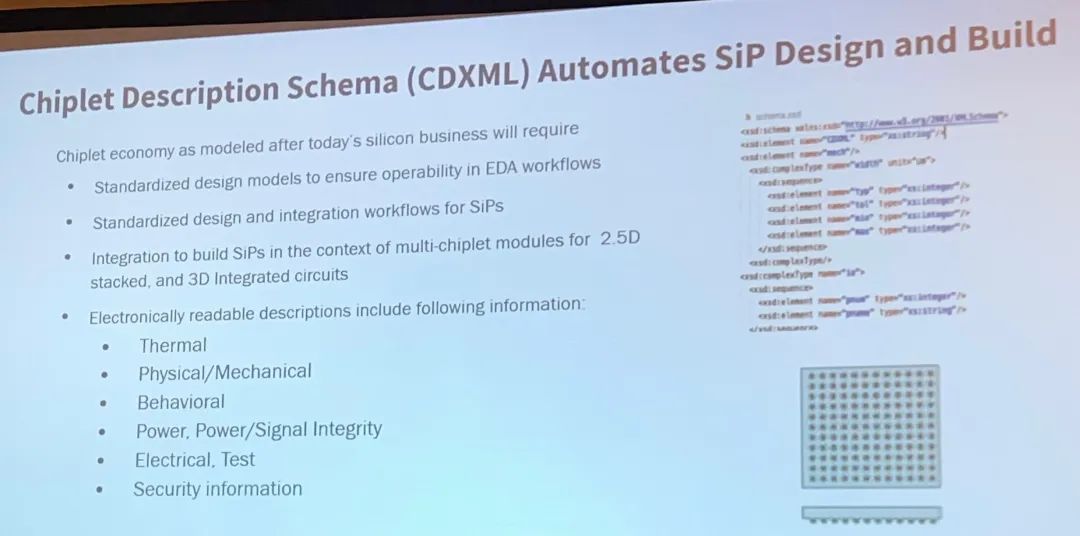

另一個(gè)標(biāo)準(zhǔn)是 CDXML,即“Chip Data Exchange Markup Language,芯片數(shù)據(jù)交換標(biāo)記語言”。該標(biāo)準(zhǔn)由 OCP(開放計(jì)算項(xiàng)目基金會(huì))開發(fā)。在芯粒峰會(huì)的第一天,JEDEC 和 OCP 就宣布正在合作制定這一標(biāo)準(zhǔn),并將被納入 JEP30,即 JEDEC 的零件模型指南。

那么,至少現(xiàn)在我們有兩個(gè)開放標(biāo)準(zhǔn):3Dblog 和 CDXML。

通信標(biāo)準(zhǔn)

存在兩個(gè)可行的通信標(biāo)準(zhǔn):一個(gè)是 Bundle-of-Wires (BoW),目前用于正在進(jìn)行的設(shè)計(jì);另一個(gè)是 UCIe (Universal Chiplet Interconnect Express),其 IP 即將上市。然而,盡管有英特爾、AMD、Arm、谷歌、Meta、高通等公司的背書,且 UCIe 有望成為終極標(biāo)準(zhǔn),峰會(huì)的參與者依然認(rèn)為 UCIe 標(biāo)準(zhǔn)“尚未完全準(zhǔn)備就緒”。

已知良好裸片

將多個(gè)芯粒封裝到一個(gè)封裝中與只使用單個(gè)裸片并不相同。如果使用單個(gè)裸片,就要在封裝成本和晶圓測試成本之間做出權(quán)衡。測試器較為昂貴,因此在晶圓劃片前耗費(fèi)太多精力進(jìn)行裸片測試比較浪費(fèi)成本。當(dāng)然,封裝也需要成本,所以也不能浪費(fèi)太多封裝。但如果因?yàn)槁闫|(zhì)量不佳而浪費(fèi)了一個(gè)封裝,那么并不算浪費(fèi)了裸片,因?yàn)樗呀?jīng)報(bào)廢了。

如果一個(gè)封裝內(nèi)有多個(gè)裸片,那么成本計(jì)算方式將完全不同。如果在晶圓測試中遺漏了一個(gè)不良裸片,那么當(dāng)它與所有其他裸片一起封裝時(shí),則不僅僅是浪費(fèi)了一個(gè)不良裸片(以及封裝的成本),也浪費(fèi)了這個(gè)封裝中所有質(zhì)量良好的裸片。另外,多個(gè)芯粒的封裝成本比單個(gè)芯粒要高得多。因此,很有必要在進(jìn)入組裝階段之前,對每個(gè)裸片進(jìn)行全面測試。這些裸片稱為 KGD(Known Good Die),即已知良好裸片。

可以采用一些措施來優(yōu)化封裝過程,例如在只置入部分裸片的情況下測試一個(gè)封裝。如此一來,可以先置入成本低廉的裸片,然后進(jìn)行測試,最后再置入昂貴的裸片(如最先進(jìn)節(jié)點(diǎn)的 CPU 或 GPU)。這樣可以避免由于某個(gè)非常便宜的元件發(fā)生故障而導(dǎo)致某個(gè)昂貴的元件也被迫報(bào)廢。

測試

多芯粒設(shè)計(jì)(甚至是真正的 3D 設(shè)計(jì))測試遵循 IEEE 1838-2019 標(biāo)準(zhǔn),即 IEEE 三維堆疊集成電路測試引入架構(gòu)標(biāo)準(zhǔn)。

安全性

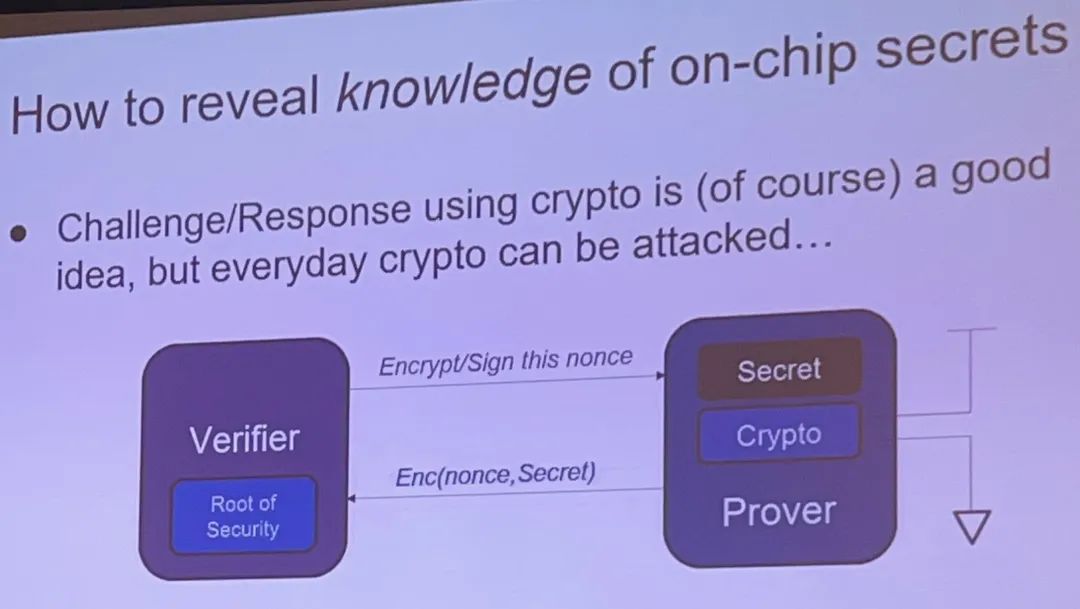

安全方面有很多問題。目前處理安全問題的方式是使用硬件信任根。對于一個(gè)基于芯粒的系統(tǒng),首先需要確定是否信任所有的芯粒,或者判斷從陌生供應(yīng)商那里獲得的一個(gè)或多個(gè)芯粒是否有可能遭到破壞。另外,還需要決定是否用一個(gè)芯粒確保安全性(包含有密鑰的安全飛地等),然后驗(yàn)證所有其他芯粒是否安全。如果很多芯粒都包含需要啟動(dòng)的微處理器,那么可以集中處理,或者,每個(gè)芯粒必須處理自身的安全啟動(dòng)。

正如 Rambus Security 的 Scott Best 所指出的那樣,5nm 的安全性設(shè)計(jì)非常復(fù)雜,幾乎不可能實(shí)現(xiàn),更不用說反向工程了。但基于芯粒的安全性設(shè)計(jì)則比較容易。

當(dāng)我們把設(shè)計(jì)分解成芯粒時(shí),SiP 就相當(dāng)于安全性最低的芯粒。

更糟糕的是,雖然在一個(gè) 5nm 的芯片上監(jiān)控大量的內(nèi)部信號幾乎無法實(shí)現(xiàn),但在一個(gè)多芯粒設(shè)計(jì)中監(jiān)控中介層上的信號卻簡單得多。在實(shí)踐中,這意味著需要對任何與安全有關(guān)的芯粒之間的通信進(jìn)行加密。當(dāng)然,這些芯粒的設(shè)計(jì)初衷并不涉及到彼此協(xié)作,因此加密并不簡單。處理這個(gè)問題的方法通常是使用某種形式的“挑戰(zhàn)-回應(yīng)”模式,但這種模式需要植入到每個(gè)芯粒中。在實(shí)踐中,需要為芯粒制定某種安全標(biāo)準(zhǔn)。

另外還有一些非主流的方法,如差分功率分析 (Differential Power Analysis,DPA)。

故障排查

如果出現(xiàn)故障該怎么辦?使用者可能不了解自己購買的所有芯粒的全部內(nèi)部細(xì)節(jié),該如何確定哪個(gè)芯粒是罪魁禍?zhǔn)祝?/p>

有些人認(rèn)為這是一個(gè)大問題,但其實(shí)這就類似于確定哪個(gè) IP 模塊引起了 SoC 故障,甚至與確定電路板上哪個(gè)芯片引起了板級故障并無二致。一種方法是假設(shè)這種情況可能發(fā)生,并提供某種方法來啟用和禁用系統(tǒng)的各個(gè)模塊。在微處理器中,這被稱為“chicken bits”。

特殊市場

峰會(huì)期間還有兩個(gè)隨機(jī)出現(xiàn)的話題。

超級計(jì)算機(jī),即最高端的 HPC,幾乎總是使用 COTS 部件,即“商業(yè)現(xiàn)成(commercial off-the-shelf)”部件,如英特爾/AMD CPU、英偉達(dá) GPU、FPGA 等等。正如 Lawrence Berkeley Laboratory 的 John Shalf 所說:

我們無法承擔(dān)從頭開始自研芯片的成本。

所以對他來說,芯粒提供了一種機(jī)會(huì)——可以購買現(xiàn)成的芯粒(也許可以簡稱為 COTC),并將其緊密地集成到系統(tǒng)中。

其次是汽車。汽車行業(yè)對芯粒不太看好,因?yàn)槠囍信c振動(dòng)有關(guān)的機(jī)械問題都會(huì)引發(fā)可靠性問題;而且汽車的期望使用壽命是二十年。另一方面,自動(dòng)駕駛將像其他技術(shù)一樣受到***極限的限制,因此汽車行業(yè)可能會(huì)迎難而上,因?yàn)闊o論如何,他們最終都需要使用芯粒。Cadence 歐洲學(xué)術(shù)網(wǎng)絡(luò)主管 Anton Klotz 在年初參加一個(gè)汽車會(huì)議時(shí)也聽到了類似消息:

自動(dòng)駕駛芯片的數(shù)量不足以證明成本的合理性。通過將不同供應(yīng)商的芯粒集成在一個(gè)中介層上,有望降低總成本;

芯粒比印刷電路板更節(jié)能;因此這種集成將大有裨益,有助于增加電動(dòng)汽車的續(xù)航能力,并提供更好的性能

-

芯片

+關(guān)注

關(guān)注

459文章

52291瀏覽量

437560 -

pcb

+關(guān)注

關(guān)注

4358文章

23442瀏覽量

407684 -

芯粒

+關(guān)注

關(guān)注

0文章

63瀏覽量

253

發(fā)布評論請先 登錄

奎芯科技登場 COMPUTEX 2025,聚焦芯粒互連解決方案

信捷電氣推出數(shù)粒機(jī)解決方案

Arm正式發(fā)布芯粒系統(tǒng)架構(gòu)首個(gè)公開規(guī)范

Arm宣布其芯粒系統(tǒng)架構(gòu)正式推出首個(gè)公開規(guī)范

Arm發(fā)布芯粒系統(tǒng)架構(gòu)首個(gè)公開規(guī)范

今日看點(diǎn)丨Arm 發(fā)布芯粒系統(tǒng)架構(gòu)首個(gè)公開規(guī)范;納芯微推出車規(guī)級D類音頻功率放大器

知存科技邀您相約第二屆集成芯片和芯粒大會(huì)

集成芯片與芯粒技術(shù)詳解

Imec牽頭啟動(dòng)汽車芯粒計(jì)劃

強(qiáng)勢入局芯粒技術(shù)鏈 東方晶源PanSys產(chǎn)品重磅發(fā)布

北極雄芯“啟明 935”系列芯粒成功交付流片

芯德科技揚(yáng)州晶圓級芯粒先進(jìn)封裝基地項(xiàng)目封頂

英特爾OCI芯粒在新興AI基礎(chǔ)設(shè)施中實(shí)現(xiàn)光學(xué)I/O(輸入/輸出)共封裝

英特爾突破技術(shù)壁壘,推出全新硅光集成OCI芯粒

英特爾實(shí)現(xiàn)光學(xué)IO芯粒的完全集成

評論