大家好,我是南山掃地僧。

在DCDC電源電路中,PCB的布局對電路功能的實現(xiàn)和良好的各項指標(biāo)來說都十分重要。本文以buck電路為例,簡單分析一下如何進(jìn)行合理PCB layout布局以及設(shè)計中的注意事項。如有問題,歡迎指正。

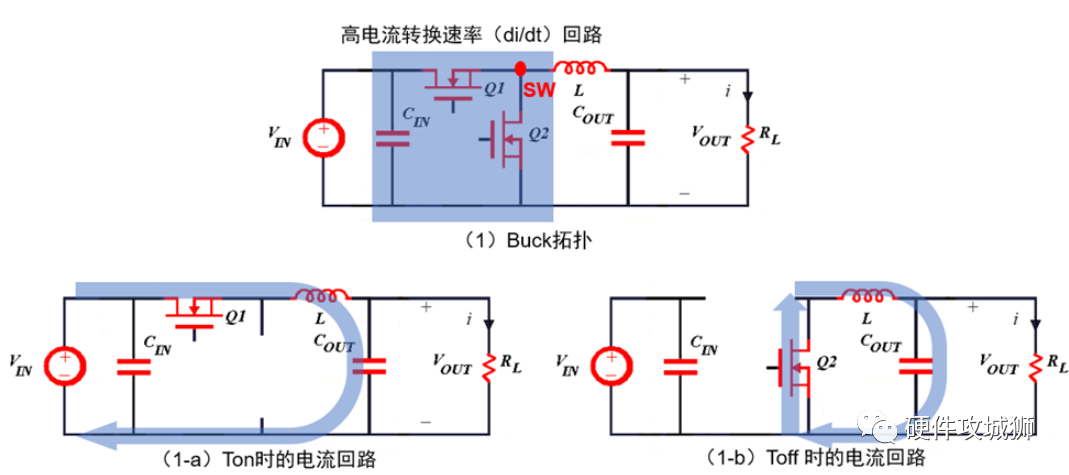

首先,以最簡單的BUCK電路拓?fù)錇槔聢D(1-a)和(1-b)中分別標(biāo)明了在上管開通和關(guān)斷時刻電流的走向,即功率回路部分。這部分電路負(fù)責(zé)給用戶負(fù)載供電,承受的功率較大。

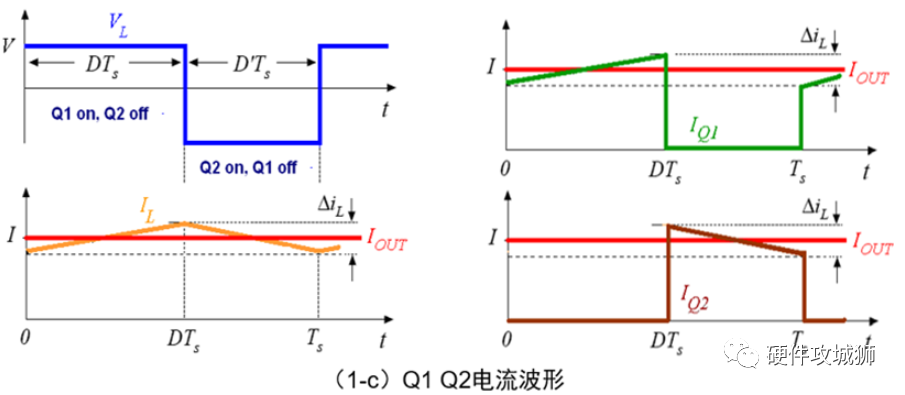

結(jié)合圖(1-c)中Q1和Q2的電流波形,不難發(fā)現(xiàn),由于電感的存在,后半部分電路中不會存在一個較高的電流變化趨勢,只有在兩個開關(guān)管的部分會出現(xiàn)高電流轉(zhuǎn)換速率。在PCB布線時需要特別注意,盡可能減小這一快速變化的環(huán)節(jié)的面積,來減少對其他部分的干擾。隨著集成工藝的進(jìn)步,目前大部分電源芯片都將上下管集成到了芯片的內(nèi)部。

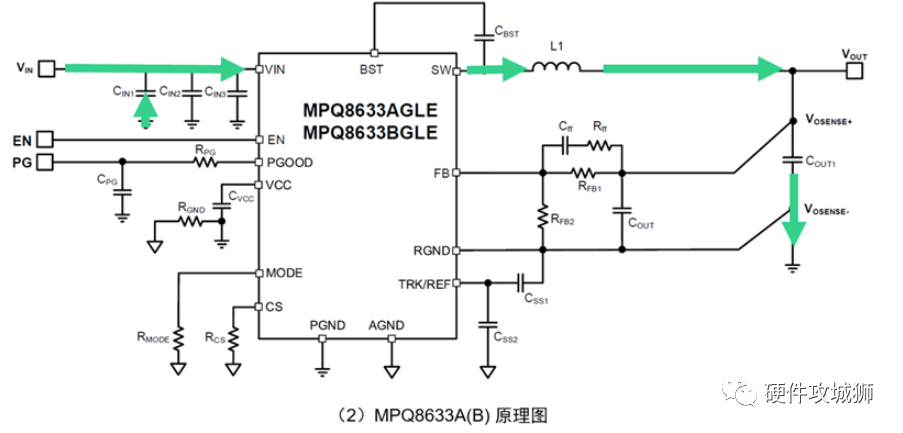

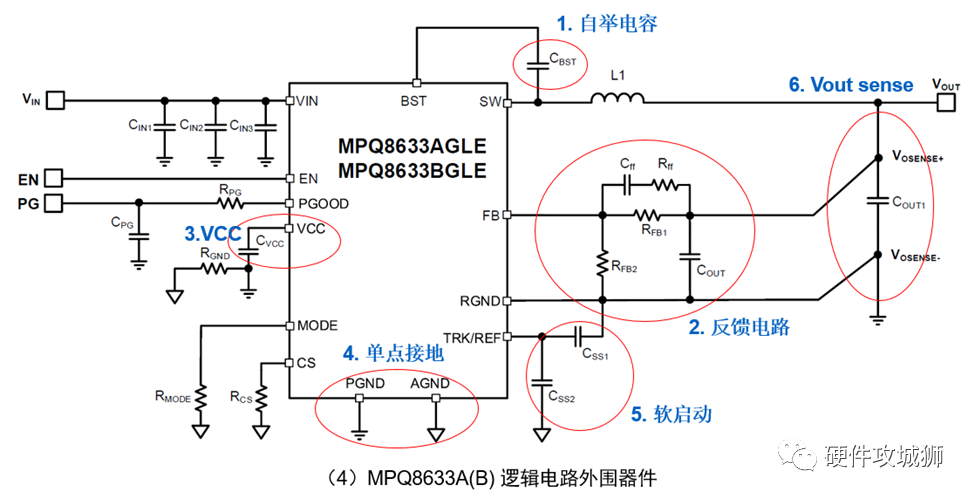

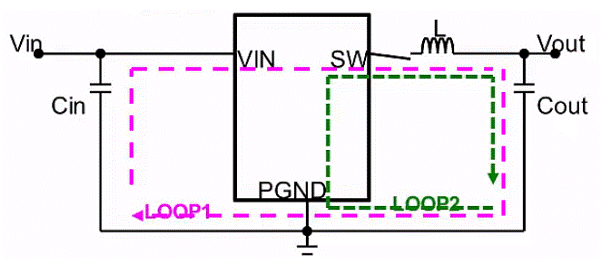

了解了高電流轉(zhuǎn)換速率部分后,讓我們回到整個功率回路布局來看。以MPS的非常受歡迎的MPQ8633A(B)系列產(chǎn)品為例,這是一款完全集成的高頻同步降壓轉(zhuǎn)換器可以實現(xiàn)高達(dá)12-20A的輸出電流,其原理圖如下,其功率回路(綠色標(biāo)注)中包含輸入電容,電感以及輸出電容等器件。

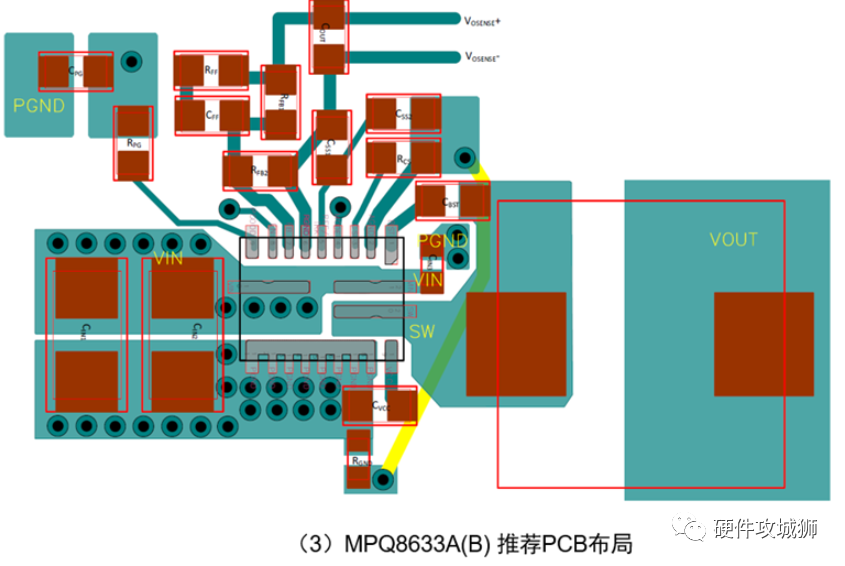

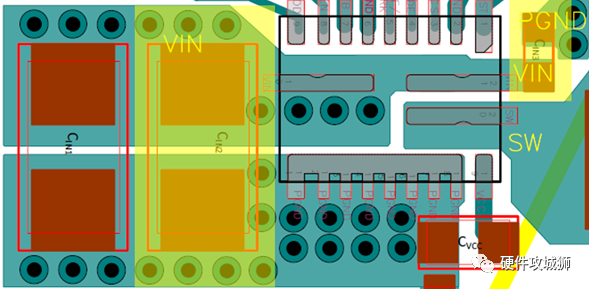

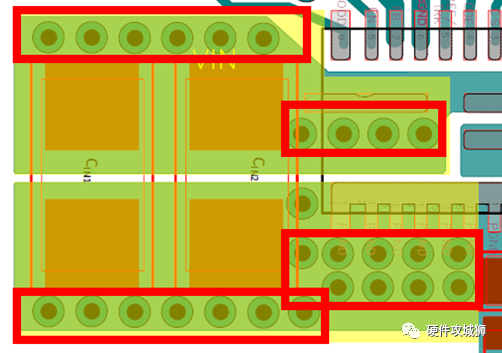

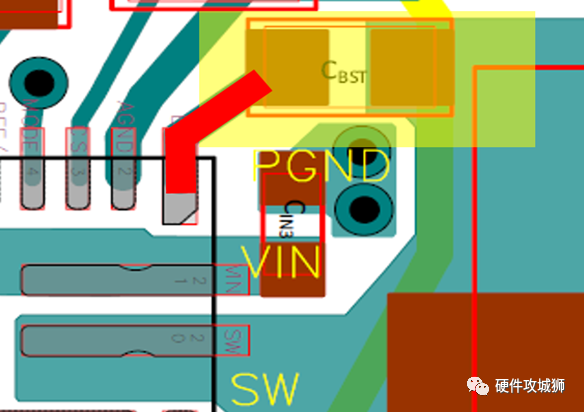

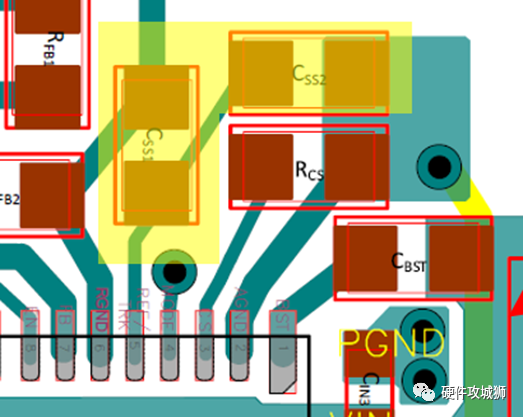

功率回路也需要做到盡可能地占用較小的環(huán)路面積,來減少噪聲的發(fā)射以及回路上的寄生參數(shù)。推薦的PCB布局如圖(3)所示。注意點如下:

1,輸入電容就近放在芯片的輸入Vin 和功率地PGND ,減少寄生電感的存在,因為輸入電流不連續(xù),寄生電感引起的噪聲對芯片的耐壓以及邏輯單元造成不良影響。VIN 的管腳旁邊至少各有1 個去耦電容,用來濾除來自電源輸入端的交流噪聲和來自芯片內(nèi)部(倒灌)的電源噪聲,同時也為芯片儲能。且電容需要緊挨管腳,兩者的間距需要小于40mil 。

2,功率回路盡可能的短粗,保持較小的環(huán)路面積,減少噪聲的發(fā)射。

3,SW 點是噪聲源,保證電流的同時保持盡量小的面積,遠(yuǎn)離敏感的易受干擾的位置,例如FB 等。

4,鋪銅面積和過孔數(shù)量會影響到PCB 的通流能力和散熱。由于PCB的載流能力與PCB板材、板厚、導(dǎo)線寬厚度以及溫升相關(guān),較為復(fù)雜,可以通過IPC-2152標(biāo)準(zhǔn)來進(jìn)行準(zhǔn)確的查找和計算。一般,對于MPQ8633A(B)的PCB來說,需要在VIN(至少打6個過孔)和PGND(至少打9個過孔)處多打過孔,這兩處的鋪銅應(yīng)最大化來減小寄生阻抗。SW處的鋪銅也需要加寬,以免出現(xiàn)限流的情況,導(dǎo)致工作異常。

討論完功率回路部分,轉(zhuǎn)眼看芯片邏輯電路部分,這部分的PCB布局也是有所講究的。

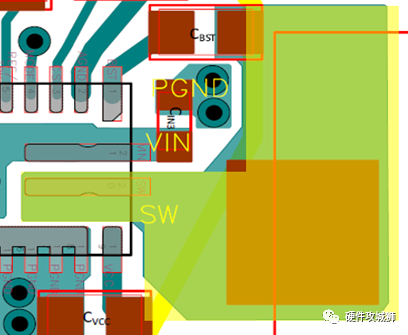

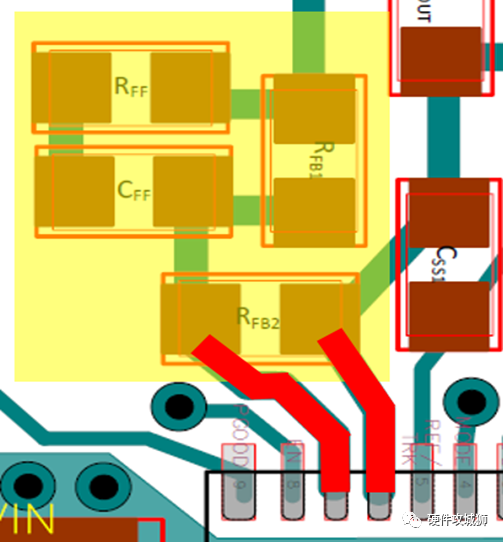

結(jié)合圖(3)和(4)可總結(jié)注意點如下:

將BST 電容放置在盡可能靠近BST 和SW 的位置,使用20mil 或更寬來布線路徑。

FB 電阻連接到FB 管腳盡可能短,減少噪聲的耦合。這是芯片最敏感,最容易受干擾的部分,是引起系統(tǒng)不穩(wěn)定的十分常見原因。需要將其遠(yuǎn)離噪聲源,例如:SW點,電感,二極管等(在非同步buck中,MPQ8633外圍無二極管)。如圖,RFF、CFF、RFB1、RFB2都盡量靠近芯片擺放。

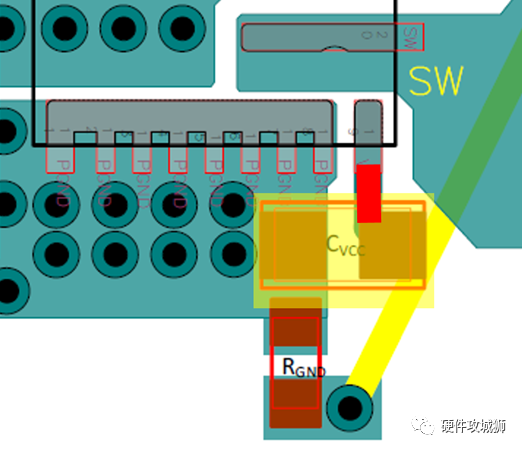

VCC 電容應(yīng)就近放置在芯片的VCC 管腳和芯片的信號地之間,盡量在一層,沒有過孔。對于信號地(AGND)和功率地(PGND)在一個管腳的芯片,同樣就近和該管腳連接。

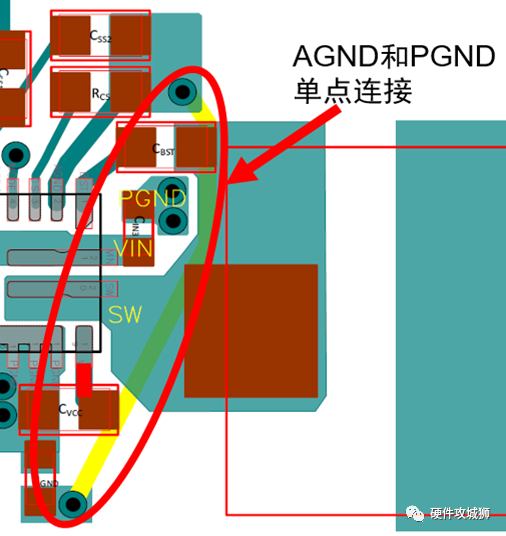

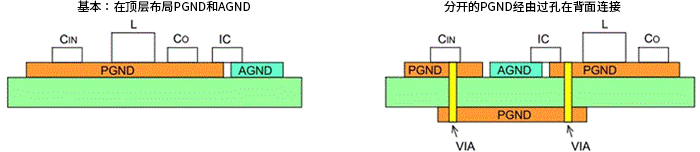

AGND和PGND需要進(jìn)行單點連接。

將SS 電容靠近TRK/REF 至RGND 。

將SENSE電容置于輸出SENSE線之間,平行走線。

PCB layout 中走線和鋪銅都盡量避免90°直角,走45°或者圓弧角,特別是在高頻信號傳輸線部分。避免由傳輸線寬帶來的反射和傳輸信號的失真。

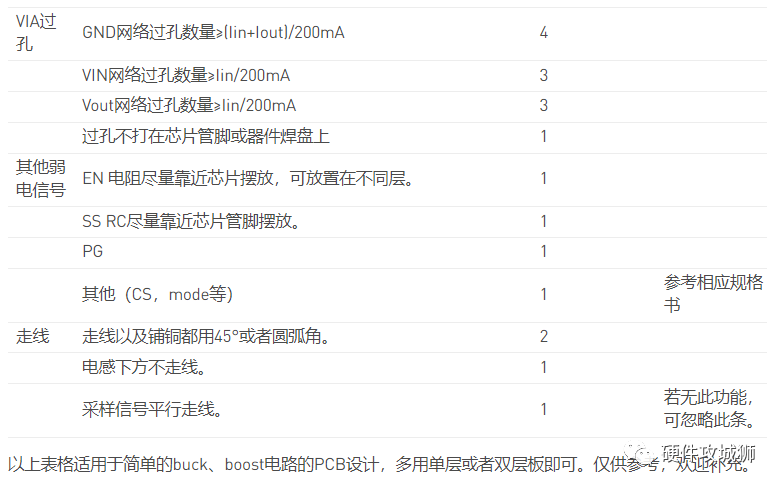

最后,為了方便大家了解自己畫的PCB是否合理,可以參考以下簡易表格做一個自評:

審核編輯:湯梓紅

-

pcb

+關(guān)注

關(guān)注

4319文章

23080瀏覽量

397511 -

BUCK

+關(guān)注

關(guān)注

32文章

482瀏覽量

64127 -

電源電路

+關(guān)注

關(guān)注

48文章

995瀏覽量

65188 -

DC-DC

+關(guān)注

關(guān)注

30文章

1943瀏覽量

81603 -

Layout

+關(guān)注

關(guān)注

14文章

403瀏覽量

61739

原文標(biāo)題:某大廠DC-DC芯片PCB布局及注意事項

文章出處:【微信號:南山掃地僧,微信公眾號:南山掃地僧】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

接地—升壓型DC/DC轉(zhuǎn)換器的PCB布局

半橋DC-DC轉(zhuǎn)換器電路圖 半橋DC-DC電路介紹及PCB布局注意點

DC-DC開關(guān)電源設(shè)計

DC-DC轉(zhuǎn)換器的相關(guān)資料分享

非隔離型DC-DC變換器的布線注意事項

升壓型DC/DC轉(zhuǎn)換器的PCB布局中“接地”探討

dc-dc開關(guān)控制芯片怎么選型,dc-dc開關(guān)控制芯片選型注意事項

升壓型DC/DC轉(zhuǎn)換器的PCB布局中接地設(shè)計

DC-DC的PCB設(shè)計注意的點

快速輸入轉(zhuǎn)換速率應(yīng)用中DC-DC轉(zhuǎn)換器的設(shè)計注意事項

DC-DC芯片PCB布局及注意事項

DC-DC芯片PCB布局及注意事項

評論