建立時間 :時鐘上升沿之前數據保持穩定時間

保持時間:在時鐘上升沿之后數據保持穩定的時間。

建立時間Tsu

根據時鐘周期公式:

Tco+Tdata+Tsu-Tskew< Tcycle

可以推導出建立時間的裕量Sslack為:

Tcycle-(Tco+Tdata+Tsu-Tskew) >0

當Sslack大于等于0時即滿足建立時間的要求。

保持時間Th

保持時間的目的是防止下一次的數據傳輸過快,將本次的數據沖刷掉,是對上次數據時間的約束。經過Tsu建立時間之后,觸發器進入建立時間階段,在該階段最擔心的問題是下一次的數據來的太快,導致還未滿足保持時間的要求。

所以要求下一次數據到來的時間要大于Th,而下一次數據到來的時間為:

Tco+Tdata-Tskew

所以保持時間裕量計算公式為:

Hslack=(Tco+Tdata-Tskew) >0

扇入與扇出

扇入 :扇入系數是指門電路允許有幾個輸入,一般門電路允許的扇入系數為1~5,最多不超過8。

扇出 :扇出系數是指門電路允許驅動同類型的門的個數,也就是負載能力,一般門電路的扇出系數為8,驅動器的扇出系數為25,體現了門電路的驅動能力。

灌電流與拉電流

灌電流:當門電路的輸出端為低電平時,邏輯門的輸入電流為灌電流。灌電流越大,邏輯門輸出低電平就越高。

拉電流:當門電路的輸出端為高電平時,邏輯門的輸出電流為拉電流。拉電流越大,邏輯門的輸出高電平就越低。

上拉電阻和下拉電阻

上拉電阻:上拉電阻就是將一個不確定信號的電平鉗位在高電平(拉電流),來增加高電平時的驅動能力,以解決邏輯門驅動能力不足的問題。

下拉電阻:下拉電阻就是將一個不確定信號的電平鉗位在低電平(灌電流),其作用是吸收電流,防止灌電流過大提高邏輯門的輸出電壓大小。

當輸出負載大于其負載能力時:

1、 邏輯門輸出低電平時,可能灌電流過大,輸出電壓Vol可能大于規定的Volmax

2、 邏輯門輸出高電平時,可能拉電流過大,輸出電壓Voh可能小于規定的Vohmin

3、 輸出的傳播延時大于規格說明的延遲值,主要表現為Net_delay(Tdata)

4、 輸出的上升和下降時間可能會高于規定值

5、超負載工作,電流較大,降低其可靠性,最終引起器件失效

Setup Violation與Hold Violation

根據建立時間公式Tsu:

Tcycle-(Tco+Tdata+Tsu-Tskew) >0

以及保持時間公式Th:

Hslack=(Tco+Tdata-Tskew) >0

當發生Setup Vioalation或Hold time Violation時,由于Tco是寄存器的固有屬性,系統時鐘一般也是固定的,可通過減小Tdata(當Sslack<0時)或者增大Tdata(當Hslack<0時),完成時序違例的優化:

舉一反二,以保持時間違例進行說明,控制Tdata,Tdata包含數據延遲和布線延遲兩部分,其關鍵在于如何降低數據延遲和布線延遲。

(1)、減小扇出Fanout,根據上文的分析可以分析Fanout較多時增加Net_delay,不利于時序收斂。減小扇出的方法有:

a、寄存器復制,幾個寄存器復制原先的驅動信號,分擔原本由一個寄存器驅動的多個模塊。

b、設置Max_Fanout,在代碼中設置信號屬性,將對應的Max_Fanout設置為一個合理的值,當實際中fanout超過此值時,綜合器極性自動優化,但是過低的扇出可能造成設計阻塞反而不利于約束。

c、BUFG,全局緩沖

(2)、減小邏輯級數Logic Level,一個Logic Level的延遲對應的是一個LUT(查找表)和一個Net的延遲,對應不同的器件,不同頻率的設計所能容納的Logic Level不同,一般可通過重定時(Retiming)解決Logic Level過大問題,使用的方法為:流水線,將過于冗長的組合邏輯增加寄存器進行打拍。對于時鐘偏斜△T來說因為不確定正負,其對建立時間和保持時間的影響是相反的,所以我們希望|△T|盡可能的小,所以盡量不要用生成時鐘,而采用全局時鐘,這樣才會有更小的|△T|。

-

驅動器

+關注

關注

53文章

8256瀏覽量

146564 -

上拉電阻

+關注

關注

5文章

360瀏覽量

30637 -

寄存器

+關注

關注

31文章

5357瀏覽量

120591 -

門電路

+關注

關注

7文章

199瀏覽量

40191 -

觸發器

+關注

關注

14文章

2000瀏覽量

61208

發布評論請先 登錄

相關推薦

【FPGA經典試題】電路模塊的setup-time和hold-time是正值還是負值

解釋下setup和hold time

警告-- Removed fan-out from the always-disabled I/O buffer 是什么意思

allegro PCB editor: 做到BGA Fan out 的時候,怎么設置BGA FAN OUT 的信號點 扇出到第幾層 ?

關于quartus上的RTL圖的讀法,將光標放在線上時,能看到fan-out= 3 ,請問這是什么意思,還有一個問題。

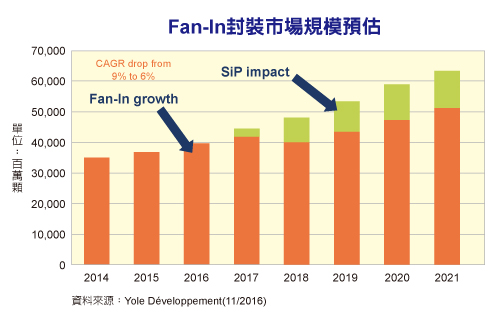

SiP封裝需求持續增加威脅Fan-In封裝未來發展

建立時間和保持時間(setup time 和 hold time)

為什么setup檢查下一個沿而hold檢查當前沿

UM2695_用于STM32探索套件和評估板的STMod_ fan_out擴展板

從fan-in、fan-out看setup和hold time violation

從fan-in、fan-out看setup和hold time violation

評論