引言

從上篇文章,我們可以很明顯的看出STA的兩大因素,一個是延遲計算,一個是約束檢查。STA最基本的工作之一就是檢查路徑延遲是否符合約束。

本篇文章主要講延遲計算。約束檢查在后續(xù)篇章講。

路徑延遲組成

路徑延遲(path delay)由單元延遲(cell delay)和線延遲(wire delay)組成:

path delay = 所有cell delay + 所有wire delay。

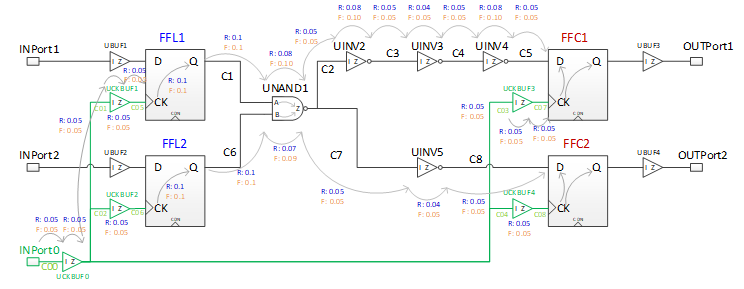

上篇文章中的計算式:

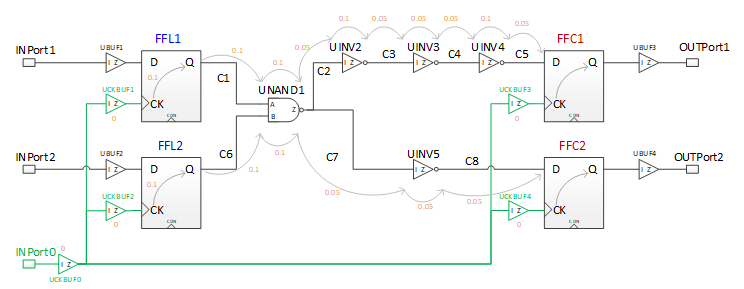

D(FFL1->FFC1)

= D(FFL1CP2Q) + D(C1) ~ ~ + D(UNAND1) + D(C2) + D(UINV2) + D(C3) + D(UINV3) + D(C4) + D(UINV4) + D(C5)

= 0.1 + 0.1 + 0.1 + 0.05 + 0.1 + 0.05 + 0.05 + 0.05 + 0.1 + 0.05

= 0.75ns

其中,D(FFL1->FFC1) 是從起始單元FFL1到終點單元FFC1的path delay,D(FFL1CP2Q)=0.1ns 是FFL1時序單元的cell delay,D(UNAND1)是UNAND1組合邏輯單元的cell delay……,D(C1)是線網(wǎng)C1的wire delay,D(C2)是線網(wǎng)C2的wire delay……

請注意,不管是path delay,還是cell delay,都有明確具體的pin起點和終點,如D(UNAND1)指的是cell UNAND1的A pin到Z pin的延遲。

Cell delay

先講Cell delay的計算

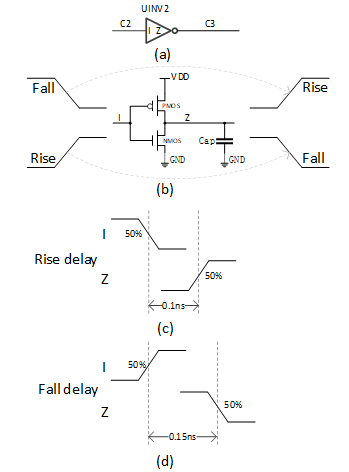

我們將圖一里反相器UINV2的內(nèi)部MOS電路畫出來,來理解cell延遲是如何發(fā)生的:

圖一 邏輯電路圖(含BC工作條件下的延遲信息)

**圖二 **反相器邏輯圖

如上圖所示,cell delay分 rise delay和fall delay 。

Rise fall是按照cell的輸出翻轉(zhuǎn)(transition)方向來定義的。考慮輸入是fall transition,輸出是rise transition的情形。 一開始,UINV2的輸入pin I上的電平是高電平,此時PMOS處于截止?fàn)顟B(tài),NMOS管處于導(dǎo)通狀態(tài),電容的上端通過NMOS管與地接通。 只要這個狀態(tài)持續(xù)足夠長,電容上的電會被放完,電放完時,UINV2單元的輸出pin Z處于低電平狀態(tài)。 接下來,I端開始Fall transition,到達(dá)PMOS的閾值電壓后,PMOS管完全導(dǎo)通, 電源通過PMOS管的channel向Cap充電,由于電容的存在,Z端電平出現(xiàn)一個緩慢上升的過程。

如圖二(c)所示,從I端的fall transion的50%電壓處,到Z端的rise transion的50%處,其時間差(0.1ns)即是該反相器的I端到Z端的rise delay。同樣,從圖八(d)可見,反相器的I端到Z端的fall delay是0.15ns。我們注意到rise delay和fall delay不相等,這是因為PMOS和NMOS導(dǎo)通后的channel電阻不一樣,所以充放電速度不一樣,表現(xiàn)出來即是delay不一樣。

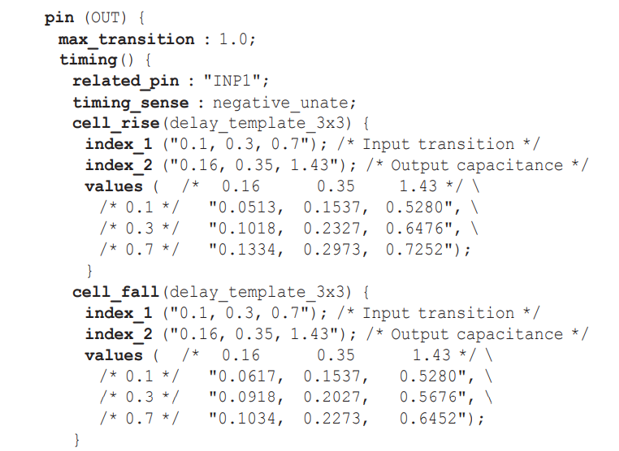

實際的STA過程,是通過查找表的方式來獲得cell delay的。 如下圖,在NLDM庫里輸入input transition和output capacitance,得到rise delay或者fall delay值:

Wire delay

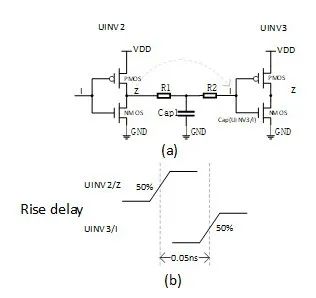

從UINV2的Z輸出端到UINV3的I輸入端之間是由金屬線連接起來的, wire存在寄生的電容電阻 。

**圖三 **線延遲

**wire delay = R1*Cap1 + (R1+R2)*Cap(UINV3/I)。**

一般情況, UINV2到UINV3之間的wire寄生參數(shù)可以用分布式RC樹來建模,作為分布式RC數(shù)的簡化模型,有T模型和Pi模型。 這里我們使用了簡化的T模型來建模和計算RC延遲。

現(xiàn)在,我們回頭再來看一下上面的path delay,它并沒有指出其delay是由起點處的rise transition還是fall transition經(jīng)過路徑傳播引起的,所以嚴(yán)格來說,計算式的正確性是值得懷疑的。

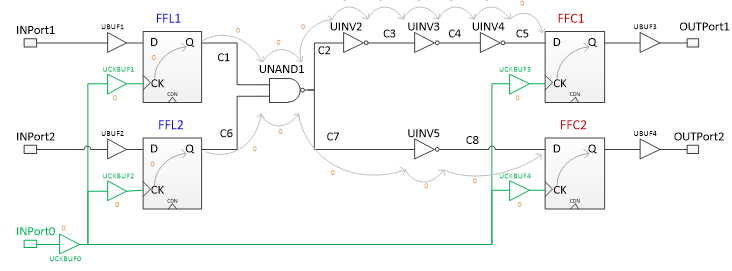

有了上述知識后,我們重新標(biāo)注了各個cell和wire的延遲,如圖十所示,“R:0.1”代表rise delay是0.1ns,“F:0.1”代表fall delay是0.1ns。同時,我們從這篇文章開始,將時鐘樹也納入考慮范圍,因此,時鐘樹上的cell delay和wire delay也標(biāo)識出來了。

圖四 邏輯電路圖(含BC****工作條件下的延遲信息)

很明顯,到FFC1存在兩條邏輯路徑,一條是從FFL1出發(fā)的路徑,一條是從FFL2出發(fā)的。從FFL1到FFC1的path delay有rise delay和fall delay,從FFL2到FFC1的path delay也有rise delay和fall delay,所以到FFC1的path delay總共有22 = 4條,即。同理,到FFC2的path delay也總共有22 = 4條。

小結(jié)

STA工具會計算這4條邏輯路徑上的總共8個path delay。然后與時序約束值做運算,判斷是否滿足約束。

想必看到這里,讀者童鞋會對路徑延遲有一個大概的了解。下一篇,我們介紹如何對這些路徑做setup、hold時序檢查,以及相關(guān)的STA概念。

-

MOS管

+關(guān)注

關(guān)注

108文章

2411瀏覽量

66762 -

反相器

+關(guān)注

關(guān)注

6文章

311瀏覽量

43292 -

PMOS

+關(guān)注

關(guān)注

4文章

245瀏覽量

29558 -

STA

+關(guān)注

關(guān)注

0文章

51瀏覽量

18958 -

NMOS管

+關(guān)注

關(guān)注

2文章

121瀏覽量

5407

發(fā)布評論請先 登錄

相關(guān)推薦

為什么STA321MPL上會有5個樣本延遲?

如何計算延遲和吞吐量?

靜態(tài)時序分析STA的優(yōu)點以及缺點分別有哪些呢

esp32在STA模式,ping延遲大,丟包多怎么解決?

STA7056.pdf

時序分析基本概念——STA概述簡析

基本的時序約束和STA操作流程

山西大學(xué)選購我司HS-STA-002同步熱分析儀

STA-0.靜態(tài)時序分析概述

STA分析-從一個案例開始

sta同步熱分析儀

鎮(zhèn)江安恬新材料有限公司選購我司HS-STA-002同步熱分析儀

STA分析—延遲計算

STA分析—延遲計算

評論