Setup和hold時間檢查

Setup時間是,為了寄存器可靠的采樣到數據,數據必須提前于采樣時鐘沿穩定的最小時間。Hold時間是,為了寄存器可靠的采樣到數據,數據必須在采樣時鐘沿后穩定的最小時間。

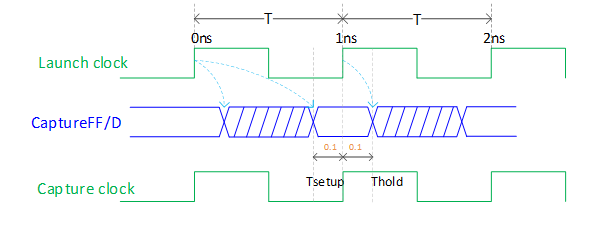

如圖一所示,周期T=1ns,該寄存器的setup要求時間是Tsetup=0.1ns,hold要求時間是Thold=0.1ns。setup時間檢查機制做這樣的檢查:上一個Launch時鐘沿打出來的數據的data arrival time(數據到達時間)不能晚于T - Tsetup = 0.9ns;而hold時間檢查機制做這樣的檢查:同一個周期的Launch時鐘沿打出來的數據的data arrival time(到達時間)不能早于Thold = 0.1ns。

同時滿足setup、hold時間要求的意義即是,在時鐘采樣沿的前后一段最小時間內,數據必須保存穩定,以供寄存器可靠的采樣到上一拍發送過來的正確數據。

**圖一 ** setup 、 hold****時間檢查示意圖

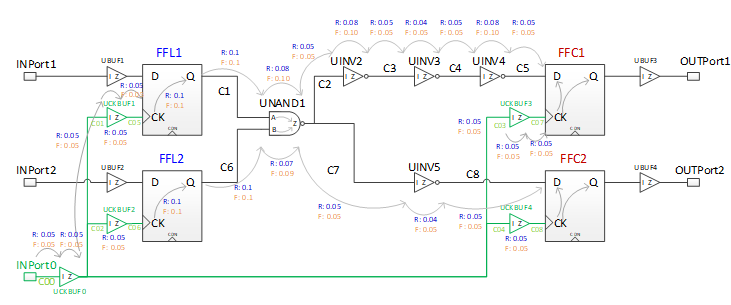

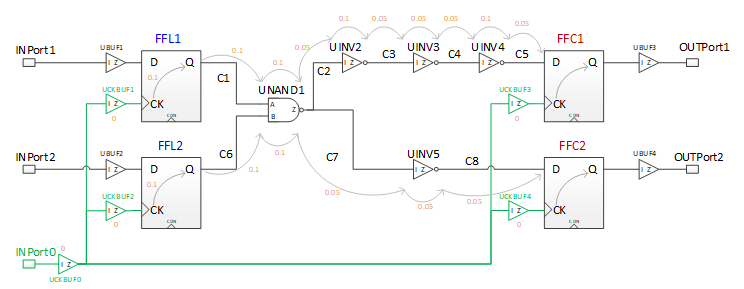

我們把上篇文章的圖再貼過來:

圖二 邏輯電路圖(含BC工作條件下的延遲信息)

下面分析FFC1寄存器的setup、hold檢查過程:

上篇文章說過,到FFC1的D端2條邏輯路徑和4個path delay,分別是FFL1->FFC1的rise delay、FFL1->FFC1的fall delay、FFL2->FFC1的rise delay、FFL2->FFC1的fall delay。

以時鐘源頭作為起點的path delay等于data arrival time。 根據圖一,可以看出:

0****1

FFL1到FFC1的rise delay的data arrival time

T(FFL1->FFC1-rise)

= T(Launch-clock-tree) + T(data-path-rise)

=T(C00-rise) + T(UCKBUF0-rise) + T(C01-rise) + T(UCKBUF1-rise) + T(C05-rise) + T(FFL1_CK2Q-rise) + T(C1-rise) ~ ~ + D(UNAND1_A2Z-fall) + T(C2-fall) + T(UINV2-rise) + T(C3-rise) + T(UINV3-fall) + T(C4-fall) + T(UINV4-rise) + T(C5-rise)

= (0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.1 + 0.05 + 0.08 + 0.05 + 0.05 + 0.05 + 0.08 + 0.05

= 0.96ns;

02

FFL1到FFC1的fall delay的data arrival time

T(FFL1->FFC1-fall)

= T(Launch-clock-tree) + T(data-path-fall)

=(0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.08 + 0.05 + 0.1 + 0.05 + 0.04 + 0.05 + 0.1 + 0.05

= 0.97ns;

03

FFL2到FFC1的rise delay的data arrival time

T(FFL2->FFC1-rise)

= T(Launch-clock-tree) + T(data-path-rise)

=T(C00-rise) + T(UCKBUF0-rise) + T(C02-rise) + T(UCKBUF2-rise) + T(C06-rise) + T(FFL2_CK2Q-rise) + T(C6-rise) ~ ~ + D(UNAND1_B2Z-fall) + T(C2-fall) + T(UINV2-rise) + T(C3-rise) + T(UINV3-fall) + T(C4-fall) + T(UINV4-rise) + T(C5-rise)

= (0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.09 + 0.05 + 0.08 + 0.05 + 0.05 + 0.05 + 0.08 + 0.05

= 0.95ns;

04

FFL2到FFC1的fall delay的data arrival time

T(FFL2->FFC1-fall)

= T(Launch-clock-tree) + T(data-path-fall)

=(0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1 + 0.1 + 0.07 + 0.05 + 0.1 + 0.05 + 0.04 + 0.05 + 0.1 + 0.05

= 0.96ns;

05

FFC1的setup requirement時間

T + T(Capture-clock-tree) - T(setup)

= T + T(C00-rise) + T(UCKBUF0-rise) + T(C03-rise) + T(UCKBUF3-rise) + T(C07-rise) - T(setup)

= 1ns + (0.05 + 0.05 + 0.05 + 0.05 + 0.05) – 0.1ns

= 1.15ns

06

FFC1的hold requirement時間

T(Capture-clock-tree) + T(hold)

= T(C00-rise) + T(UCKBUF0-rise) + T(C03-rise) + T(UCKBUF3-rise) + T(C07-rise) - T(setup)

= (0.05 + 0.05 + 0.05 + 0.05 + 0.05) + 0.1ns

= 0.35ns

做setup檢查時,STA會遍歷計算所有到FFC1/D端路徑的data arrival time,然后將每個值與T + T(Capture-clock-tree) - T(setup)做運算。以slack來表示余量,setup time slack = data require time – data arrival time = {T + T(Capture-clock-tree) - T(setup)} – {T(Launch-clock-tree) + T(data-path)}。只有當所有Slack值都為正時,才滿足setup時間要求。

類似的,做hold檢查時,也是將每個data arrival time的值與T(Capture-clock-tree) + T(hold)做比較,以slack來表示余量,hold time slack = data arrival time - data require time = {T(Launch-clock-tree) + T(data-path)} - {T(Capture-clock-tree) + T(hold)}。只有當所有Slack值都為正時,才滿足hold時間要求。

上述4個path delay的Setup time slack分別為:

Setup time slack(1) = 1.15ns – 0.96ns = 0.19ns

Setup time slack (2) = 1.15ns – 0.97ns = 0.18ns

Setup time slack (3) = 1.15ns – 0.95ns = 0.20ns

Setup time slack (4) = 1.15ns – 0.96ns = 0.19ns

4條path delay的hold slack time分別為:

Hold time slack(1) = 0.96ns – 0.35ns = 0.61ns

Hold time slack(2) = 0.97ns – 0.35ns = 0.62ns

Hold time slack(3) = 0.95ns – 0.35ns = 0.60ns

Hold time slack(4) = 0.96ns – 0.35ns = 0.61ns

由于所有slack值都為正,故setup和hold時間檢查都滿足了。

時序路徑概念

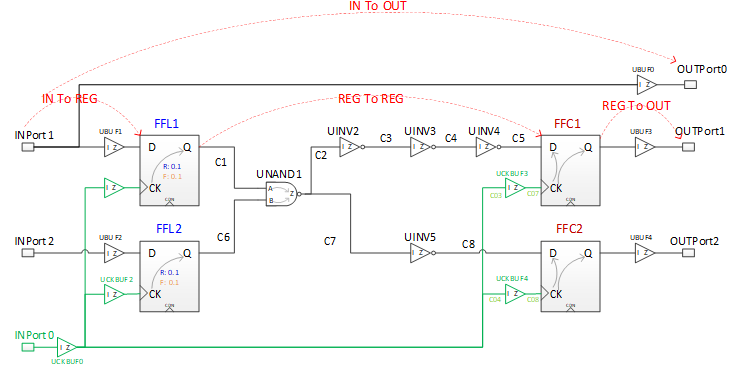

STA分析時,所有時序路徑都有起點和終點,起點包括輸入端口和時序單元的時鐘端口,終點包括輸出端口和時序單元的數據輸入端口。所以總共有4種路徑集合,即:

a. 從輸入端口到輸出端口(IN To OUT);

b. 從輸入端口到時序單元的數據輸入端口(IN To REG);

c. 從時序單元的時鐘端口到時序單元的數據輸入端口(REG To REG);

d. 從時序單元的時鐘端口到輸出端口(REG To OUT)。

4種時序路徑請見圖三:

圖三 時序路徑

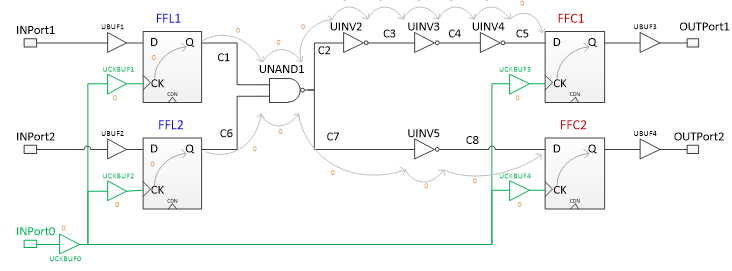

Timing Arc 概念

如圖三所示,每個cell都存在多條Timing Arc,如UNAND1存在A->Z和B->Z這2條Timing Arc。FFC1也存在CK->Q和CK->D 2條Timing Arc。

其中UNAND1的A->Z和B->Z是組合路徑Timing Arc。FFC1的CK->Q是edge Timing Arc,FFC1的CK->D又含setup arc和hold arc。

-

寄存器

+關注

關注

31文章

5347瀏覽量

120498 -

FFC

+關注

關注

0文章

58瀏覽量

17665 -

STA

+關注

關注

0文章

51瀏覽量

18980

發布評論請先 登錄

相關推薦

VIVADO時序約束及STA基礎

靜態時序分析在高速 FPGA設計中的應用

靜態時序分析基礎與應用

FPGA進行靜態時序分析

FPGA靜態時序分析詳解

STA-0.靜態時序分析概述

STA分析—時序檢查

STA分析—時序檢查

評論