PCIe技術,數據交互的高速公路

PCIe總線的前身是PCI(Peripheral Component Interconnect)總線協議,由英特爾于1992年提出,并聯合業界合作伙伴成立了名為PCI-SIG (PCI Special Interest Group)(PCI 特殊興趣組J)的企業聯盟,負責PCI總監的標準制定和推廣。

PCI提出的目的是簡化主板的總線接口,并提高數據傳輸總線的性能。由于PCI總線跟ISA總線都使用了并行總線設計,所以傳輸速度會受到影響。此外,PCI總線由于采用了帶寬共享機制,因此在高負載下會出現設備之間會搶帶寬的現象。最后,由于PCI不支持熱插拔,因此也不能更好的支持更換磁盤的操作。

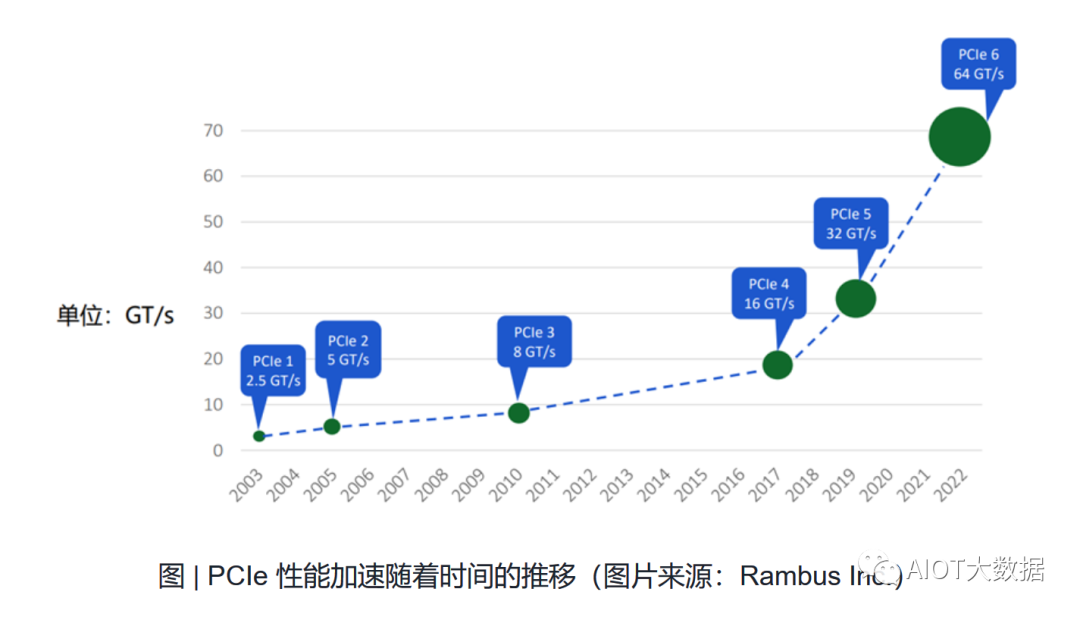

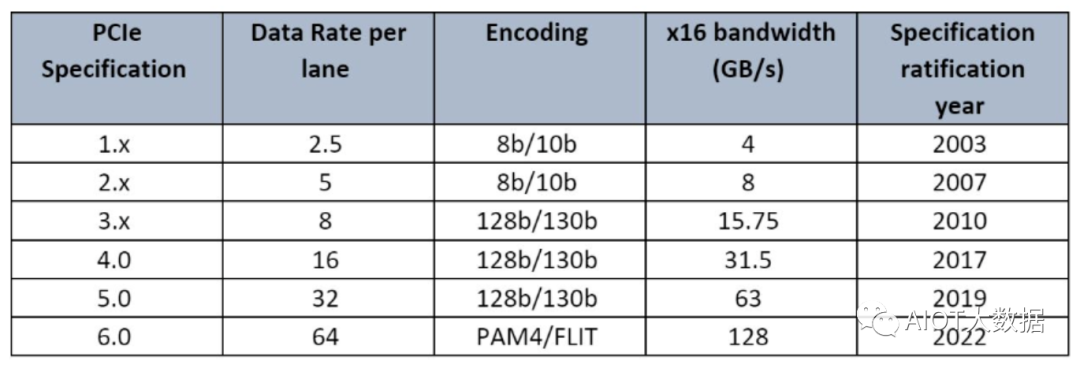

為了解決PCI總線的缺陷,2004年英特爾聯合伙伴對PCI技術進行了升級,正式發布了PCI Express(簡稱PCIe)總線,并陸續推出了PCIe1.0、PCIe2.0、PCIe3.0、PCIe4.0、PCIe5.0和PCIe6.0規范,不斷的進行帶寬優化。

實際上,近兩年火爆的CXL技術,其底層就是基于PCIe技術。隨著大數據分析、視頻渲染等技術的飛速發展,以及異構計算模式的興起,對于CPU與GPU、CPU與DPU等之間數據交互的帶寬提出了更高的要求。于是,PCIe 6.0 標準應運而生。

受到人工智能/機器學習(AI/ML)和數據中心、云、高性能計算等數據密集型應用的驅動,數據中心架構正在持續演進,這對PCIe接口提出了更高的要求。作為CPU與存儲之間的連接通道,PCIe自推出以來始終扮演著重要的作用。隨著大數據分析、視頻渲染等技術的飛速發展,PCIe6.0標準于去年初正式發布,相比較上一代PCIe 5.0規范,帶寬再次翻倍,達到了64 GT / s。

PCI Express 6.0 (PCIe 6.0) 規范由 PCI-SIG 于 2022 年 1 月發布。最新一代的 PCIe 標準帶來了許多激動人心的新功能,旨在提高計算密集型工作負載的性能,包括數據中心、 AI/ML 和 HPC 應用程序。

雖然PCIe 5.0正在廣泛流行并被主流設計所采用,但業界急切地等待PCIe 6.0的推出。好消息是PCIe 6.0帶來了更高的性能和一系列新特性,包括64GT/s的數據速率,采用具有吞吐量和延遲優勢的 FLIT,以及新的低功耗狀態L0p,實現了真正的帶寬擴展來降低功耗。

自 PCIe 3.0 以來,每一代新標準的數據速率都翻了一番。 PCIe 6.0 將數據速率提高到每秒 64 千兆傳輸 (GT/s),是 PCIe 5.0 的兩倍。 對于顯卡和網卡典型的 x16 鏈路,鏈路帶寬達到每秒 128 GB (GB/s)。 與前幾代產品一樣,PCIe 6.0 鏈路是全雙工的,因此它可以同時在兩個方向上提供 128 GB/s 的帶寬,總帶寬容量為 256 GB/s。

PCIe 除了已經廣泛擴展到服務器和 PC 之外,其規模使其對物聯網、汽車、醫療和其他領域以數據為中心的應用程序具有吸引力。 也就是說,PCIe 6.0 的初始部署將針對需要盡可能高帶寬的應用程序,這些應用程序可以在數據中心的核心找到:AI/ML、HPC、網絡和云圖形。

下圖顯示了 PCIe 規范隨時間的演變:

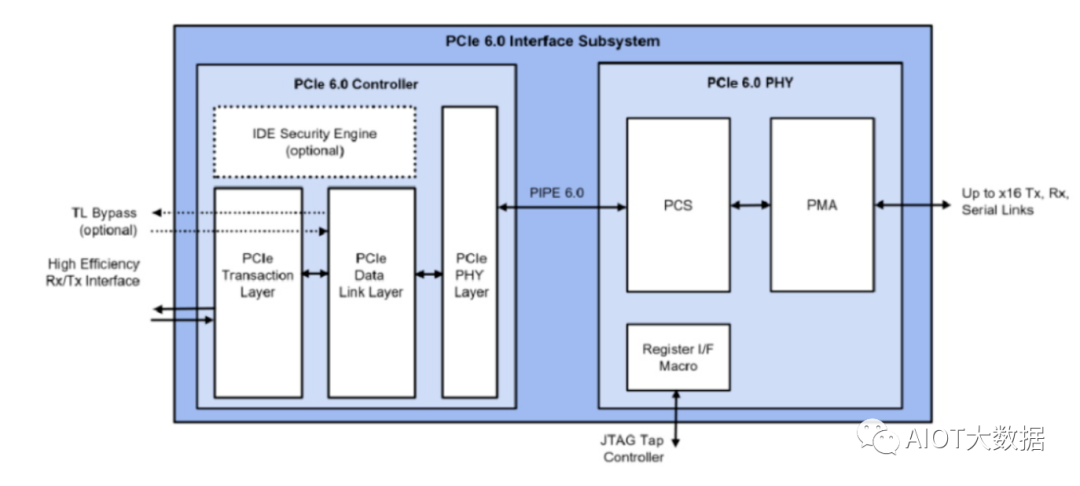

芯片設計周期通常都非常長,而通過采用PCIe 6.0接口子系統,可以降低芯片設計人員的設計復雜性。這是因為在過去,芯片設計人員需要把PHY和控制器單獨拿來使用,同時還要重復一些冗雜的驗證工作,而現在PCIe 6.0接口子系統集成了控制器和PHY,可以直接在其芯片中實施。

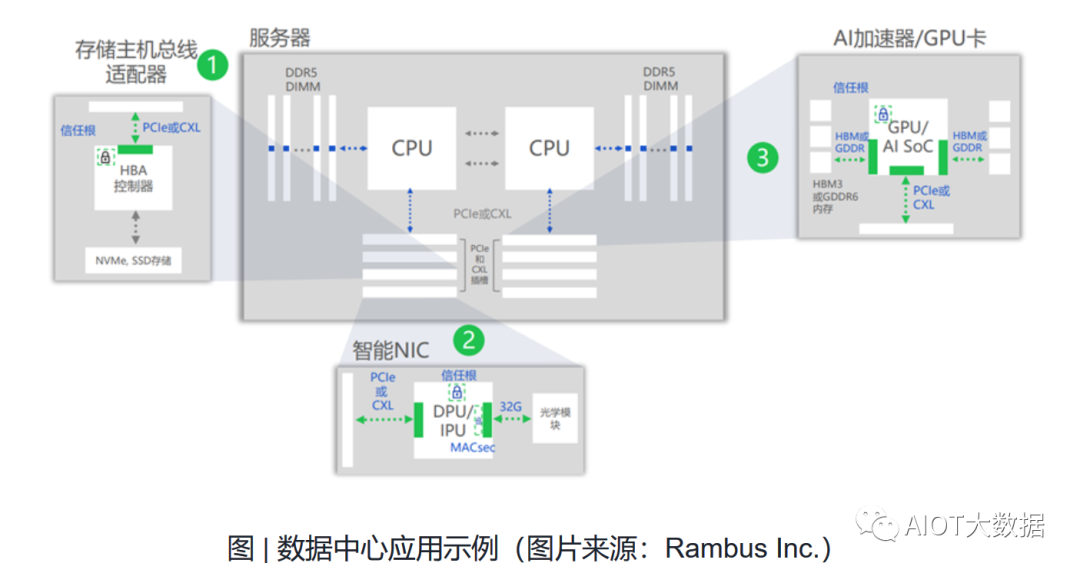

以數據中心三個應用為例,每個示例都有一個存儲主機總線適配器、一個智能網卡和一個AI加速器或GPU卡。我們看到,PCIe PHY和控制器的組合提供了一個成熟的接口,可以從服務器主板上的PCIe插槽和物理接口連接到控制器芯片上。這三個例子都保證了PCIe或CXL接口是經過硅驗證的,并且不會增加設計復雜性。

PCI Express(PCIe)6.0對于高性能計算、AI和存儲SoC開發者來說,理解并考慮如何最好地應對即將面對的關鍵變化,以及由此帶來的設計挑戰變得至關重要。這些變化包括從非歸零(NRZ)轉換到脈沖幅度調制4(PAM-4)信號導致對噪聲的敏感性增加,轉向FLow控制器unIT(FLIT)導致控制器行為和性能的變化,PHY與控制器之間緊密集成的需求,以及針對互操作性和測試的規劃。

確保順利成功地過渡到PCIe 6.0,開發者需要考慮的PCIe 6.0的三個主要變化如下:

數據速率從32GT/s翻倍至64GT/s

從NRZ編碼轉換到PAM-4編碼,以及由此帶來的糾錯影響

從傳輸的可變大小TLP到固定大小FLIT

前兩項變化緊密相關,并且受到要傳輸PCIe 6.0信號的通道性質的影響。

除了這三項變化之外,本文還將簡要介紹其他一些新特性,例如旨在允許功率/帶寬擴展的新的低功耗狀態L0p,以及支持的標簽數量從PCIe 5.0中的768個(10位標簽)擴展到PCIe 6.0中的15,360個(14位標簽)。

通道和PAM-4

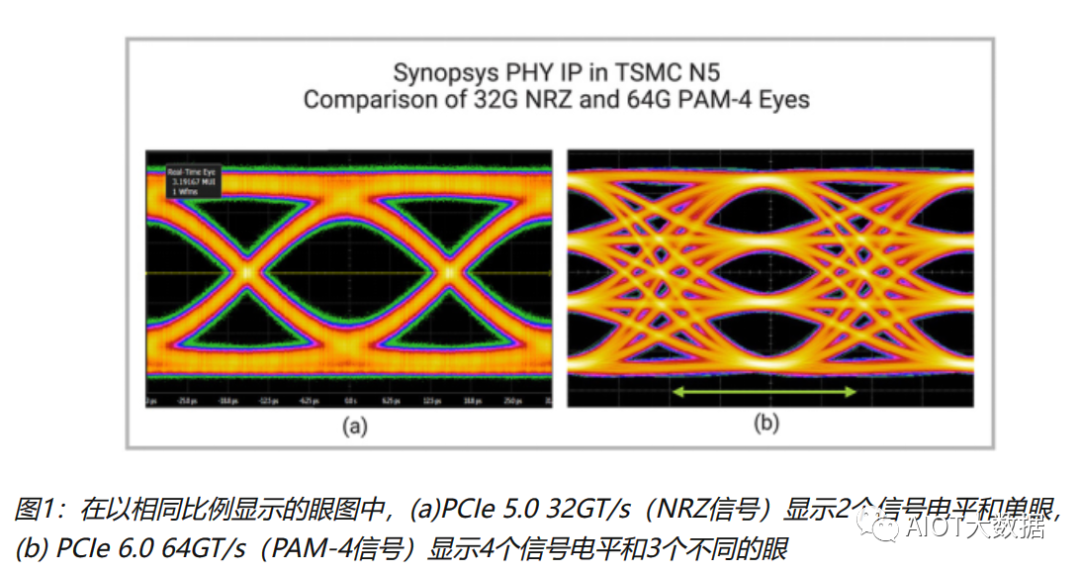

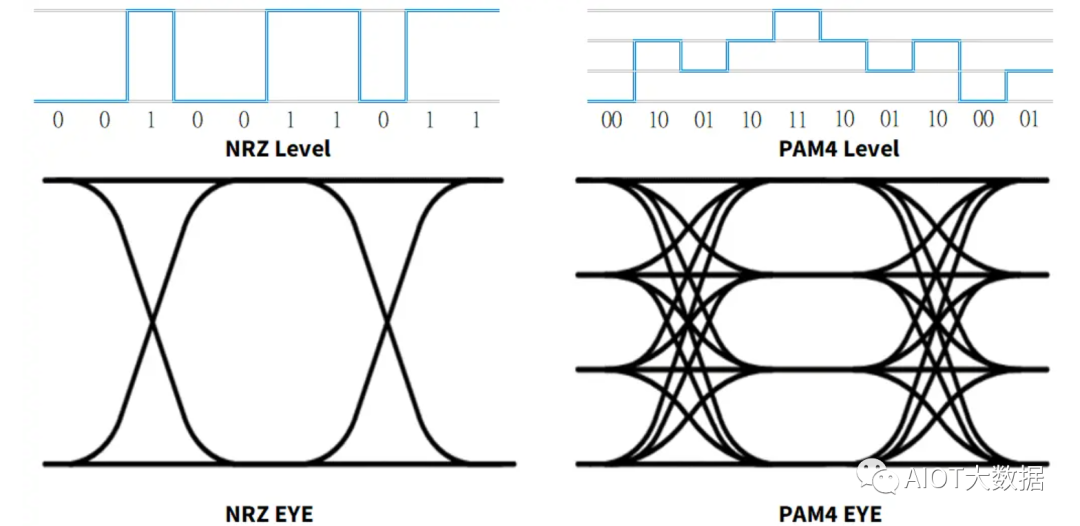

當數據速率從16GT/s加倍到32GT/s時,奈奎斯特頻率也從8GHz加倍到16GHz,使得PCIe 5.0(第5代)的頻率相關損耗比PCIe 4.0(第4代)嚴重得多。再加上電容耦合(噪聲和串擾)的增加,使得PCIe 5.0通道成為最難處理的NRZ通道。如果PCIe 6.0仍然保留NRZ信號,則奈奎斯特頻率將增加到32GHz,通道損耗大于60dB,這對于實際系統而言太大了,因此需要從NRZ更改為PAM-4信號。這一變化意味著發射和接收的信號現在有四個不同的電壓電平,而不是兩個,如圖1所示。

圖1(a)顯示了使用NRZ信號的PCIe 5.0的眼圖,包含兩個電壓電平和單眼。圖(b)顯示了使用PAM-4信號的PCIe 6.0的眼圖,包含四個電壓電平和三眼。圖1中的兩個信號具有相同的16GHz奈奎斯特頻率和相同的單位間隔(UI)。這意味著他們基本上可以使用相同的PCIe 5.0通道,而不會讓頻率相關損耗變得更糟糕,如果使用64GT/s的NRZ信號,奈奎斯特頻率為32GHz。這就是56G和112G以太網轉換到PAM-4信號的原因,也是PCIe 6.0現在轉換到PAM-4的原因,可以降低信號損耗。但是PAM-4的四個電壓電平在一個UI中使用2bit編碼,而NRZ是1bit編碼,從而使數據速率提高了一倍。這聽起來很棒,但是這里有一項重要的權衡因素。由于發射端(TX)的總體電壓擺幅沒有增加,因此PAM-4系統中每只眼的可用電壓僅為NRZ的1/3。因此,信號在TX和接收端(RX)之間遇到的任何噪聲都會對信號完整性造成更大的損害。

轉變為PAM-4信號使得RX的工作更加困難,因為眼不僅在電壓域要小得多(約 1/3),而且在時域也要小得多,而且這么多的轉換必須嵌入同一個UI中。如圖1 所示,這很明顯。圖1(b)底部的綠色箭頭顯示了NRZ眼的相對寬度,表明PAM-4 的眼寬度明顯小于NRZ的眼寬度。因此,使用PAM-4時,時鐘和數據恢復更加困難,需要更好的RX設計。PAM-4的大多數設計(包括即將推出的PCIe 6.0設計)將在RX中配置一個模數轉換器(ADC),以更好地滿足PAM-4的多電平信號需求以及對傳統NRZ的支持。這意味著數字濾波是完全開放的,一個RX對另一個RX使用特定的數字信號處理(DSP)算法,再疊加針對不同通道的模擬和數字均衡的仔細平衡,將區分PHY性能。此外,更窄的PAM-4眼意味著PCIe 6.0上的TX抖動性能需要比PCIe 5.0上好2倍左右,開發者應該仔細考慮這些因素。

從NRZ信號轉換為PAM-4信號還會顯著影響封裝和電路板設計,因為更改為四個電平信號會導致信噪比(SNR)立即退化9.6dB,因此正確管理噪聲變得更加關鍵,即使奈奎斯特頻率相同,封裝和電路板設計中的串擾和回波損耗也比PCIe 5.0高。噪聲敏感性增加意味著我們用于PCIe的1e-12誤碼率(BER)不可行,并且需要前向糾錯 (FEC),因為PAM-4信令的BER將比1e-12高幾個數量級,第一位誤碼率(FBER)的目標是1e-6。在其他標準(如以太網)中,使用強大的FEC來獲得可接受的BER,但代價是帶來100ns量級的大量額外延遲,這對PCIe來說是不可接受的。

由于FEC延遲和復雜性會隨著需要糾正的符號數量的增加而增加,并且由于PCIe 6.0的延遲目標非常苛刻,因此使用了輕量級FEC,并與使用循環冗余碼(CRC)檢測錯誤的PCIe的重試能力相結合,以便數據包可以重新發送或重試。PCIe 6.0的輕量級FEC可以產生1e-6級的重試概率,并且與更強的CRC結合使用時,整個系統可以提供穩定、接近無誤的性能,對往返時延的影響非常小(通常約為2納秒)。這意味著開發者可以使用與PCIe 5.0基本相同的延遲預期進行設計,對于許多情況,例如大于128字節(32DW)的事務層數據包(TLP),相對于PCIe 5.0將獲得顯而易見的實際延遲改進。

FLIT

開發者需要考慮的另一個重要問題是轉換到使用FLIT作為數據交換單元,而不是使用可變大小的TLP。由于PAM-4編碼的更改和FEC需要將誤碼率提高到可接受的水平,因此這是必要的,這樣CRC和重試機制可以讓路給可接受的錯誤率和系統延遲。FEC僅適用于固定大小的數據包,因此PCIe 6.0采用了256字節FLIT作為標準大小的數據傳輸單元。為了保留現有通道的PCIe 5.0,需要對PAM-4進行更改,這需要添加FEC,相應地需要轉換到FLIT。使用FLIT對系統有影響,因為一些FLIT可能有來自多個TLP的數據,而其他FLIT可能只包含TLP的一部分,并且底層TLP的大小仍可以在0到4096B(1024個DWORD)之間變化。

另一個影響是,一旦設備進入FLIT模式(例如,通過協商必須支持FLIT的PCIe 6.0鏈路進入),則無論鏈路質量有何變化,它都必須保持FLIT模式。因此,如果由于通道不穩定而需要降低鏈路速度,則新協商的較低數據速率將保持FLIT模式。這意味著在PCIe 6.0中,需要支持的所有可能的速度都有FLIT模式。

隨著在PCIe 6.0中引入新的FLIT模式,TLP和數據層數據包(DLP)包頭格式發生了變化,應用程序需要理解并正確處理這些變化。例如,對于PCIe 6.0,FLIT包含自己的CRC,因此數據鏈路層數據包(DLLP)和TLP不再需要像在PCIe 5.0和前幾代中那樣的單獨CRC字節。此外,由于FLIT的大小固定,因此無需使用前幾代(非FLIT模式)中的PHY層成幀令牌。與PCIe 5.0相比,這提高了帶寬效率。

新的低功耗狀態用于FLIT模式的L0p

PCIe 6.0引入了一種新的低功耗狀態,稱為L0p,允許PCIe 6.0鏈路在不中斷數據流的情況下擴展帶寬利用率,從而降低功耗。在前幾代中,為了改變鏈路寬度,整個鏈路重新訓練時,流量會中斷幾微秒,但L0p允許鏈路關閉通道,從而降低功耗,同時始終保持至少一個通道處于活動狀態,即使其他通道正在進行鏈路訓練。需要注意的是,這種新的低功耗模式僅在FLIT模式下可用,而L0s支持非FLIT模式。

這種新的低功耗模式是對稱的,這意味著TX和RX一起縮放,并且支持FLIT模式的重定時器也支持這種模式。在處于L0p期間空閑通道的PHY功耗預計與關閉通道時的功耗相近。

PCIe 5.0~6.0相比PCIe 1.0~4.0速率高,SI、PI要求也有提高。電源方面,插卡最大功耗可提升至600W,將在6.0 CEM中更新;信號方面為保證信號完整性要求使用表貼連接器;互連通道方面,與PCIe 5.0類似,要求主板支持約12 inch,插卡支持約3-4 inch,可以想象下,如果PCIe 6.0仍舊采用NRZ調制格式,64GT/s速率奈奎斯特頻點在32GHz,那么通道IL將小于-60dB(參考下圖通道仿真結果),很難通過現有技術實現該信號的高頻補償,考慮實現成本和技術復雜度,采用高階調制PAM4是種不錯選擇,相比PCIe 5.0奈奎斯特頻率不變,當前可用板材下可傳輸相似距離。

在64GT/s下保持性能

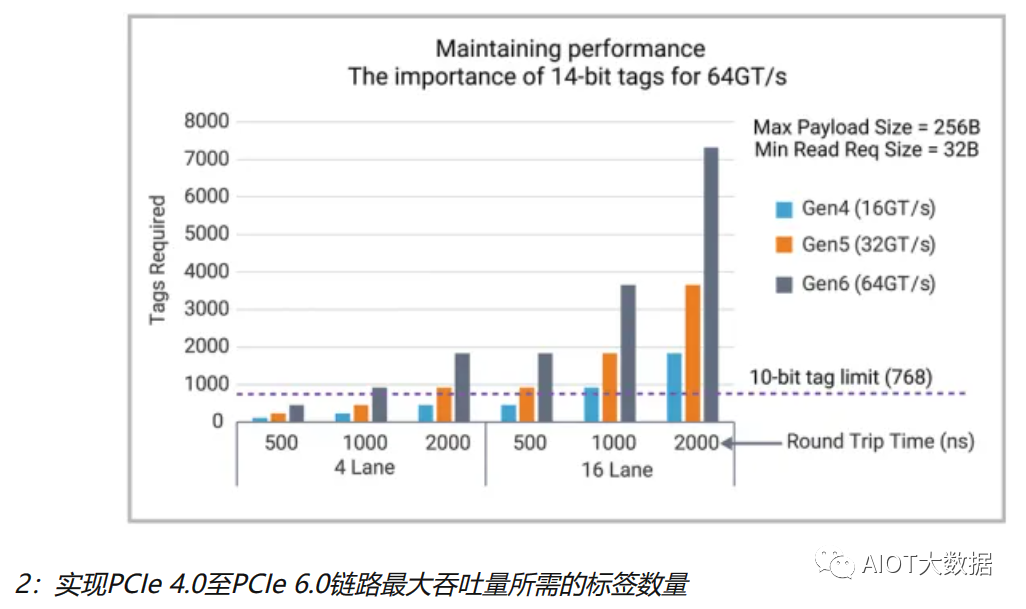

為了在PCIe系統中實現最佳性能,開發者需要確定系統必須處理的未發布請求(NPR)的最大數量,以保持數據暢通,這取決于有效負載大小以及總往返時間(RTT)。該數量轉換為可用標簽的數量,并且是必須根據系統需求正確設置的控制器屬性。對于PCIe 6.0,隨著數據速率再增加一倍,以前的768個標簽限制已經遠遠不夠,因此標簽數量最大值急劇增加,變為基于14位的15,360個標簽。這樣即使在往返時間較長的情況下也可以實現高效的性能,并且具有很大的余量,可以在將來實現更快的數據速率。

圖2顯示了各種RTT的PCIe 4.0、5.0和6.0數據速率所需的標簽數量,以保持256B 有效負載和32B最小讀請求大小的最大吞吐量。如圖2所示,PCIe 5.0的768個標簽限制遠遠不足以支持大多數PCIe 6.0系統的性能。這應該在作為系統片上(SoC)設計的一部分的PCIe 6.0控制器的配置過程中進行仿真和驗證,以確保能夠實現預期的性能。

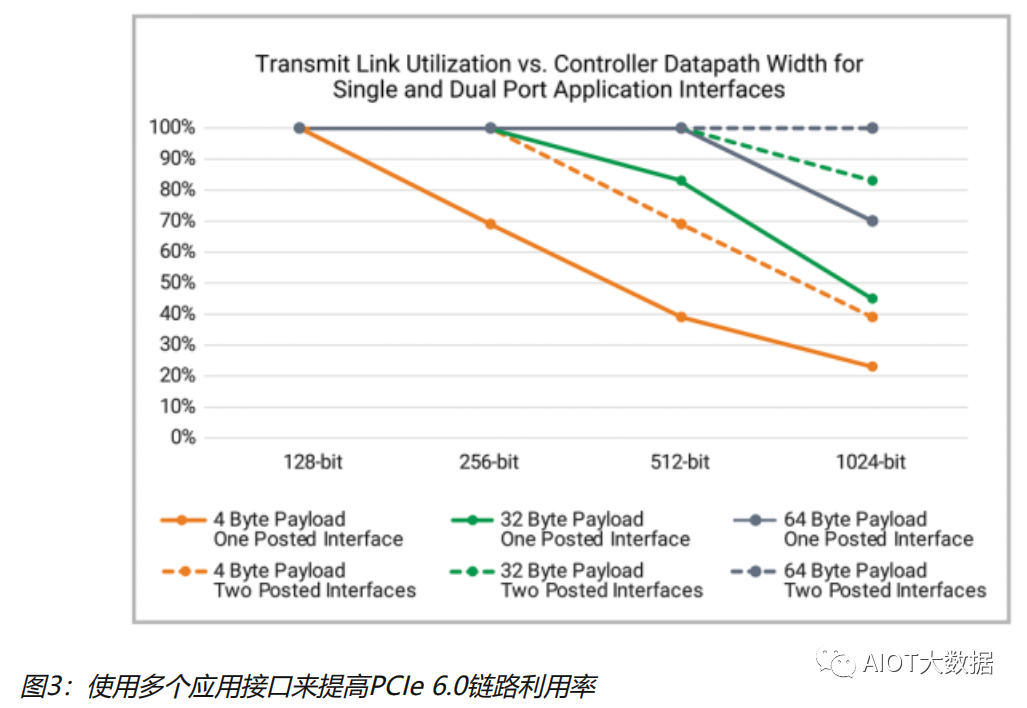

要考慮的第二個因素是如何確保應用能夠有效地利用PCIe 6.0的大量可用帶寬。通常,應用程序通過帶有3個獨立接口的控制器連接到PCIe:分別用于已發布、未發布和已完成事務。對于64GT/s PCIe 6.0,各種情況的分析表明,使用單個接口將導致鏈路利用率或帶寬效率(實現的帶寬相對于理論帶寬)的顯著損失。對于較小的數據路徑寬度和較小的負載大小,此問題最為嚴重。

如圖3所示,對于傳統的單應用接口和雙應用接口(用于已發布事務),PCIe 6.0 在各種數據路徑寬度和有效負載大小下的傳輸鏈路利用率。在1024b數據路徑的32字節有效負載的情況下,使用單個已發布接口而不是兩個接口導致鏈路利用率下降54%。這意味著在這種情況下,使用帶有單個應用接口的控制器將獲得相當于PCIe 5.0的性能。

PHY和控制器集成

為了實現最佳性能、最低延遲和簡化集成,通過單一供應商來實現PHY和控制器IP的完整解決方案是有利的。如果這不可能,PIPE接口的細節就比較關鍵。PIPE 5.x 接口規范不支持PCIe 6.0,因此必須指定較新的版本PIPE 6.0。現在看來,PCIe6.0 的大多數設計將采用基于新PIPE 6.0規范的SerDes架構PIPE接口。這簡化了PHY 設計,還使PCIe 6.0PHY在推出時能夠支持CXL 3.0的低延遲要求。

在PCIe 6.0中,仍然需要權衡數據路徑位寬和PIPE接口處時序能夠收斂的頻率。對于要求最大的PCIe 6.0帶寬和16通道配置的應用,只有兩個可行的選擇。為了使時序能夠收斂在1GHz,需要使用64b PIPE,這又需要1024b PCIe 6.0控制器架(16 通道x64b=1024b)。這是PCIe 6.0的一個新特性,因為前代PCIe沒有1024位架構可用。

另一個選擇是使用32位PIPE并堅持使用512位架構。這意味著在PHY控制器接口上以2GHz來收斂時序。雖然大多數SoC開發者不太可能首選這種架構,但如果開發者想要在非常快的CMOS過程中實現最小的延遲,那他們就有可能會這么選擇,因為將bit時鐘的周期時間減半,可以提供比1GHz時序更小的延遲。

測試和調試注意事項

對于量產設備,64GT/s速率的生產測試需要能夠驗證鏈路的快速測試,此類測試通常使用內置環回模式、數據圖形發生器和接收器(集成在PHY和控制器IP中)。在PHY中支持PAM-4的環回比NRZ更復雜,但很重要,應將其視為可測試性解決方案的一部分。

對于實際硅片中的調試和質量監測,能夠監測硅片中的FBER對于一個系統的實際鏈路質量也非常有益。可以與內置scope功能結合使用,通常合并入PCIe 6.0 PHYIP,以獲得對TX和RX之間更詳細的理解。

像PCIe 6.0這樣的新規范需要進行更魯棒的系統測試,針對調試、錯誤注入和統計監測功能提供內置控制器支持非常重要。這有助于不確定是否能夠正確地開發固件和軟件,以預測可能遇到的任何潛在的實際系統問題。

PCIe 6.0先行者——固態存儲

要實現這種未來科技,增加數據帶寬非常重要。帶寬也就是單位時間內網絡從某一點到另一點所能通過的”最高數據率”,常用的單位是bps,即每秒多少比特。隨著高性能計算(HPC)、超大規模數據中心、人工智能/機器學習(AI/ML)、自動駕駛、物聯網(IoT)等領域對先進應用的需求不斷增加,帶寬需求曲線依舊呈現不斷上揚的趨勢。

新的PCI Express (PCIe )6.0規范正是一種能夠輔助開發者們實現未來科技的關鍵技術。PCIe 6.0堪稱是迄今為止最重要的PCIe協議創新。

PCle 6.0是如何實現帶寬飛躍的?

PCIe 6.0的帶寬是上一代的2倍,具有以下特性:

每個引腳的數據傳輸速率可高達64GT/s

通過新的低功耗狀態提高電源效率

經濟高效的性能

高性能的數據加密與完整性

向后兼容之前的版本

PCIe 6.0實現帶寬飛躍的一種方式就是改變電氣信號調制方案,即從傳統的不歸零(NRZ)信號轉變為使用脈沖幅度調制技術的四電壓電平(PAM-4)信號。

在前幾代PCIe中,NRZ位在每個單位時間間隔(UI)中是以1或0的形式串行傳輸的。而采用PAM-4時,則可以在與NRZ相同的單位間隔中獲得四個值。由此,無需讓信號速率加倍,即可實現數據速率翻倍。四個電壓電平將生成三個眼圖,而眼圖高度和眼圖寬度則有所減小。為了減少信號中的錯誤,PCIe采用了格雷編碼,即一次只改變一位。對于模擬信號,預編碼有助于減少錯誤。而對于數字信號,前向糾錯(Forward Error Correction)可降低誤碼率。

但是,這樣難道不會顯著增加延遲嗎?

并不會。因為PCI-SIG提出了一種簡潔的方式來實現輕量級FEC,它利用了現有的重試機制,因此不會導致延遲問題。

與PCIe 5.0相比,PCIe 6.0可提供更高的帶寬(2x),但由此增加的延遲卻幾乎為零。

流量控制單元很重要

在PCIe 6.0中,事務傳輸層概念(the transaction layer concepts)使用了與前幾代相同的命令。新的包頭格式雖然在根本上與前幾代并無不同,但組織結構卻更為精簡。新的包傳送方法讓協議徹底重組,這種重組不僅支持更高的帶寬,系統還可以通過共享流量控制授權等功能對帶寬進行處理。

PCIe 6.0使用流量控制單元(FLIT)來傳輸數據,無需編碼。以2.5G為例,由于編碼的原因,8位數據在線路上會變成10位。對于8G而言,128位數據在線路上會變成130位。另一方面,FLIT完全無需進行編碼。這意味著每個1位數據在線路上也是1位。因此,PCIe 5.0中通過編碼執行的功能和特性,在PCIe 6.0中將由于擾碼多項式以及 FLIT 包頭的更改而被涵蓋。

PCle 6.0通道可進入“睡眠”

PCIe 6.0所需的低功耗狀態是新的L0p,雖然L0p可以向后兼容前幾代的L0s,但64GT/s的FLIT模式速率還是要求使用 L0p。這種新的低功耗狀態的創新之處在于,一些通道可以進入睡眠狀態(相當于電氣閑置),而數據可以繼續在非閑置通道上進行傳輸。要支持L0p,還需要支持FLIT模式的重定時器。L0p的優勢在于開發者可以根據實際使用的帶寬來擴展電源。

保護數據和系統的安全

互聯程度越來越高,數據和系統漏洞的攻擊面就越大,攻擊者的動機現在也越來越難以揣測。正因如此,越來越多的法律法規還要求電子系統具有更高的安全性。在此背景下,PCIe 6.0采用了數據完整性和安全保護機制,其在安全方面的亮點主要體現在以下三個方面:

數據對象交換(DOE)

這不是一種性能模式,而是一種安全模式,也并非出于高性能目的,這是一個PCIe用于增強其他領域安全性的低級別構建模塊。DOE是一種基于配置空間寄存器來傳輸主要加密數據和密鑰的簡單機制,它與應用邏輯緊密結合。

組件測量和認證(CMA)

借助此安全功能,設備中的固件可為設備提供加密簽名。收到CMA報告時,開發者可以驗證簽名是否準確。如果不準確,他們就需要解決相應的安全問題。

完整性和數據加密(IDE)

這一安全措施主要是為了防止物理訪問攻擊。這項保護是為了防止有人嗅探PCIe 6.0 FLIT數據包,并對數據包進行插入和刪除操作。這一安全保護機制有兩種模式:第一種是Link IDE,相應的數據將在發送端加密,然后在直連設備的接收端解密。第二種是選擇性IDE,相應的數據包將通過交換機傳輸,在請求者那里加密,并經過若干中間設備中轉后在請求完成時解密。由于這種安全模式作用于PCIe的“核心”數據包級別,因此它需要與控制器緊密結合,以便以64GT/s的速率高效地實現加密和解密功能,同時將延遲影響降至最低。此外,開發者還需要有多個管道化AES-GCM加密引擎來滿足吞吐量要求。

PCIe 5.0與PCIe 6.0在安全特性方面的主要區別在于帶寬擴展、對FLIT模式的支持,以及對新包頭格式的支持上。另外還有一些安全特性即將推出,它們將同時支持PCIe 5.0和PCIe 6.0。可以這么說,隨著安全形勢的變化,安全防護措施也會不斷發展和完善。

PCle 6.0先行者:固態硬盤

雖然PCIe 4.0和PCIe 5.0正在普及,但固態硬盤(SSD)已經開始率先采用PCIe 6.0。

▲ PCIe是超大規模數據中心機架單元盒中的實際接口。這是一個盒內(計算)的示例:PCIe 是CPU、GPU、SSD、加速器和智能NIC應用的主要接口,并通過CXL保持緩存一致性。

以上圖為例,仔細觀察圖中機架單元的盒內結構,就會發現CPU與加速器及SSD相連,而加速器與智能網卡(NIC)相連,這些都屬于PCIe插槽。在從PCIe 5.0過渡到PCIe 6.0時,U.2外形尺寸將逐步被淘汰,PCIe 6.0很可能支持U.3、EDSFF(企業和數據中心標準外形尺寸)和OCP(開放計算項目)3.0。

由于SSD SoC與NVMe(非易失性內存主機控制器接口規范)或閃存以及根聯合體處理器相連,因此帶寬要求會非常高。但SSD會受限于SSD插槽的帶寬,而后者又受PCIe數據速率控制,這意味著SSD在同一通道下可獲得雙倍帶寬,而這也是SSD率先采用PCIe 6.0的原因所在,對于開拓市場,優勢很明顯。同時,面向根聯合體處理器的生態系統也已成形。

在Meta的推動下,開放計算項目(OCP)正在開發一種可用于所有接口的通用外形尺寸。NIC、SSD及其他組件一直都有自己的外形尺寸,而OCP的愿景就是讓所有這些接口都使用一種通用外形尺寸。參與Meta生態系統的公司正在開發采用OCP 3.0外形尺寸的設備,而PCIe 6.0將會支持該外形尺寸。

-

AI

+關注

關注

87文章

31155瀏覽量

269488 -

PCIe

+關注

關注

15文章

1243瀏覽量

82797 -

人工智能

+關注

關注

1792文章

47442瀏覽量

239005

原文標題:技術前沿:PCIe6.0助力AI人工智能應用

文章出處:【微信號:AIOT大數據,微信公眾號:AIOT大數據】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe6.0助力AI人工智能應用

PCIe6.0助力AI人工智能應用

評論