經典鎖相環結構小結

頻率合成器一般分為直接合成模擬式頻率合成器、鎖相環頻率合成器、直接數字頻率合成器(DDS)。其中鎖相環頻率合成器按照實現技術分為模擬PLL、數字PLL(ADPLL)、數模混合PLL。

這篇文章中主要講的就是比較常用的數模混合PLL(以下簡稱PLL)的兩種經典結構。

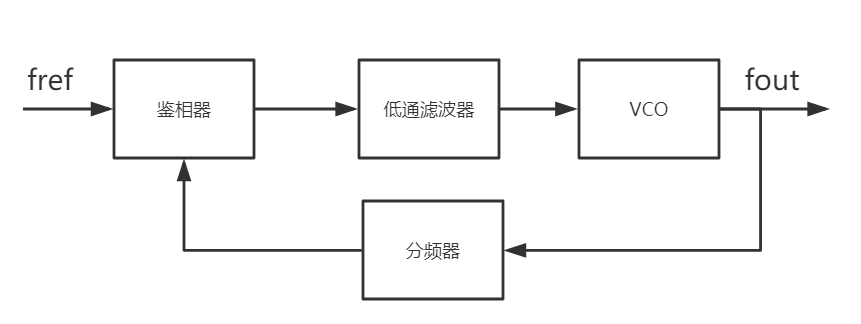

主要構成

PLL一般由PD(PFD)、LPF、VCO、分頻器等組成。

核心器件之鑒相器

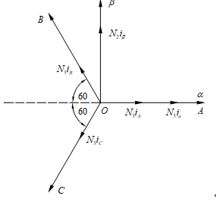

模擬鑒相器就是一個乘法器,通常由Gilbert乘法器單元構成,由于當兩信號相位差為 時,鑒相器的增益最大,又稱為正交型鑒頻器,同時環路的相位誤差

時,鑒相器的增益最大,又稱為正交型鑒頻器,同時環路的相位誤差 等于兩信號的相位差減去

等于兩信號的相位差減去 。當某一個輸出信號為方波或者由于輸入信號幅度很大類似方波時,需要對VCO的頻率范圍進行限制,防止環路鎖定到高階諧波頻率上,鑒相范圍為

。當某一個輸出信號為方波或者由于輸入信號幅度很大類似方波時,需要對VCO的頻率范圍進行限制,防止環路鎖定到高階諧波頻率上,鑒相范圍為 。

。

數字鑒相器主要為異或型鑒相器、時序型鑒相器、以及可鑒頻又可鑒相的鑒頻鑒相器PFD。

- 異或型鑒相器由數字異或門構成,穩定狀態類似模擬鑒相器,相位差為

時,鑒相器經過低通濾波器的輸出為0,環路相位誤差

時,鑒相器經過低通濾波器的輸出為0,環路相位誤差 為0。也要注意鎖定到高階諧波頻率上,鑒相范圍為

為0。也要注意鎖定到高階諧波頻率上,鑒相范圍為 。

。 - 時序型鑒相器可由JK觸發器構成,一般鑒相范圍為2

,環路鎖定時兩信號的相位差為0,穩定平衡點和不穩定平衡點的鑒相器增益差距較大,與異或型鑒相器相比,鎖定時間減小,但因為是邊沿觸發,需要保證J、K兩端的邊沿響應速度相同。

,環路鎖定時兩信號的相位差為0,穩定平衡點和不穩定平衡點的鑒相器增益差距較大,與異或型鑒相器相比,鎖定時間減小,但因為是邊沿觸發,需要保證J、K兩端的邊沿響應速度相同。 - 鑒頻鑒相器可以理解為在鑒相器的基礎上加一個鑒頻器,目的是在兩信號頻率差較大時,能夠鎖定,且減小鎖定時間,同時由于有鑒頻器的反饋作用,對于鑒頻鑒相器來說沒有捕獲范圍的限制,鑒相范圍為4

。

。

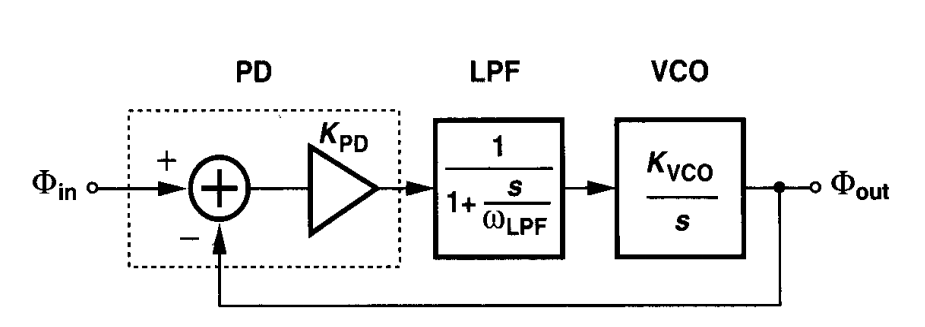

經典結構之I型鎖相環

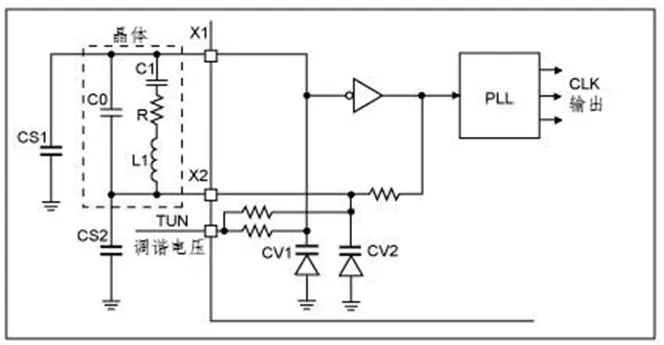

下圖所示的PLL是一個二階I型鎖相環。“二階”是因為低通濾波器為一階,Ⅰ型是因為環路增益在原點處有一個極點。

鎖定過程

兩輸入之間相位不同時,鑒頻器會輸出與相位差正比的寬脈沖,經過低通濾波器后,變為控制VCO振蕩頻率的控制信號,改變振蕩器的頻率,再反饋與鑒相器,在各個參數合適的情況下,最終使得輸出相位差減小為一穩態值,兩輸入信號的頻率相等。

主要問題

I型鎖相環需要在阻尼系數,低通濾波器帶寬與相位誤差之間進行折衷,或者說系統鎖定時間、系統穩定度、相位誤差、控制電壓的紋波之間需要折衷,而且這種類型的鎖相環只有 和

和 的差值比

的差值比 略小時才能鎖定。

略小時才能鎖定。

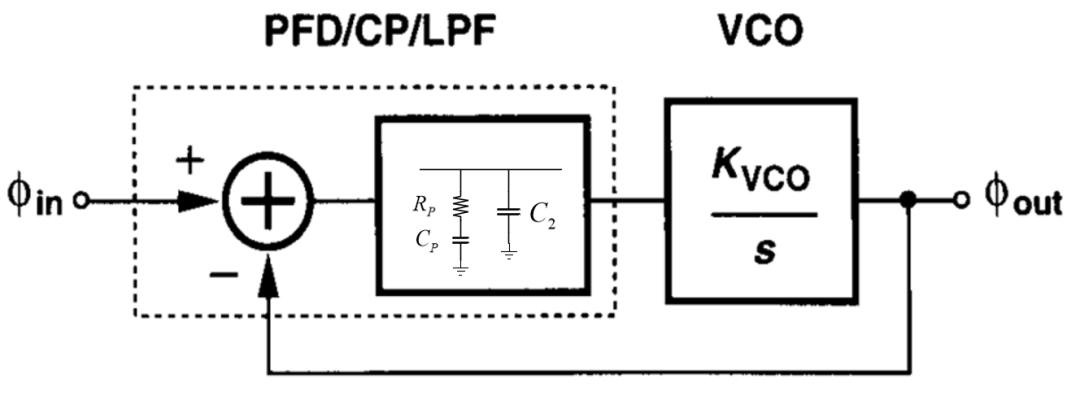

經典結構之II型鎖相環

上圖所示為三階II型鎖相環,由于鑒相器改為鑒頻鑒相器,又可稱為電荷泵鎖相環(CPPLL)。同理,“三階”是因為低通濾波器為二階,II型是因為環路增益在原點處有兩個極點。

鎖定過程

兩輸入之間相位不同時,鑒頻鑒相器、電荷泵和低通濾波器會產生和相位差、頻率差,正比的控制信號,改變VCO振蕩頻率,再反饋回去,在各個參數合適的情況下,由于鑒頻鑒相器中鑒頻作用,使得鎖定時間減小且捕獲范圍增大,同時又因為電荷泵直流增益較大,使得鎖定時,相位差趨于0,兩輸入頻率也相等。

與I型鎖相環的差異點

- 環路增益在原點處有兩極點,容易導致系統的不穩定,低通濾波器設計需要更加注意

- 環路的直流增益較大,相位差趨于0,且相位和頻率不會有太大的漂移;

- PFD/CP/LPF在原點有一極點,而I型鎖相環的PD/LPF沒有。

主要問題

-

鎖相環

+關注

關注

35文章

584瀏覽量

87739 -

頻率合成器

+關注

關注

5文章

219瀏覽量

32350 -

低通濾波器

+關注

關注

14文章

474瀏覽量

47390 -

DDS

+關注

關注

21文章

633瀏覽量

152631 -

PLL電路

+關注

關注

0文章

92瀏覽量

6403

發布評論請先 登錄

相關推薦

貼片機常用的兩種直線驅動結構

兩種不同結構的永磁同步電機特點說明

兩種典型的ADRC算法介紹

射頻與數模混合類高速PCB設計

兩種新型一維微帶開口環PBG結構

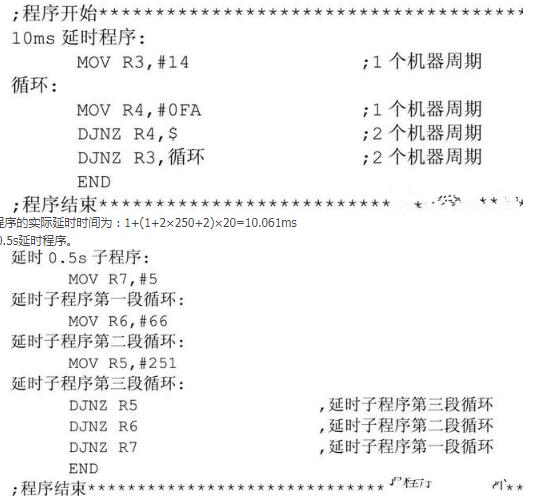

單片機常用的兩種延時控制方式

詳解PMSM中常用的兩種坐標變換

常用的數模混合PLL的兩種經典結構

常用的數模混合PLL的兩種經典結構

評論