Clock Latency簡介

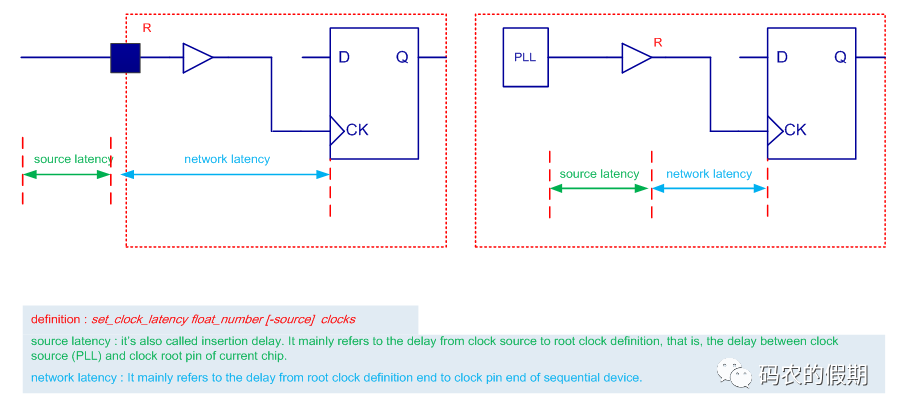

要探討今天的主題,首先需要跟大家一起學習下clock latency這個基本概念。Clock latency通俗意義上是指clock定義點到clock sink point(時序器件的clock Pin)之間的這段延遲時間。其分為兩類,其中一類為,source latency,另外一類是network latency。

**source latency ** :也稱作insertion delay,通常是指clock source端到clock定義點之間的這段時間延遲;通常有兩種情況,其一:clock 直接來自于芯片外部,如crystal clock,此時,source latency指的是芯片外部crystal出口到芯片PAD(假如clock定義在此處)之間的時間延遲;其二:clock 來自于芯片內部的PLL,此時,source latency指的是芯片內部PLL輸出點到芯片內部某個第一個clock定義點之間的這段時間。

network latency :其指的是clock定義點到clock sink point之間的這段時間。

這兩種latency是每一個clock的固有屬性,當CTS完成之后,每一個clock如果是在propagation狀態下,其source latency和network latency都是確定的。當然,在前期(PR之前或者CTS之前),通常情況下clock都處于ideal狀態,為了能夠模擬真實的情況,我們可以通過指令set_clock_latency去指定每個clock的source latency或者network latency,具體此指令的用法,我們這里不詳細解釋了,有興趣,有需要的可以自己去查閱相關資料。

圖1 clock latency 示例

圖1 clock latency 示例

create_clock和create_generated_clock的不同點簡介

通常定義clock的方式有兩種,create_clock和create_generated_clock。再上次有具體介紹過,這兩個指令的使用。那么他們之間有哪些使用上的區別以及各自都有什么特點呢?大體總結如下:

- create_generated_clock能夠繼承其master clock phase,換句話說:generate clock的邊沿(rise or fall)是通過繼承master clock得到的。

- create_generated_clock能夠繼承其master clock的source latency。

- 通常情況下,create_clock的source latency為0.(在不特殊指定的情況下)

- 每當設置一個create_clock,通常CTS時會構建一個新的clock domain。

Generate clock定義出錯引入的clock edge識別出錯

在上次,我們通過多個例子,分類說明了,如果generate clock定義不合理,會誤導工具做出錯誤的timing分析的各種情形。但是具體工具timing分析會是什么樣的呢?

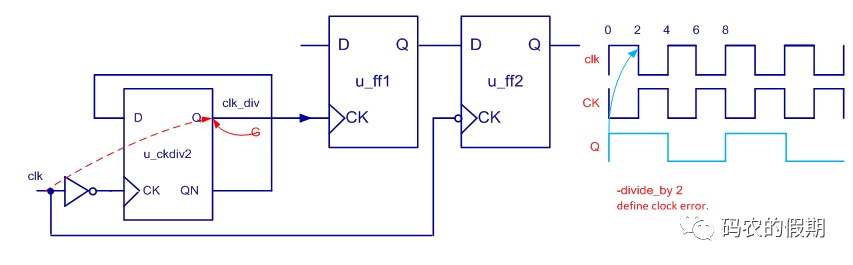

圖2 錯誤的定義generate clock示例

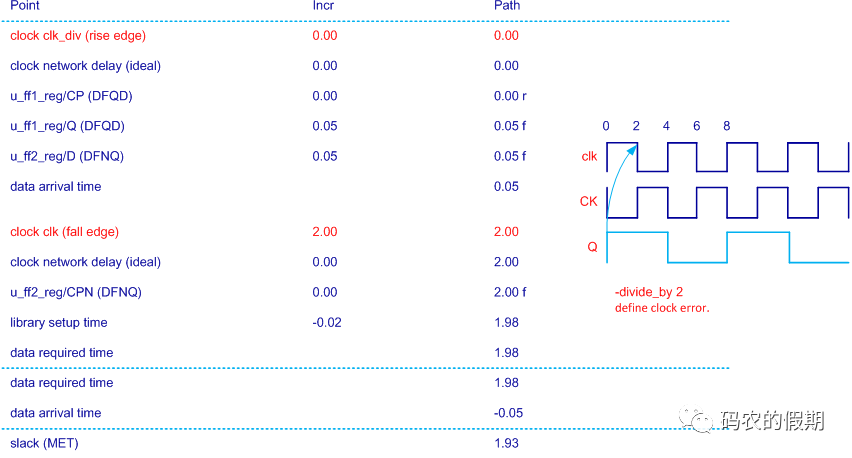

如圖2所示,如果直接在u_ckdiv2/Q點上,使用-divide_by 2 –master_clock clk的方式定義generate clock,那么工具認為的Q點的波形會是圖2中右圖所示的情況。這其實是與實際design的情況不符合的(假如DFF復位狀態為0)。這時工具會認為的timing path check情況會如圖3所示。從u_ff1/CK到u_ff2/D,整個timing path周期只有半個clk cycle。

圖3 錯誤的generate clock定義

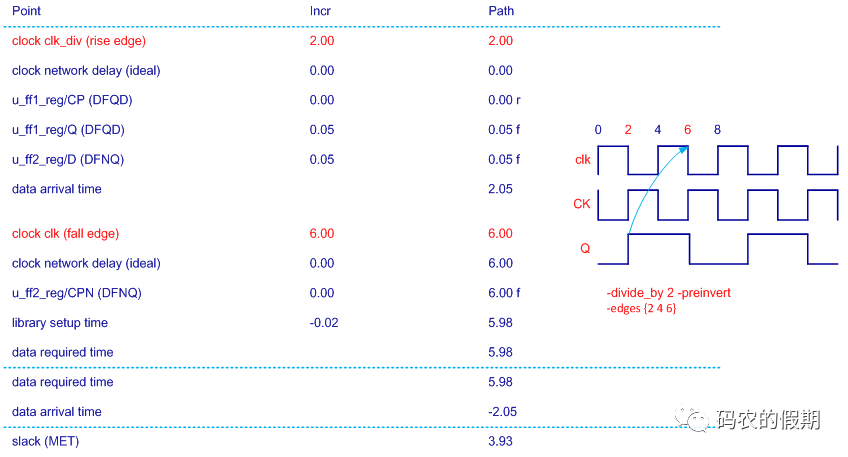

如果我們能夠正確的在Q-pin上定義generate clock,那么工具認為的Q-pin的波形會是圖4中所示的情形。這時同樣的timing path,從u_ff1/CK到u_ff2/D,工具做出的timing 分析會是圖4中的情形。

圖4 正確的generate clock定義

當然,通過上面這個例子,雖然clock定義不合理,但是錯誤的clock的定義,單從edge的傳播來看,其實是加緊了對design的約束,可能會浪費一些PPA,但是不會讓design最終因為timing出錯。

Generate clock定義出錯引入的latency計算出錯

其實,除了上面分析提到的會影響工具正確的判斷定義的generate clock的edge之外,還會可能影響到工具錯誤的計算clock的latency。

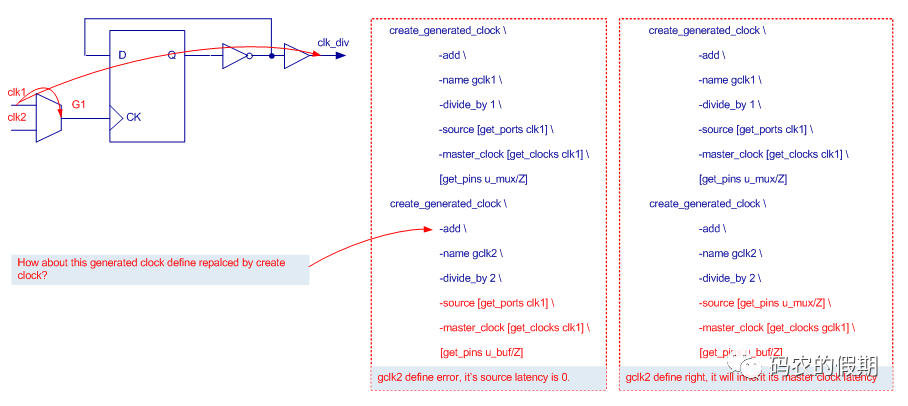

如圖5中的情形,如果采用圖5中(左,中,右)所示的定義方式,由于在mux的Z-pin上已經定義了generate clock gclk1,而在定義generate clock clk_div時,如果其master clock還指向了gclk1前面的一個clock-clk1,那么此時clock其實定義是不合理的。因為從clk_div往前追,看到的第一個clock是gclk1,而clk1被其打斷了,其clock屬性不能再正確的往后傳播。

圖5 錯誤的clock定義

也即上面提到的generate clock可以繼承其master clock的source latency這個特性就不能正確的保持了,從而導致工具認為此處定義的generate clock的source latency將從0開始計算。如果此處的generate clock替換為create clock會是怎樣的呢?大家可以思考一下。而如果想正確的繼承master clock的source latency,那么此處,可以按照圖5中右所示的方式定義clock。

Clock Group定義簡介

上面提到create clock定義時,會伴隨新的clock domain的創建,此時所提到的clock domain即指clock group。當然,clock group并不僅存在于create clock定義時,在generate clock定義時,也可以指定clock group。其主要目的是,人為的告訴工具,我們所定義的所有的clock之間的關系,從而減少工具自動化分析的情形,降低runtime,得到更好的PPA的結果。但是具體clock group怎么劃分,是需要按照design架構決定的。我們在此處,先不會深究為什么要區分不同的clock group以及clock group劃分的依據(后面其它系列文章中再做分析),而是跟大家詳細的解釋下定義clock group的方法以及注意點。

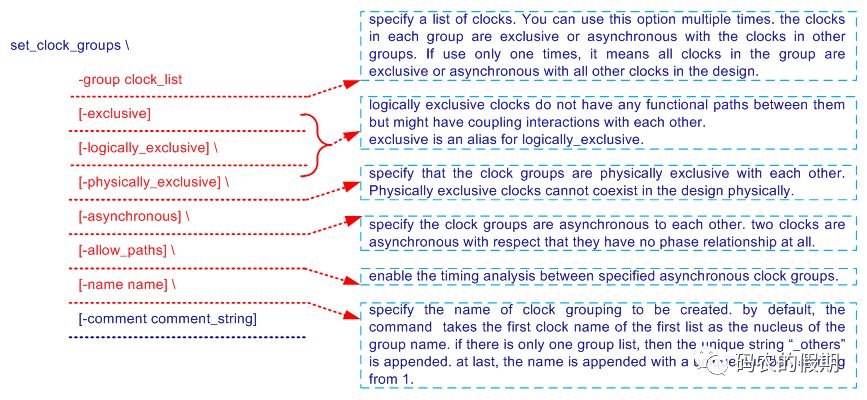

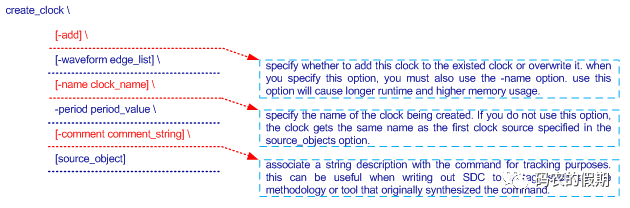

如圖6所示,定義clock group我們SDC中右一條指令其為set_clock_group,詳細的解釋在圖6中都已經給出,但是個人覺得還是有必要針對-logically_exclusive/-physically_exclusive/-asynchronous這三個option具體的分情況說明一下。

圖6 clock group定義

-logically_exclusive/-physically_exclusive/-asynchronous簡介

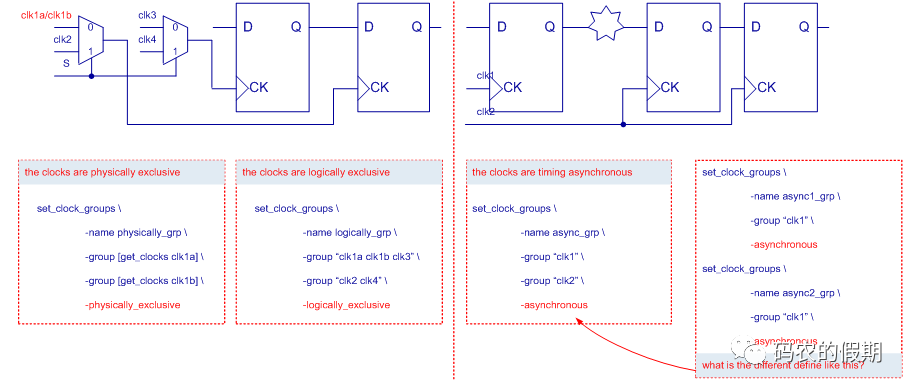

Logically_exclusive : 其含義是指兩組clock邏輯上不會同時存在。如圖7中第2框圖所示,雖然,clk1a/clk1b/clk2/clk3/clk4同時存在于整個design中,但是由于clock mux的select信號是相同的,所以從圖中可以看出,S=1,此時前后兩個mux分別選通clk2和clk4;如果S=0,則此時兩個MUX分別選通clk1a/clk1b和clk3,也就是clk1a/clk1b/clk3和clk2/clk4是邏輯上不會同時存在的。所以他們之間就是logically_exclusive。

Physically_exclusive : 其含義是指兩組clock之間物理上不會同時存在。如圖7中第1框圖所示。第一個clock mux中的clk1a和clk1b,這兩個clock是來自于相同的path,同一時間,這兩個clock物理上只有一個存在,所以他們便是physically_exlusive。

Asynchronous : 其含義是指兩組clock之間功能上異步的。如圖7中第3框圖所示,clk1和clk2,在功能設計時便是采用的異步方式設計的,即clk2跟clk1之間完全不需要關心相位或者frequency之間的關系,功能上也是正確的,這時候這兩個clock便是aysnchronous。當然aysnchronous的前提條件是design功能上要保證正確性。

圖7 clock group定義示例

圖7中,如果換成第4框圖中的定義方式,跟第3框圖中的定義方式會有什么異同點?這個大家可以自己思考一下…

-

PAD

+關注

關注

1文章

98瀏覽量

30680 -

PIN管

+關注

關注

0文章

36瀏覽量

6324 -

PLL電路

+關注

關注

0文章

92瀏覽量

6403 -

CTS

+關注

關注

0文章

35瀏覽量

14103

發布評論請先 登錄

相關推薦

揭開xenomai雙核系統下clock機制的面紗

探討一下,CRC校驗的優勢

Stm32_Clock_Init函數如何定義

介紹一下STM32L151的clock tree

基于Stm32_Clock_Init()函數的流水燈設計

請教一下各位標準單元庫中clock buffer的設計很復雜嗎

浪潮與中橋探討:新數據時代下,存儲的挑戰與創新

企業云下的軟件定義存儲

軟件定義汽車趨勢下的供應鏈變革

Arduino IDE環境下NodeMCU引腳定義

探討下clock的基本定義(下)

探討下clock的基本定義(下)

評論