目標

本實驗活動的目標是進一步強化上一個實驗活動“使用CD4007陣列構建CMOS邏輯功能”中探討的CMOS邏輯基本原理,并獲取更多使用復雜CMOS門級電路的經驗。具體而言,您將了解如何使用CMOS傳輸門和CMOS反相器來構建傳輸門異或(XOR)和異或非邏輯功能。

背景知識

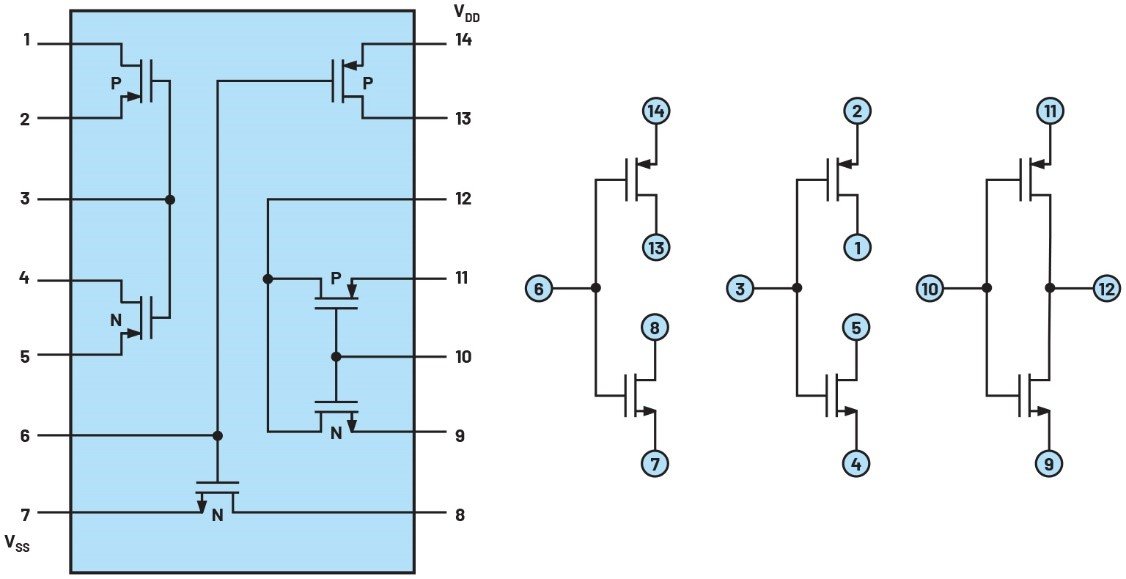

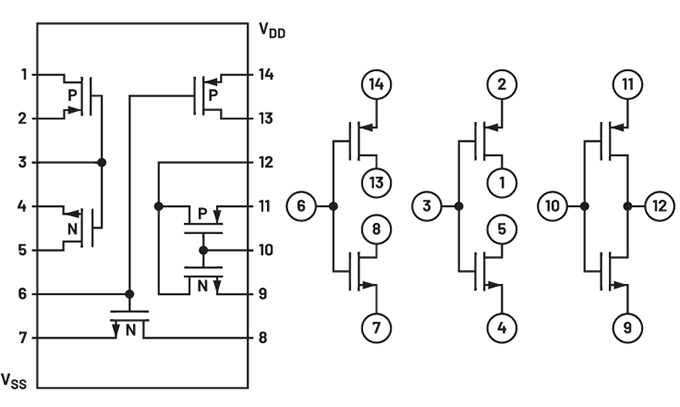

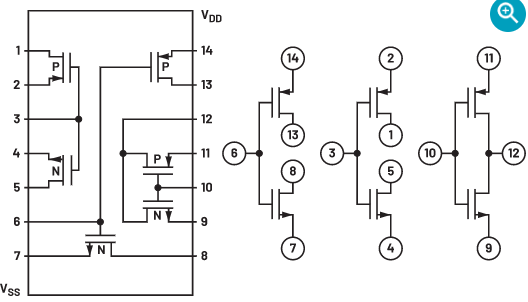

為了在本實驗活動中構建邏輯功能,需要使用ADALP2000模擬部件套件中的CD4007 CMOS陣列和分立式NMOS和PMOS晶體管(ZVN2110A NMOS和ZVP2110A PMOS)。CD4007由3對互補MOSFET組成,如圖1所示。每對共用一個柵極(引腳6、3和10)。所有PMOSFET(正電源引腳14)以及NMOSFET(地引腳7)的襯底都共用。左邊一對,NMOS源極引腳連接到NMOS襯底(引腳7),PMOS源極引腳連接到PMOS襯底(引腳14)。另外兩對均為通用型。右邊一對,NMOS的漏極引腳連接到PMOS的漏極引腳,即引腳12。

圖1.CD4007功能框圖。

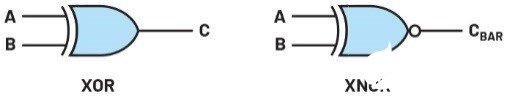

CD4007是一款多功能IC。例如,單個CD4007可用于構建三個反相器、一個反相器加上兩個傳輸門或其他復雜的邏輯功能,如NAND和NOR門。反相器和傳輸門尤其適合構建傳輸門XOR和XNOR邏輯功能。XOR和XNOR邏輯門的示意圖符號如圖2所示。

圖2.XOR和XNOR示意圖符號。

靜電放電

CD4007與許多CMOS集成電路一樣,很容易被靜電放電損壞。CD4007包括二極管,可防止其受靜電放電的影響,但如果操作不當仍可能會損壞。使用對靜電敏感的電子產品時,通常會使用防靜電墊和腕帶。然而,在家里(正規的實驗環境之外)工作時,可能沒有這些物品。避免靜電放電的一種低成本方法是在接觸IC之前先使自己接地。在操作CD4007之前,使積聚的靜電放電將有助于確保在實驗過程中不會損壞芯片。

材料

?ADALM2000主動學習模塊

?無焊試驗板

?1個CD4007(CMOS陣列)

?2個ZVN2110A NMOS晶體管

?2個ZVP2110A PMOS晶體管

說明

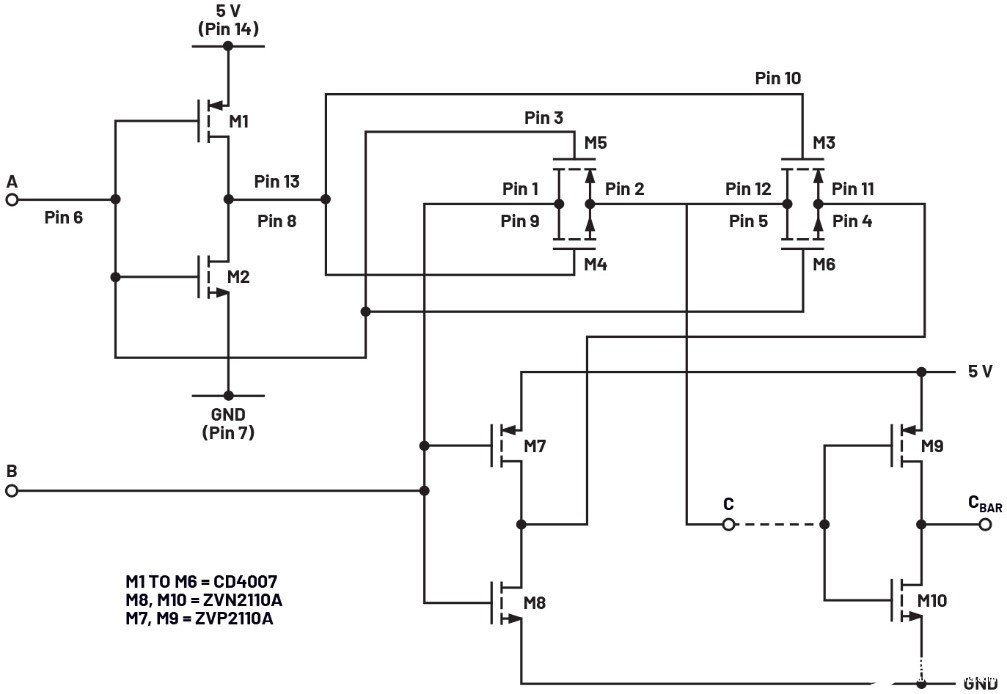

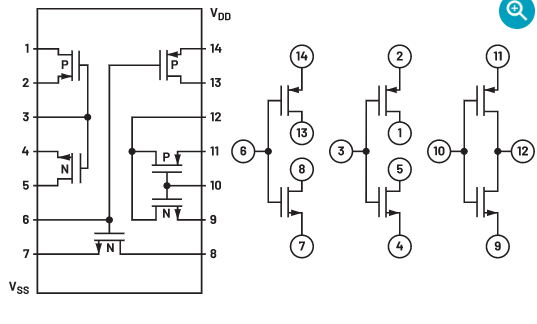

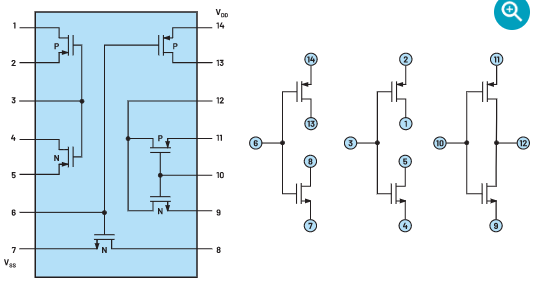

現在我們將使用單刀雙擲(SPDT)傳輸門開關和兩個CMOS反相器來構建XOR門(和XNOR),如圖3所示。兩個傳輸門協同工作以實現選擇器操作。根據A輸入的狀態,輸入B或輸入B的反相會通過節點C (XOR)輸出。另外兩個反相器M9和M10使C反相以產生CBAR (XNOR)輸出。

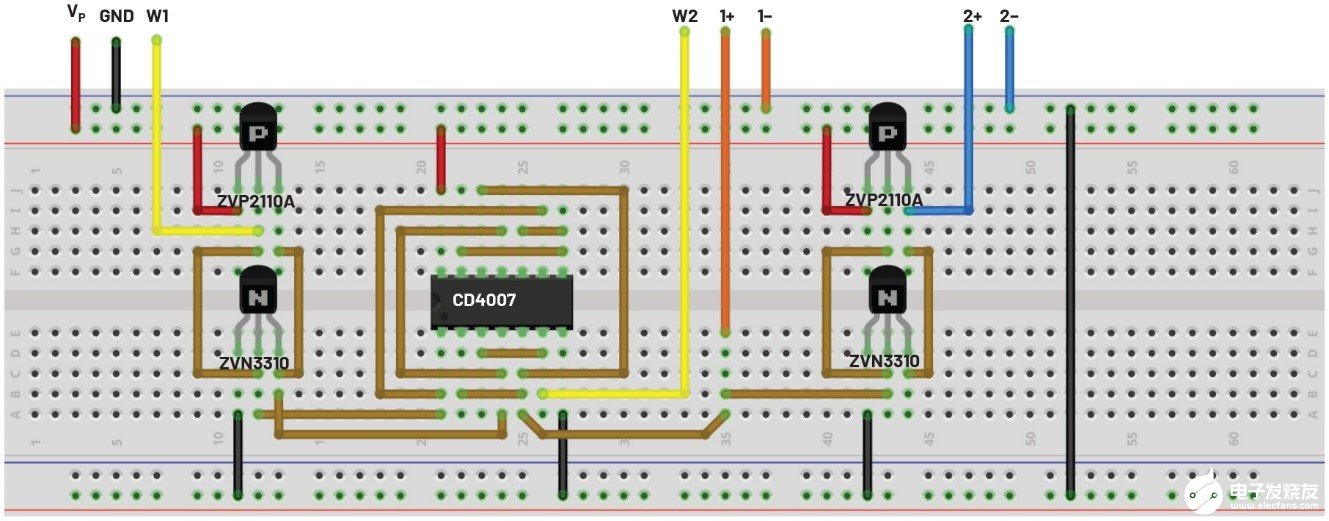

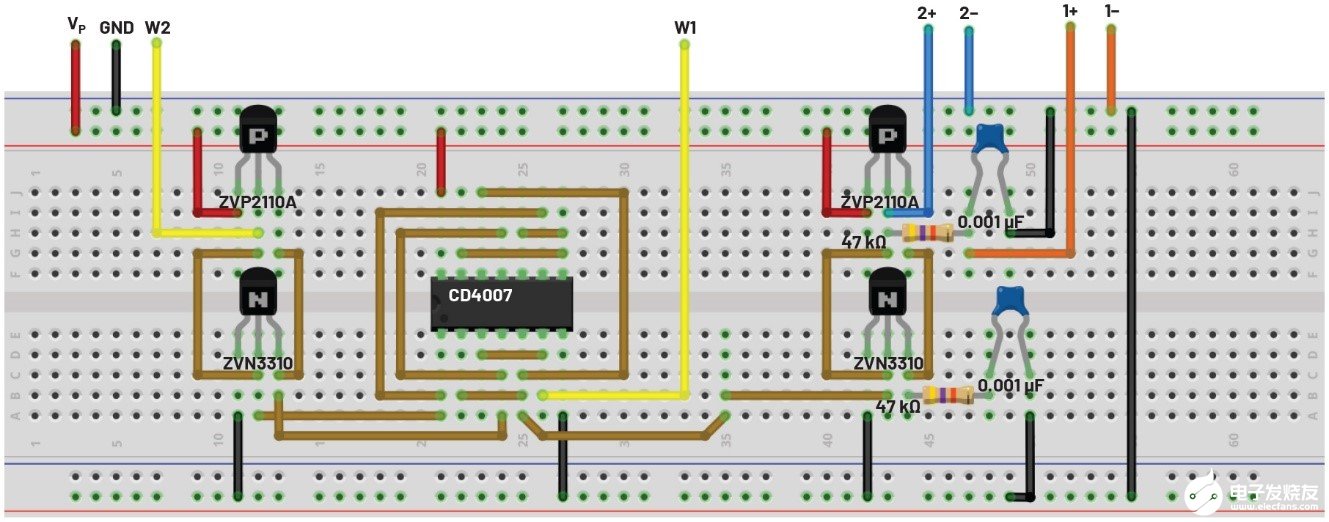

在無焊試驗板上構建圖3所示的XOR/XNOR電路。器件M1至M6采用CD4007 CMOS陣列,兩個反相器級(反相器級M7和M8,以及M9和M10)分別使用ZVN2110A NMOS和ZVP2110A PMOS。電路使用ADALM2000的固定5 V電源供電。

電路中有兩個邏輯輸入A和B。同相XOR輸出位于節點C,而該輸出的反相位于節點CBAR以形成XNOR函數。

圖3.XOR和XNOR門。

硬件設置

在實驗最初,將兩個AWG輸出配置直流源。根據需要,示波器通道將用于監控電路的輸入和輸出。固定+5 V電源用于為電路供電。在此實驗中,應禁用固定–5 V電源。

圖4.XOR和XNOR門試驗板電路。

程序步驟

將AWG1連接引腳6,作為A輸入端。將AWG2連接引腳1和9,作為B輸入端。示波器通道1連接引腳2、5和12,作為C輸出端。示波器通道2連接M9和M10的漏極引腳,作為CBAR輸出端。確保打開固定5 V電源。

首先,打開AWG控制界面并將AWG1設置為0 V直流電壓,對A施加邏輯低電平。將AWG2設置為0 V直流電壓,對B輸入段施加邏輯低電平。

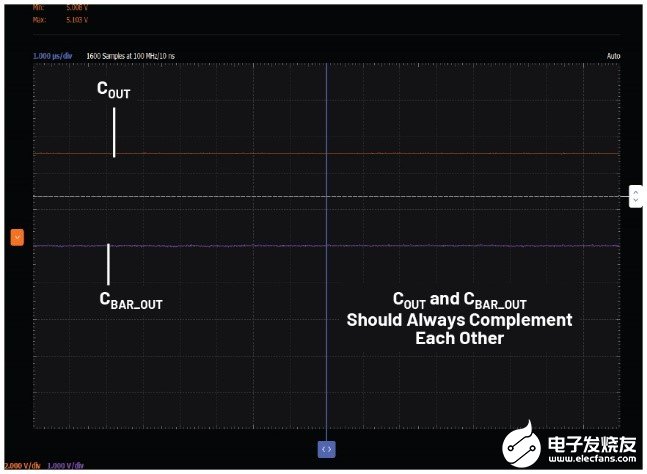

圖5.COUT和CBAR輸出。

觀察示波器通道1上柵極的輸出C。示波器界面上應顯示穩定的直流電壓。

現在將兩個AWG通道均配置為具有5 V幅度峰峰值和2.5 V偏移(0 V至5 V擺幅)的方波。將AWG1設置為1 kHz頻率,將AWG2設置為2 kHz頻率或AWG1頻率的兩倍。確保將AWG設置為同步運行。

觀察示波器界面上A和B輸入信號相應的C輸出和CBAR輸出。

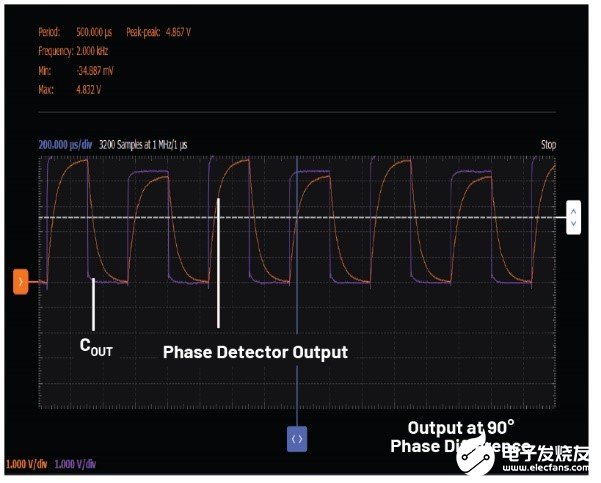

接著,將AWG2設置為與AWG1相同的1 kHz頻率,但將AWG2的相位設置為90°。觀察示波器界面上A和B輸入信號相應的C輸出和CBAR輸出。

XOR門用作鑒相器

鑒相器或相位比較器是一種邏輯電路,用于產生代表兩個邏輯信號輸入之間相位差的模擬輸出電壓信號。它是鎖相環(PLL)的中心元件。檢測信號之間的相位關系是許多系統中的重要功能模塊,如電機控制、雷達、電信、解調器和伺服機構。

方波信號的鑒相器可由XOR邏輯門組成。當比較的兩個信號完全同相時,即相位差為0°,XOR門將輸出恒定的零電平。例如,當兩個信號的相位相差10°時,在10/180或1/18周期(兩個信號值不同的極小部分周期)中,XOR門將輸出高電平。當信號相位相差180°時,即一個信號為高電平而另一個為低電平,反之亦然,此時XOR門的輸出在每個周期內都會保持高電平。

當XOR門鑒相器用于PLL系統時,它通常鎖定在相位檢測范圍中間的90°相位差附近。在90°時,XOR具有50%占空比的方波輸出,輸出頻率是輸入頻率的兩倍。方波占空比根據兩個輸入信號的相位差發生變化。XOR門的輸出通過低通濾波器產生的模擬電壓與兩個信號之間的相位差成正比。它需要對稱的方波輸入。如果一個輸入的占空比與另一個輸入的占空比略有不同,則低通濾波輸出將會偏移90°相位差時的理想中間范圍。

說明

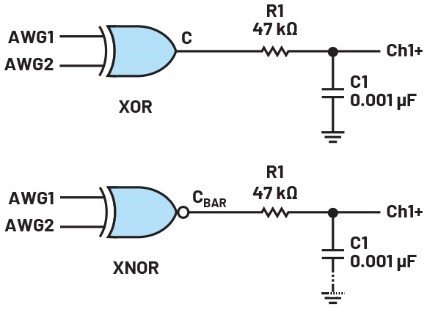

將圖6所示的RC低通濾波器添加到XOR試驗板電路中。將示波器通道1連接到RC濾波器輸出。

圖6.XOR門鑒相器。

硬件設置

將兩個AWG通道均配置為具有5 V幅度峰峰值和2.5 V偏移(0 V至5 V擺幅)的方波。將AWG1和AWG2的頻率都設置為1 kHz。同時確保從AWG1和AWG2的相位都設置為0°開始。確保將AWG設置為同步運行。

圖7.XOR門鑒相器試驗板電路。

程序步驟

將示波器通道1連接到C1的RC濾波器輸出,觀察鑒相器的濾波(DC)輸出。將示波器通道2連接到XOR門的輸出C,觀察邏輯門輸出的脈沖寬度。

圖8為Scopy波形圖示例。

圖8.XOR門鑒相器采樣輸出。

替代元件選擇

使用四個獨立NMOS和PMOS晶體管(ZVN2110A和ZVP2110A)構建的反相器對也可以由第二個CD4007 IC構成,或者可以是采用六路反相器IC的CMOS反相器,如74HC04或CD4049。CD4066四通道SPST開關也可以作為采用CD4007構建的開關的替代器件。

問題

1.對于圖3中的電路,將AWG1和AWG2設置為邏輯高電平(5 V)和低電平(0 V)值,并填入以下表格。

表1.每組輸入(A和B)的輸出值

| 輸入A | 輸入B | 輸出C | 輸出CBAR |

| 0 | 0 | ||

| 1 | 0 | ||

| 0 | 1 | ||

| 1 | 1 |

-

CMOS

+關注

關注

58文章

5710瀏覽量

235420 -

晶體管

+關注

關注

77文章

9682瀏覽量

138082

發布評論請先 登錄

相關推薦

CD4007里的group A subgroup是什么意思

CD4007.pdf

cd4007中文資料pdf

常用CD系列門電路

高速CMOS邏輯8輸入與非門cd74hct30手冊

cd4007中文資料匯總(cd4007引腳圖及功能_特性及應用電路)

CD4007UB-MIL CMOS 雙路輔助對反向器

CMoS雙互補對加型逆變器CD4007UB TYPES 數據表

使用CD4007陣列構建CMOS邏輯功能

使用CD4007陣列構建CMOS邏輯功能

評論